Multiplier calculating modular multiplicatin of large numbers

A large number analog multiplication and multiplier technology, which is applied in the field of large number analog multiplication calculation multipliers, can solve the problems of increased power consumption, high circuit power consumption, and large circuit area, achieving less increase in circuit area and low circuit power consumption , The effect of small circuit area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

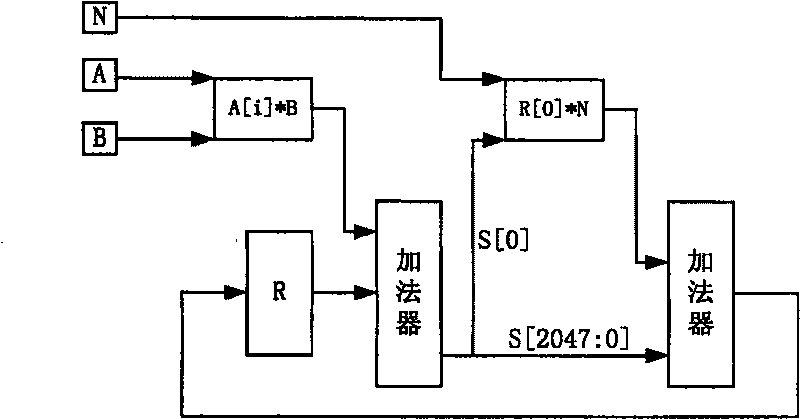

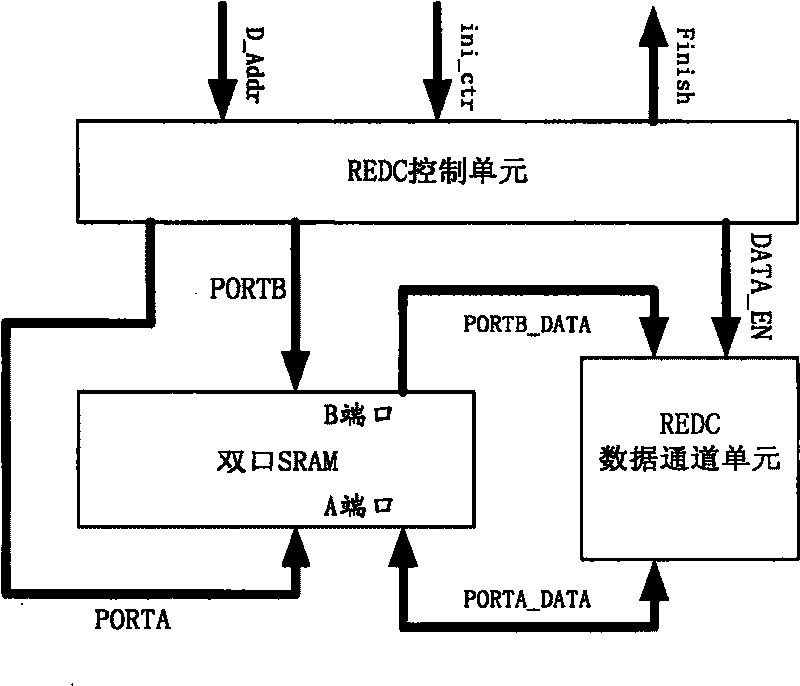

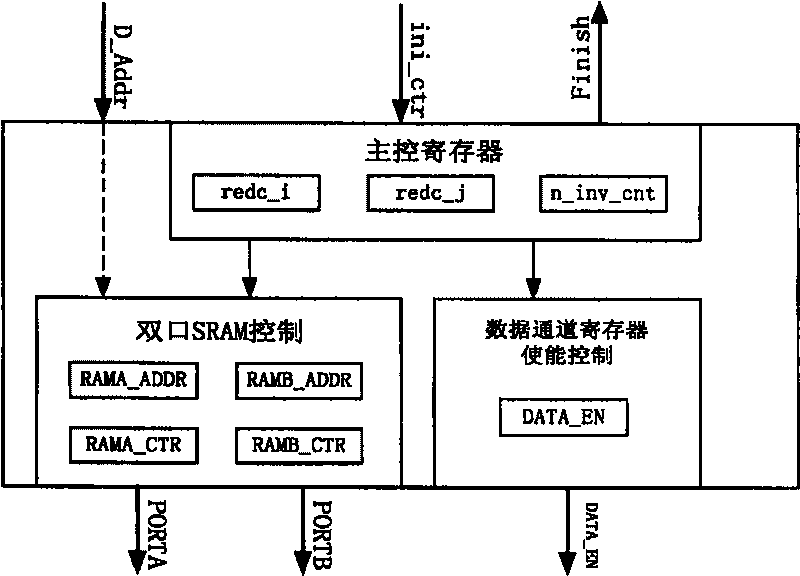

[0043] The present invention is a kind of optimized hardware realization scheme of Montgomery algorithm, compared with the original technical scheme, all calculations of the original technical scheme are realized by an adder, and the technical scheme of the present invention is realized by a multiplier; Registers store operands and intermediate quantities in operations.

[0044] In order to carry out the modular multiplication calculation of large numbers more conveniently and reduce the use of hardware registers and hardware adders, for the Montgomery algorithm: when integers A, B and N are given, calculate R=REDC(A, B, N, n), Satisfy the condition R*2 n =A*B mod N; The present invention has been improved as follows: make n=nn*Y, wherein nn is the binary bit number of N taking Y bits as a unit; Modular inverse N_INV[Y-1:0] satisfies the following conditions: N_INV[Y-1:0]*N[Y-1:0] mod 2 Y =-1. Y can be 1-128. When Y is equal to 1, it is equivalent to the original algorithm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More