Semiconductor integrated circuit for wireless communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

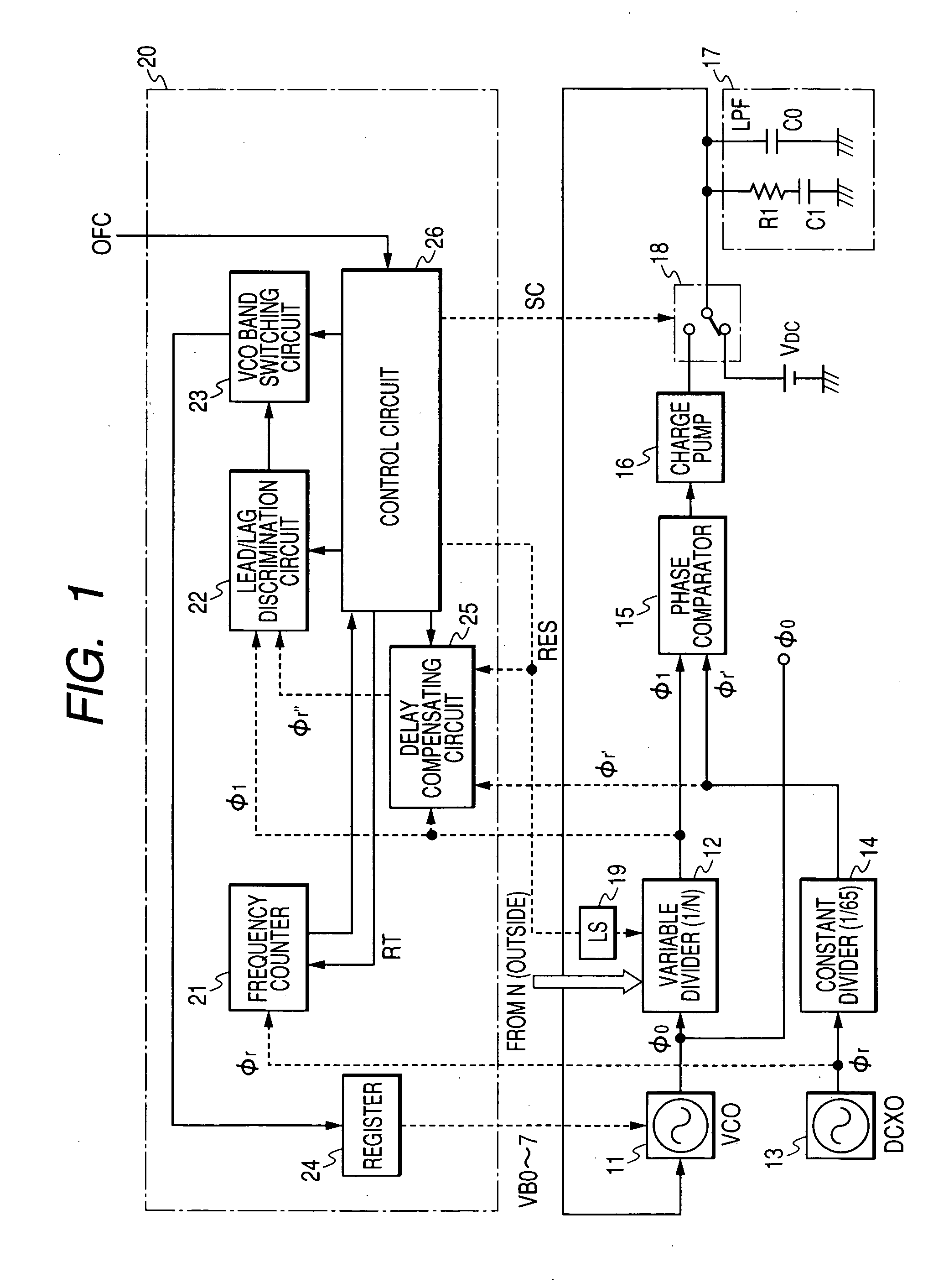

[0068] the delay compensating circuit 25 is shown in FIG. 7. Prior to the description of the configuration and operation of the delay compensating circuit 25 shown in FIG. 7, the reason why the delay compensating circuit 25 is provided, will be explained using a timing chart shown in FIG. 6.

[0069] In the auto band selection circuit employed in the embodiment, in which the phase lead / lag discrimination circuit 22 determines whether the rising edge of the output pulse φ1 of the variable divider 12 leads the rising edge of the output pulse φr′ of the constant divider 14, the rising edge of the output pulse φr′ of the constant divider 14 and the rising edge of the output pulse φ1 of the variable divider 12 coincide with each other upon resetting by the reset signal RES as shown in FIG. 6(A) where no delay occurs in the reset operation of the variable divider 12. It is therefore possible to accurately determine whether the phase processed after 2.5 μs leads or lag.

[0070] On the other ha...

second embodiment

[0079] a delay compensating circuit 25 is shown in FIG. 9. In FIG. 9, the same circuits as those in the delay compensating circuit 25 shown in FIG. 7 are given the same reference numerals and their dual explanations are therefore omitted.

[0080] The delay compensating circuit 25 shown in FIG. 9 is configured in such a manner that a signal φ1 divided by a variable divider 12 and a signal / φr obtained by inverting a pre-division oscillation signal φr of a DCXO 13 by an inverter 27 are selectively inputtable to a signal delay circuit 251 by a switch 252 in place of the reset signal RES and the signal φr′ divided by the constant divider 14, respectively. The delay compensating circuit 25 is provided with a selector switch 256 for selecting either the oscillation signal φr outputted from the DCXO 13 or a signal / φr′ delayed by the signal delay circuit 251 and supplying it to an auto band selection circuit 20. The auto band selection circuit 20 is configured so as to generate a reset signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More