Method for manufacturing semiconductor device and semiconductor device

A device manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as rewiring damage, side damage, substrate side cut surface exposure, etc., to prevent damage , to ensure the effect of dimensional accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

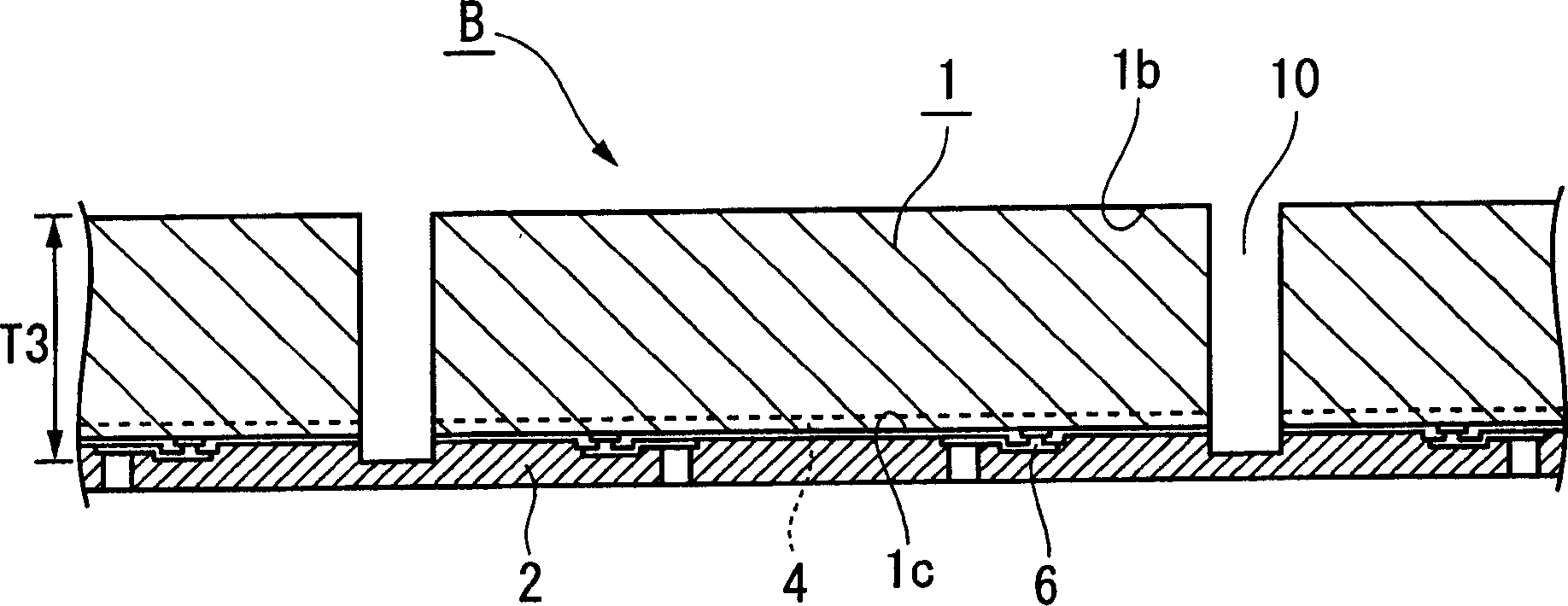

[0073] A semiconductor device B and a manufacturing method thereof according to a first embodiment of the present invention will be described below with reference to the drawings. The semiconductor device B described in this embodiment is mounted and used in devices such as mobile terminal equipment, particularly, in connection with processing wafer-level rewiring and WL-CSP of resin moldings.

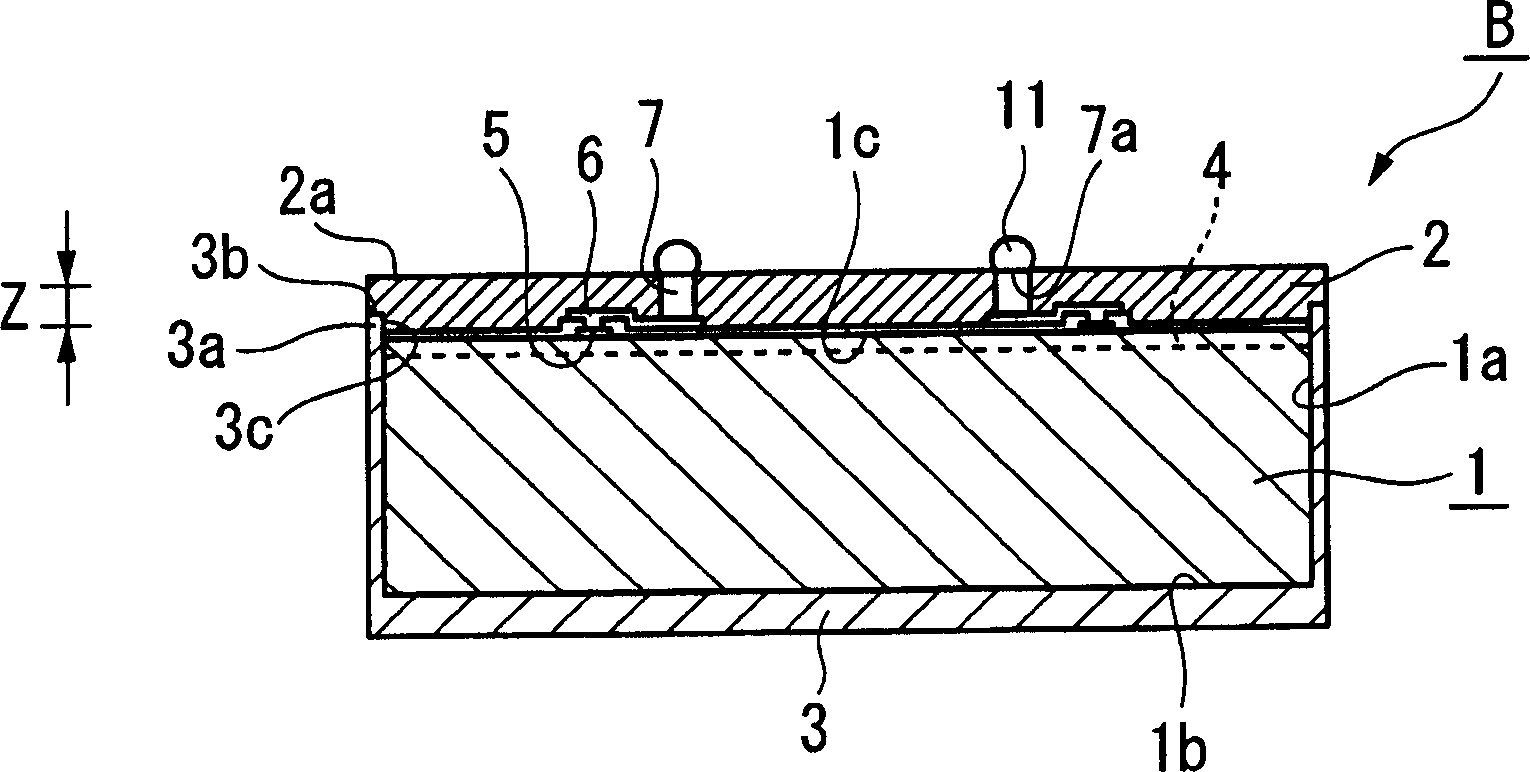

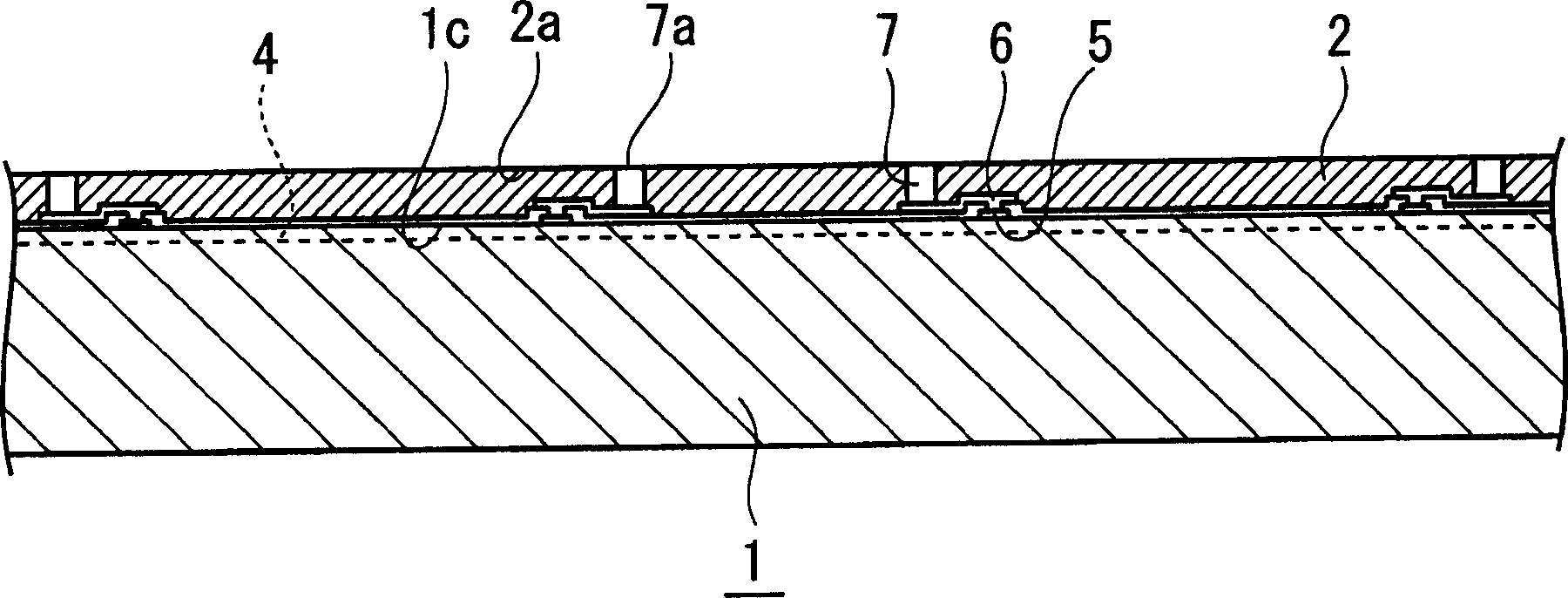

[0074] like figure 1 As shown, a semiconductor device B according to the present invention includes: a substrate 1 (wafer after dicing), which is laminated and has an integrated circuit 4 on a main surface 1c; 6; columnar electrode terminals (metal posts) 7 formed on the rewiring 6; first resin layer 2 having a thickness from the main surface 1c of the substrate 1 to the upper surface 7a of the electrode terminals 7 and sealing the main surface 1c of the substrate 1; bumps Electrodes 11 (bumps) are mounted on the upper surface 7 a of the electrode terminal 7 exposed on the surface 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More