Wafer for evaluation, evaluation method and method of manufacturing semiconductor device

An evaluation method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical components, etc. Effect of small shot distribution deviations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. In the following embodiments, although various limitations are made on constituent elements, types, combinations, shapes, relative arrangements, etc., these are merely examples, and the present invention is not limited thereto.

[0053] The wafer shown in this example is not a semiconductor wafer actually used for manufacturing a semiconductor chip, but an evaluation wafer for an ion implantation test used to evaluate the distribution deviation of the ion implantation amount in the main surface of the semiconductor wafer. In the present embodiment, the ion implantation to be evaluated is impurity implantation for threshold voltage control of transistors, which is hereinafter abbreviated as "channel doping".

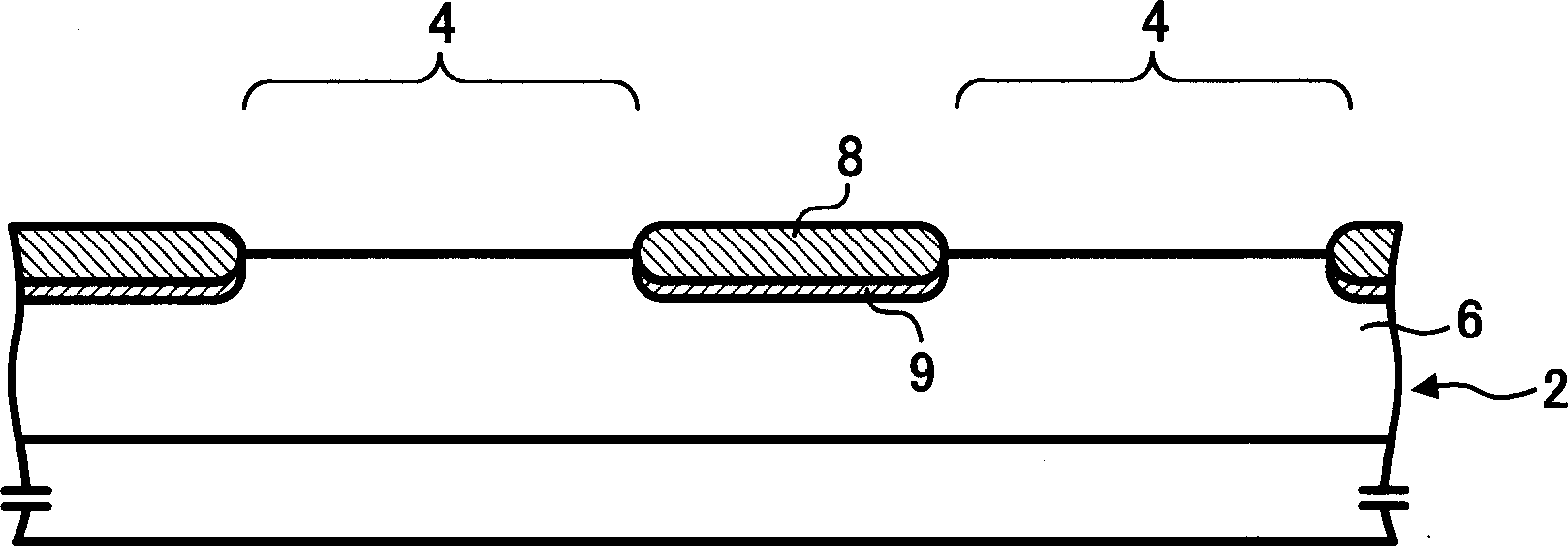

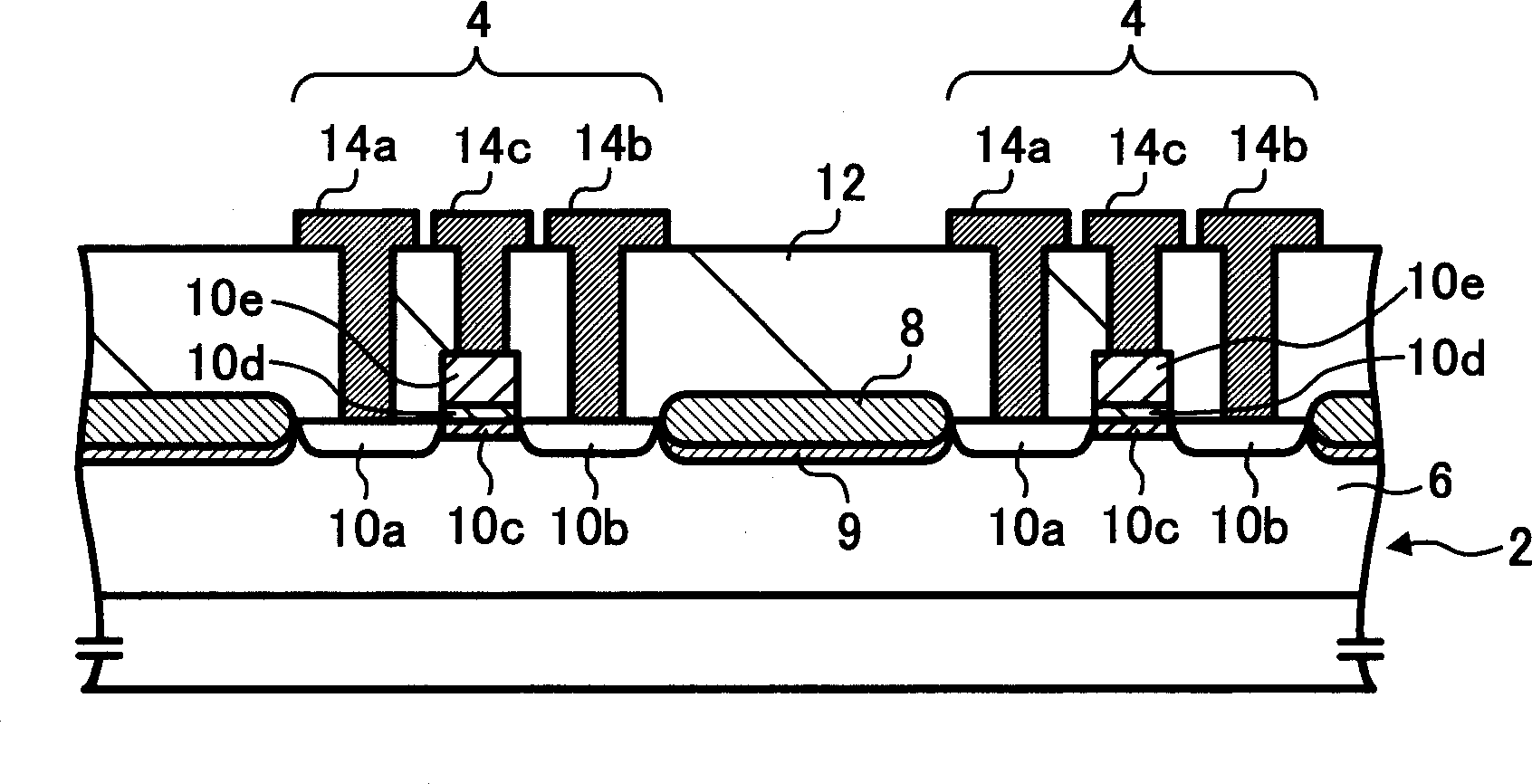

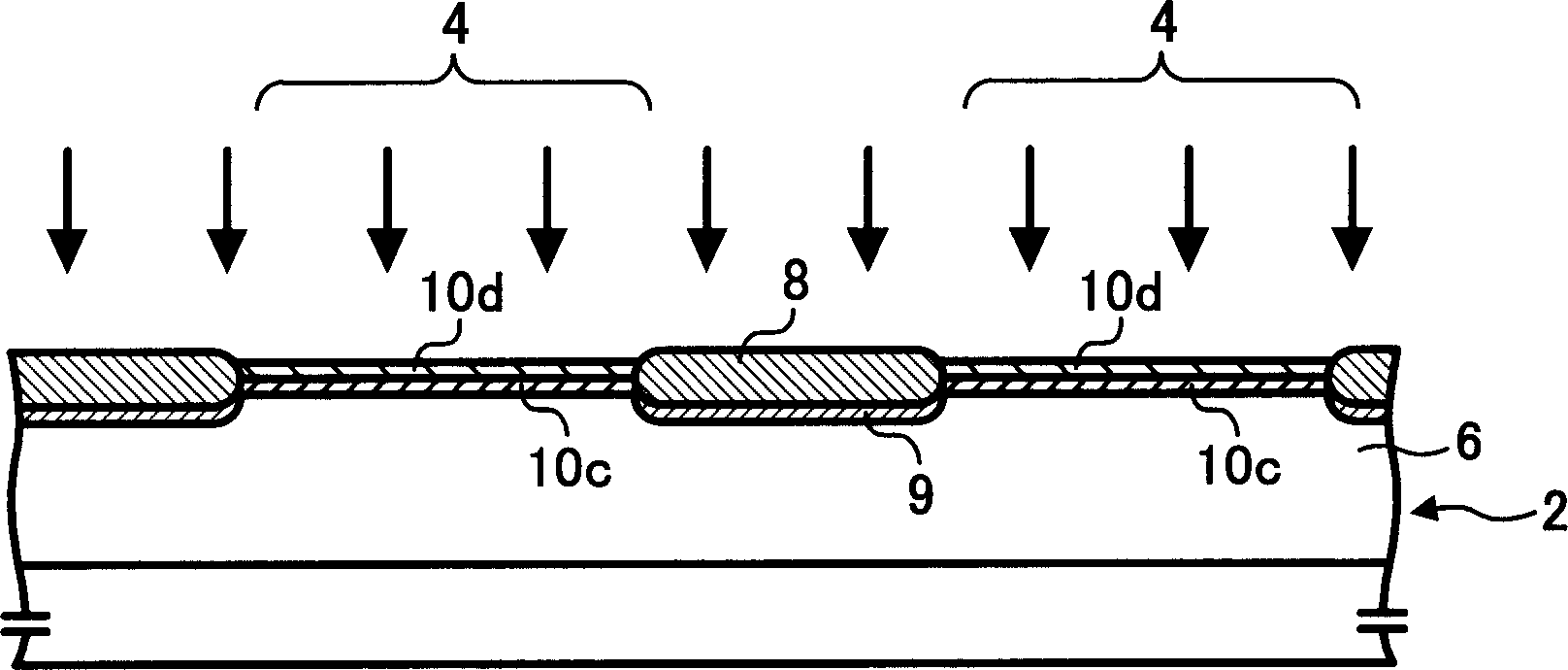

[0054] figure 1 It is a cross-sectional view for explaining an example of a wafer for evaluation.

[0055] On the entire main surface of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More