High-speed CCD camera data synthesizing system

A data synthesis and camera technology, which is applied to measuring devices, signal generators with multiple pick-up devices, instruments, etc., can solve problems such as wasting system resources, reduce system volume, reduce pixel output rate, and save system cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

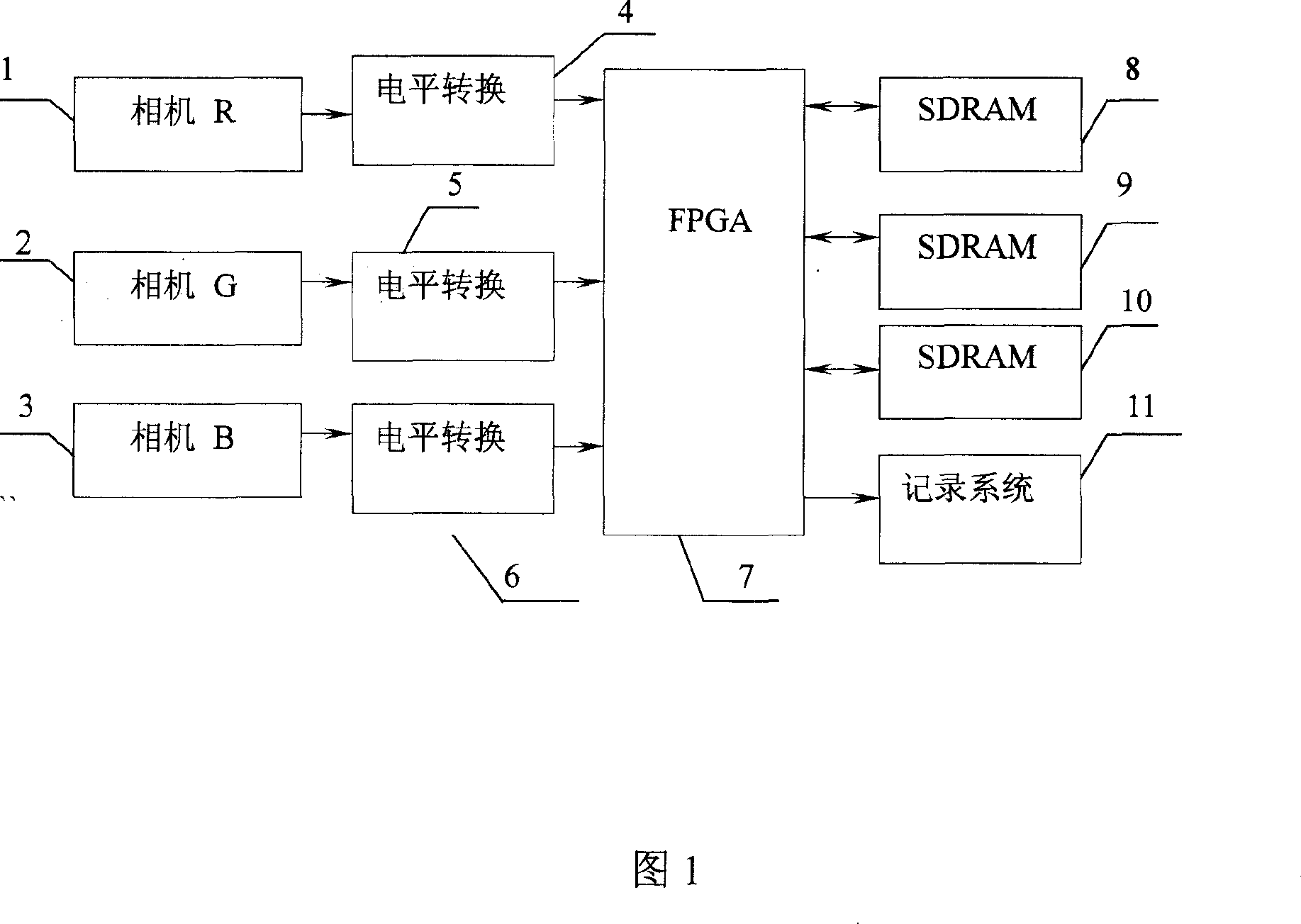

[0008] As shown in Figure 1, the present invention comprises three-way parallel high-speed CCD camera R (1), camera G (2) and camera B (3), three-way interface level conversion chip (4,5,6), FPGA (7 ), a three-way cache unit SDRAM (8, 9, 10) and a recording system (11).

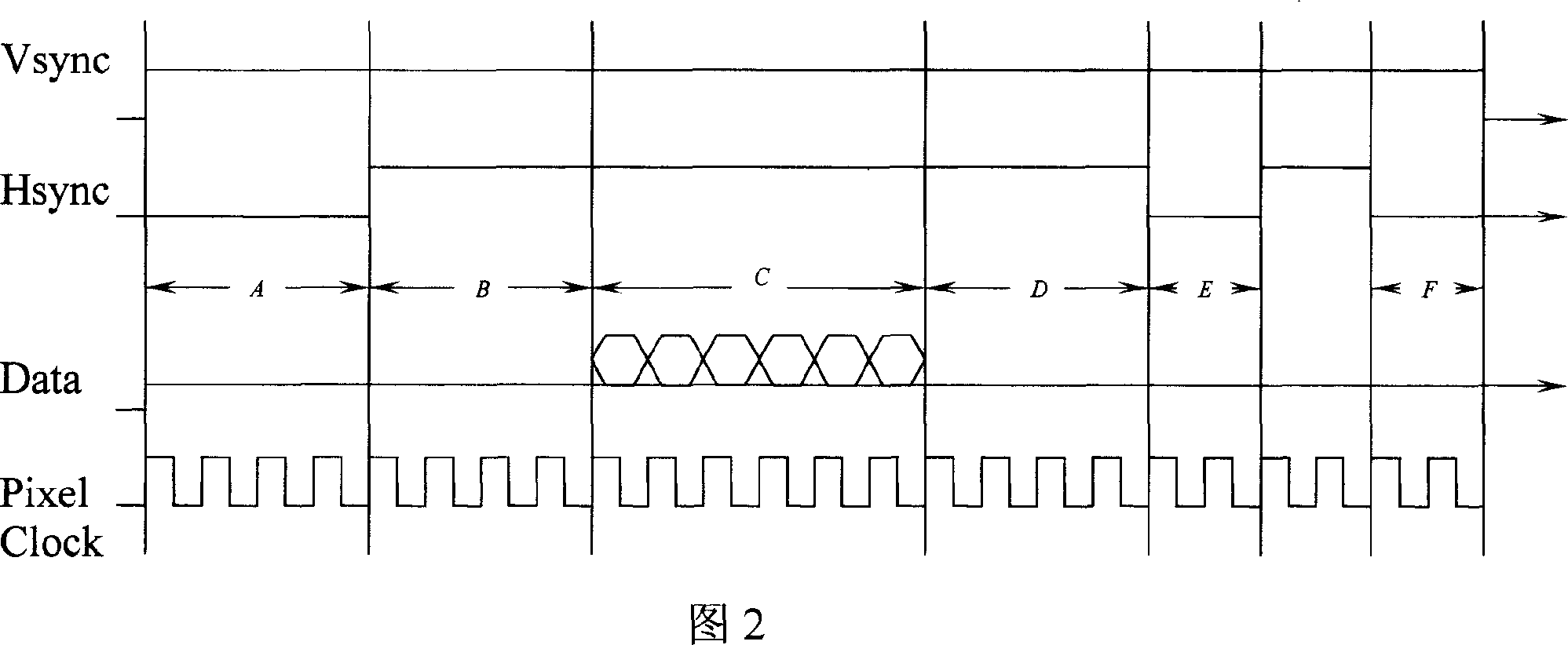

[0009] When the three CCD cameras start to work, the CCD image data is sequentially read in through the external synchronous clock and line and field clock signals. Since the CCD camera data interface is an RS422 signal, it must be converted into a TTL signal by a level conversion chip and written into the FPGA. Considering that the initial states of the three cameras cannot be exactly the same, first write the data of the three cameras into the three FIFOs in the FPGA respectively, and use the read enable logic control of the three FIFOs by the FPGA to realize the synchronous readout of the data of the three FIFOs. Then, the three-camera data synchronized by the FIFO is constructed in the FPGA internal SDRA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More