Method for manufacturing cmos image sensor

An image sensor and pattern technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as threshold voltage fluctuations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

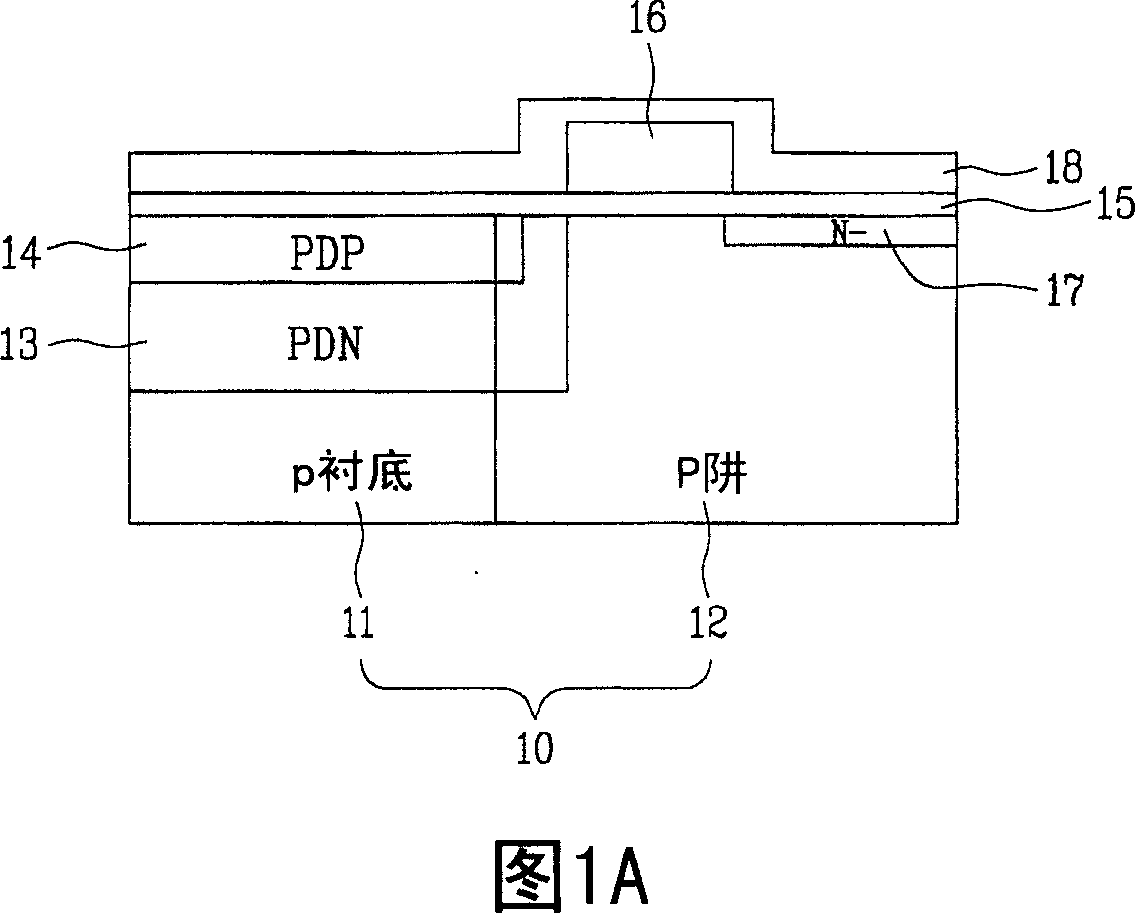

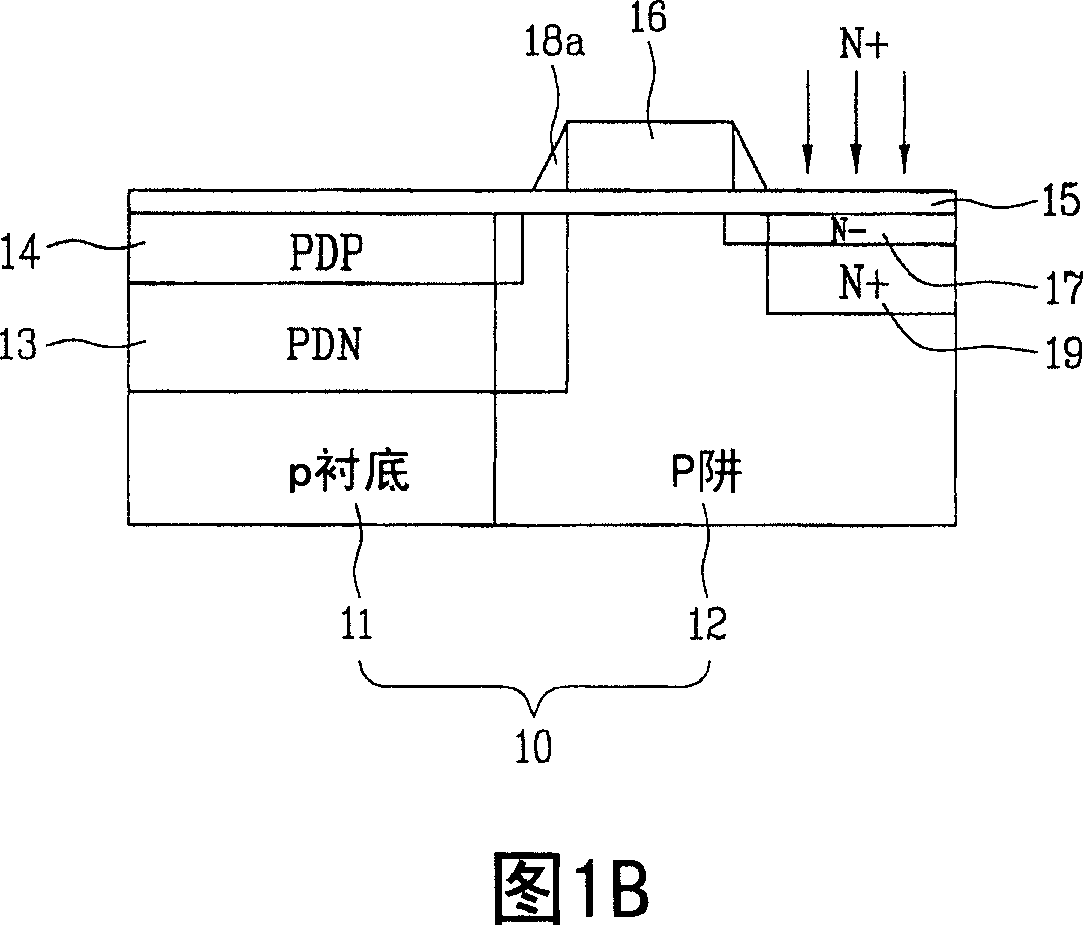

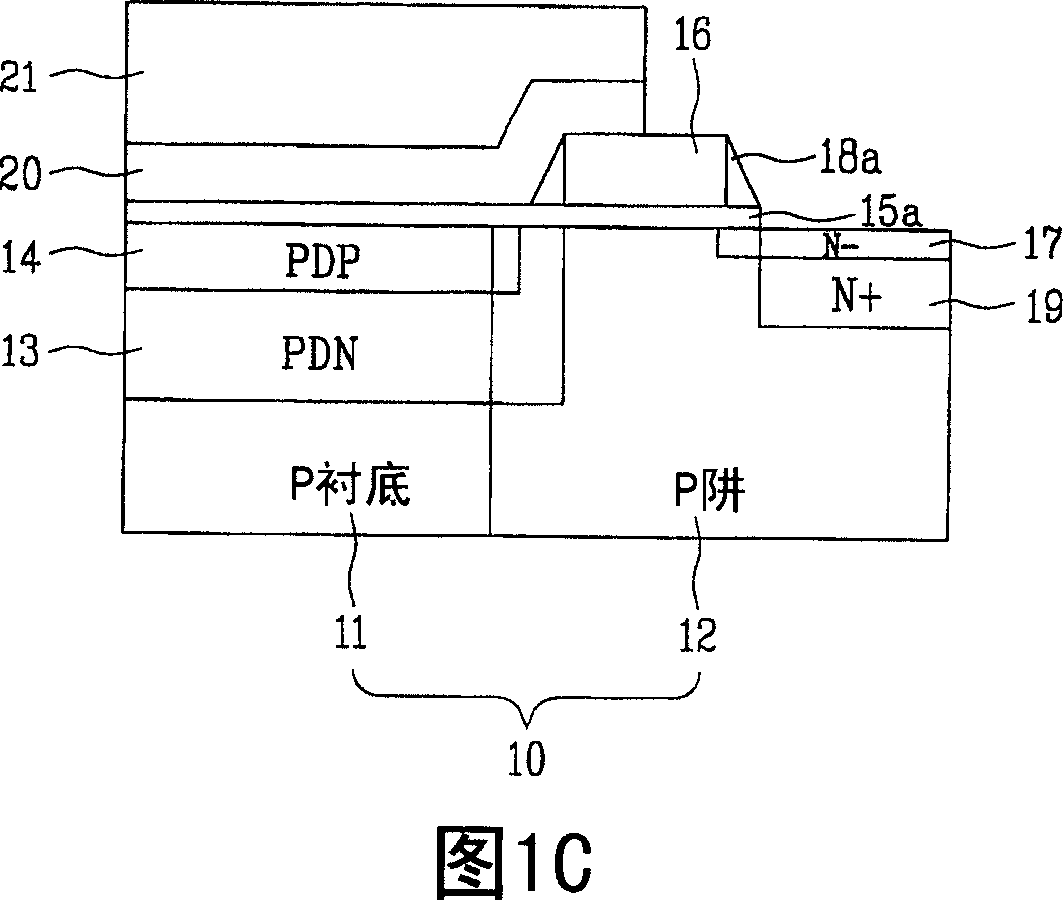

[0034] Preferred embodiments of the invention will be described in detail hereinafter, examples of which are illustrated in the accompanying drawings.

[0035] 2A to 2D are cross-sectional views illustrating a manufacturing method of manufacturing a CIS according to the present invention.

[0036] Referring to FIG. 2A, an STI (not shown) is formed on a semiconductor substrate 100 formed of an epitaxial layer. By forming the STI, the device isolation region is separated from the active region.

[0037] Subsequently, P-type impurities are implanted into the active region portion to form the P well 102 , wherein the active region portion belongs to the portion of the semiconductor substrate 100 other than the STI region. The active region portion is defined in a portion of the semiconductor substrate 100 other than the portion where the PD is to be formed. Here, other regions where the P well 102 is not formed are defined as the P subsubstrate 101 .

[0038] Subsequently, an o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More