Test method for liquid crystal display panel

A liquid crystal display and panel technology, applied in static indicators, electronic circuit testing, instruments, etc., can solve problems such as waste, unknowability, and reduced output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

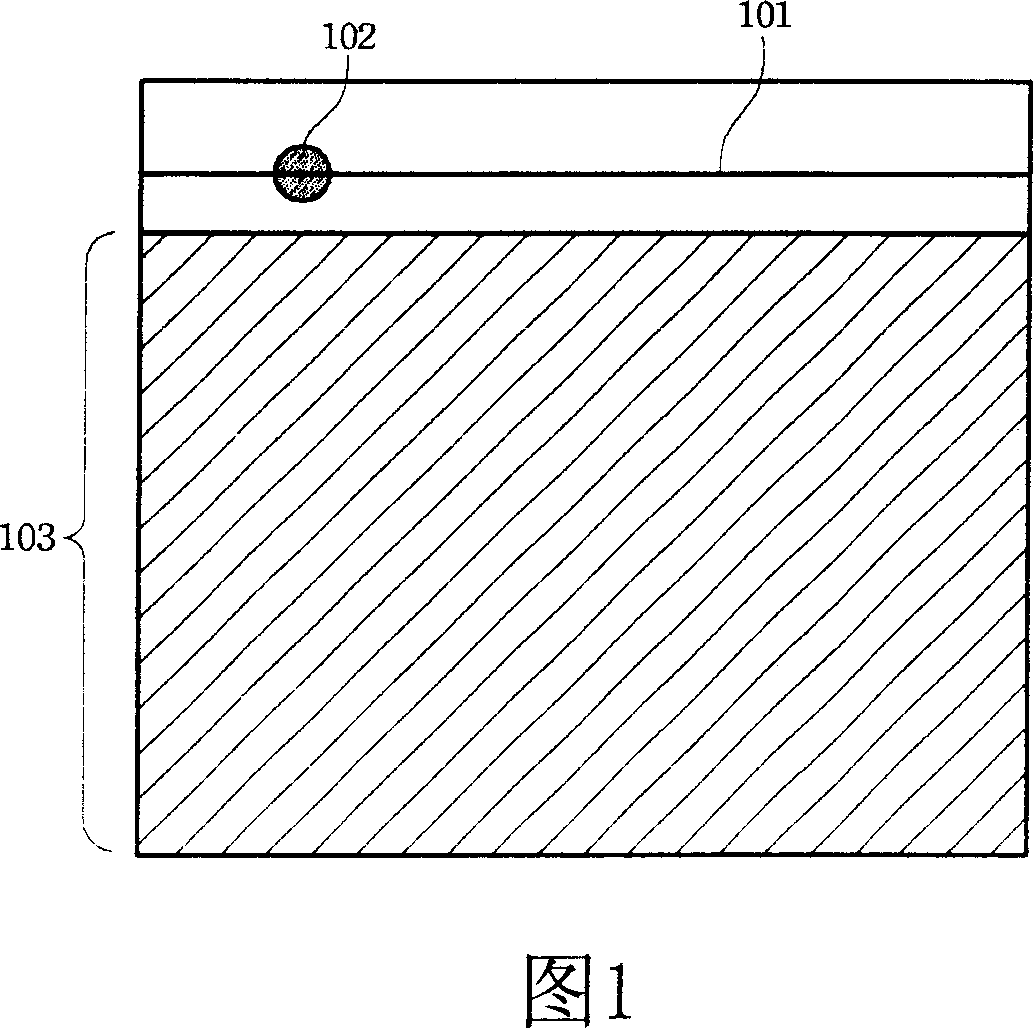

[0055] The invention provides a testing method of a liquid crystal display panel, which is used for simultaneously testing the thin film transistors on multiple gate lines when the grid driving circuit is integrated on the liquid crystal display panel. The first embodiment of the present invention is to electrically connect the positive phase timing input end, the negative phase timing input end and the start signal input end of the gate driver of the selected area on the liquid crystal display panel to the corresponding test pads respectively. After the gate driver in the selected area turns on the gate lines, all the pixels represented by the TFTs in the selected area can be tested.

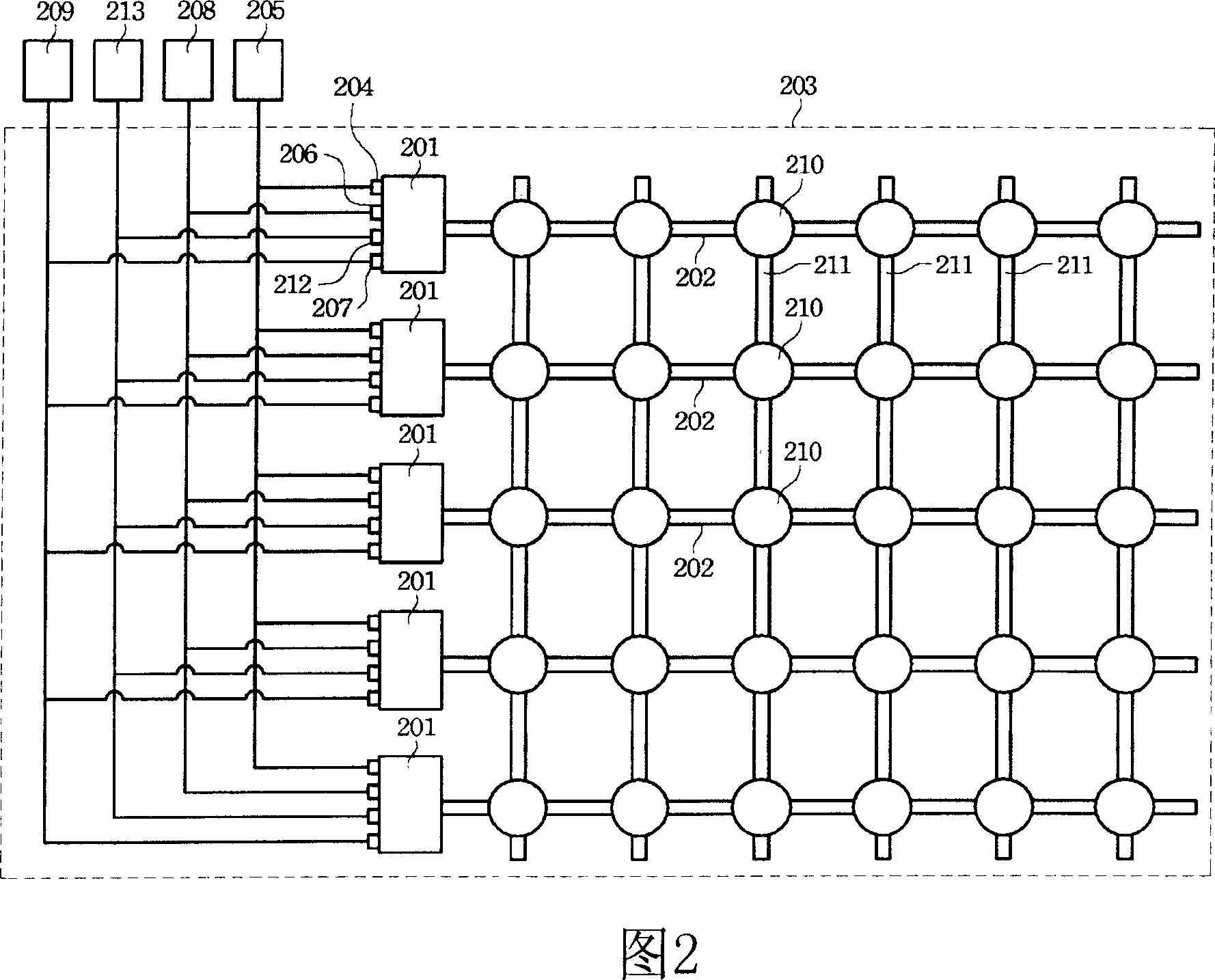

[0056] Please refer to FIG. 2 , which shows a schematic diagram of a selected area of a liquid crystal display panel according to a first embodiment of the present invention. The gate driver 201 and the gate lines 202 are integrated on the panel glass 203 . The positive-phase timing input en...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More