Method for creating a design verification test bench

a design verification and test bench technology, applied in the field of digital design verification, can solve the problem that the atpg techniques used in manufacturing test are not directly suitable for verification testing, and achieve the effect of large design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

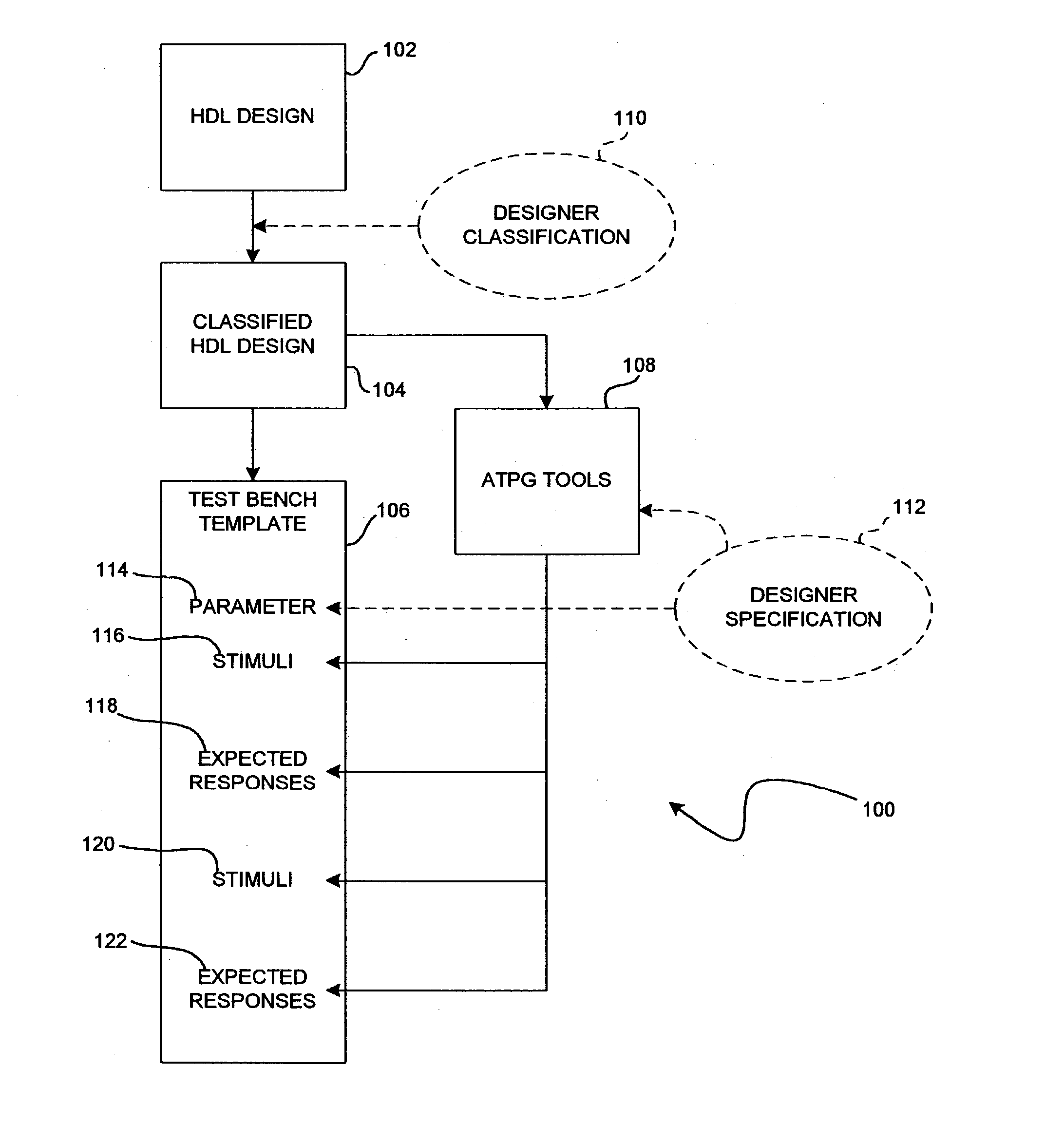

[0014] FIG. 1 is a block diagram that illustrates a test bench creation system according to one aspect of the present invention. The system is designated generally by the reference numeral 100 and includes an HDL circuit design 102, a classified HDL circuit design 104, a test bench HDL design template 106, ATPG-like tools 108, designer interactions 110, 112, designer-selected parameters 114, and various ATPG-generated test stimuli and expected responses 116-122.

[0015] In general, a test bench creation process according to the present invention begins with a completed HDL circuit design 102. If the designer has not already done so, he now classifies 110 the various parts of the design according to circuit type, e.g., finite state machines (FSMs), data paths, counters, and shift registers. The classifications are typically entered directly into the HDL circuit design using special comment lines. The result of the designer intervention 110 is a classified HDL circuit design 104.

[0016] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More