Nonlithographic method to produce self-aligned mask, articles produced by same and compositions for same

a non-lithographic method and mask technology, applied in the direction of circuit masks, instruments, photomechanical equipment, etc., can solve the problems of reducing the effective dielectric constant of typical procedures used to generate masks by lithographic or other means, so as to achieve simple and robust effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

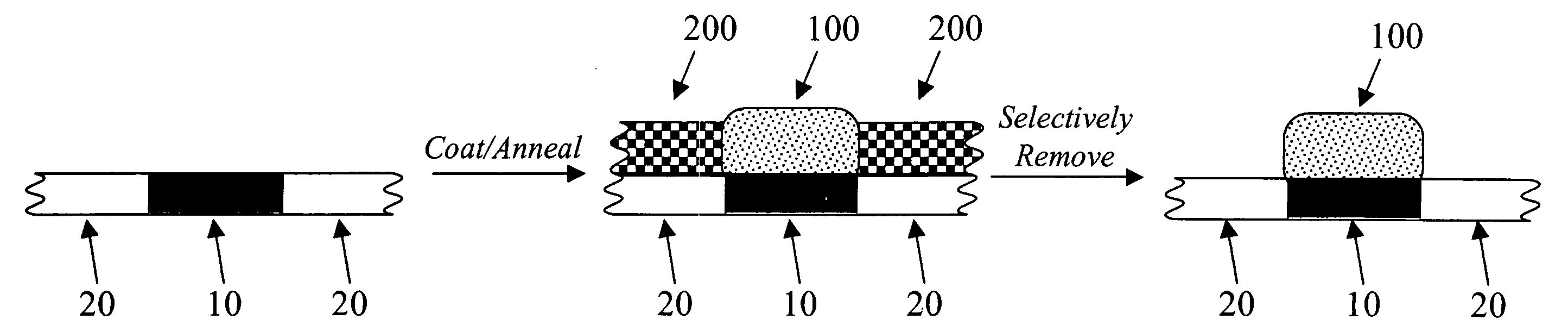

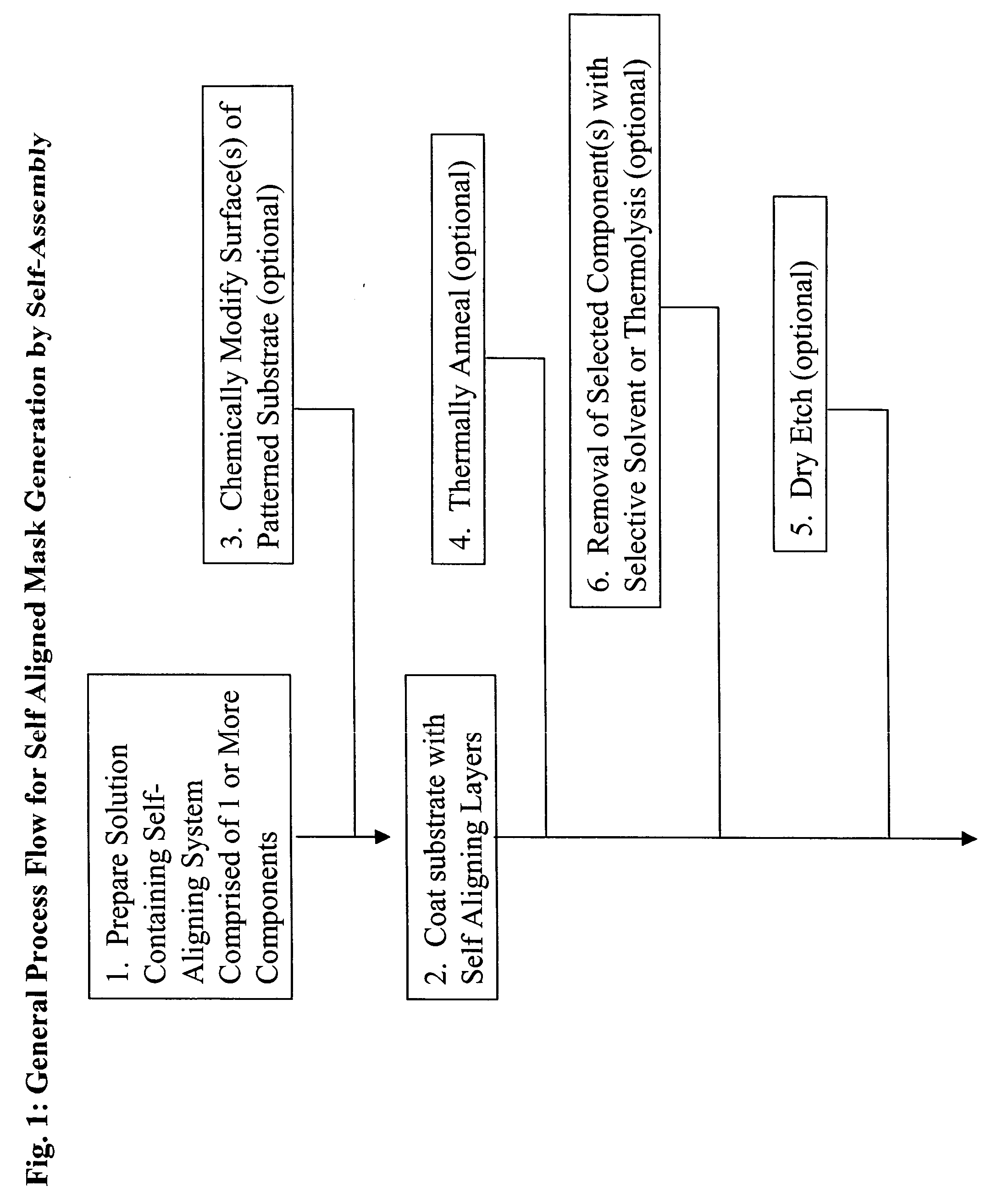

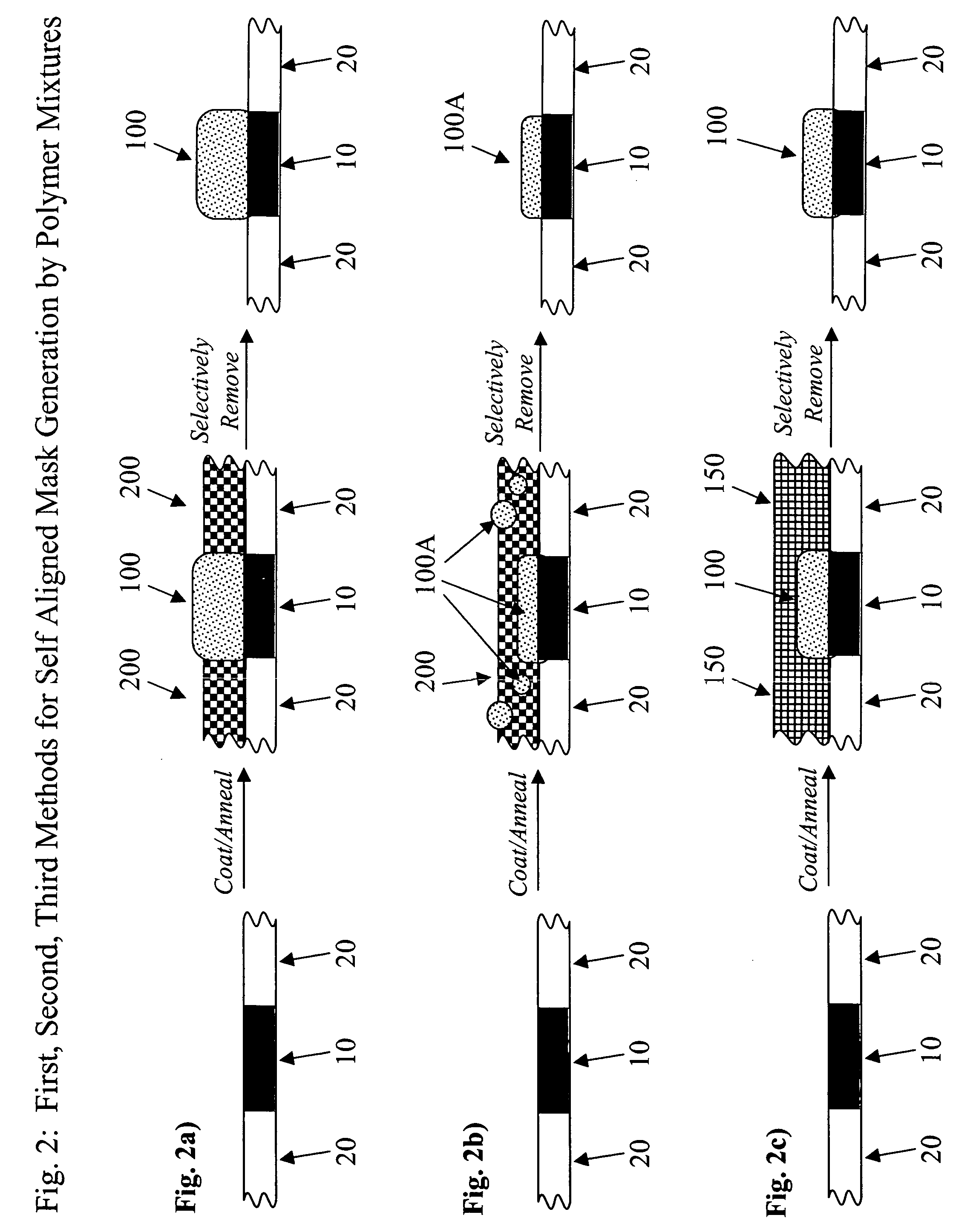

[0033] In accordance with the invention, a patterned substrate containing structures having two or more distinct components is processed by a route whereby layers can be applied to selected component surfaces. This layer can be generated by a number of self-assembly approaches described below and can be used as a mask layer for subsequent treatment or material deposition onto the intended component surfaces. These structures can be sacrificial and, in general, do not remain in the final structure. The use of the masks for the generation of self assembled barrier layers can proceed by a number of routes including: blanket deposition followed by lift-off, blanket deposition followed by chemical mechanical polishing (CMP), and enhancement of selective electrochemical and electroless metal deposition processes. It will be clear to one skilled in the art that the application of a self-aligned layer by any of the approaches described below can be used as a process to generate a selective ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length scales | aaaaa | aaaaa |

| dielectric constants | aaaaa | aaaaa |

| composition | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More