Dual-scaler architecture for reducing video processing requirements

a video processor and architecture technology, applied in the field of integrated circuits, can solve the problems of becoming increasingly difficult to utilize hardware adapted for processing sdtv video signals to process hdtv video signals, and achieve the effects of reducing the manufacturing cost of video processor ic components, reducing the bandwidth of high definition signals, and reducing the processing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

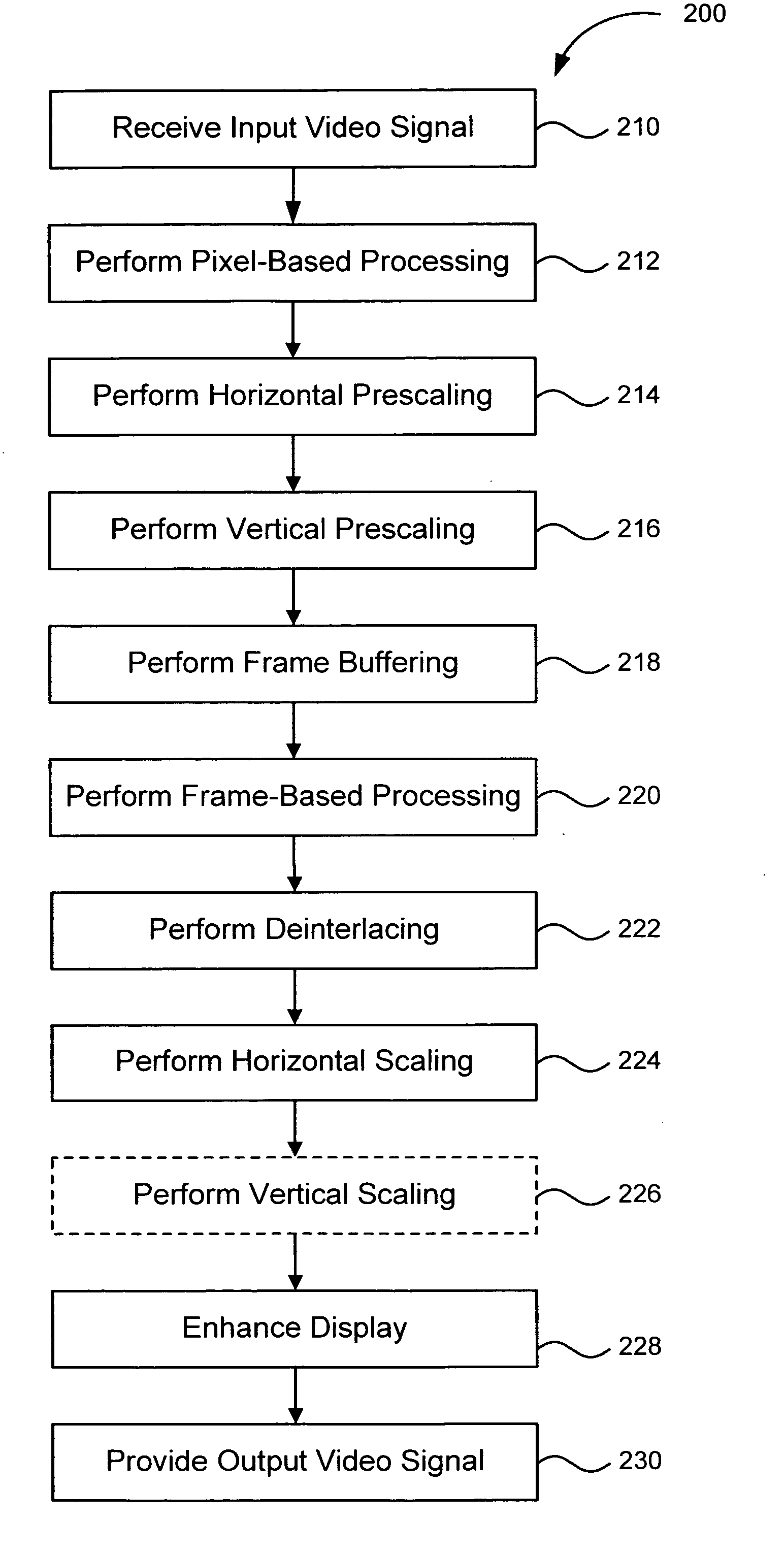

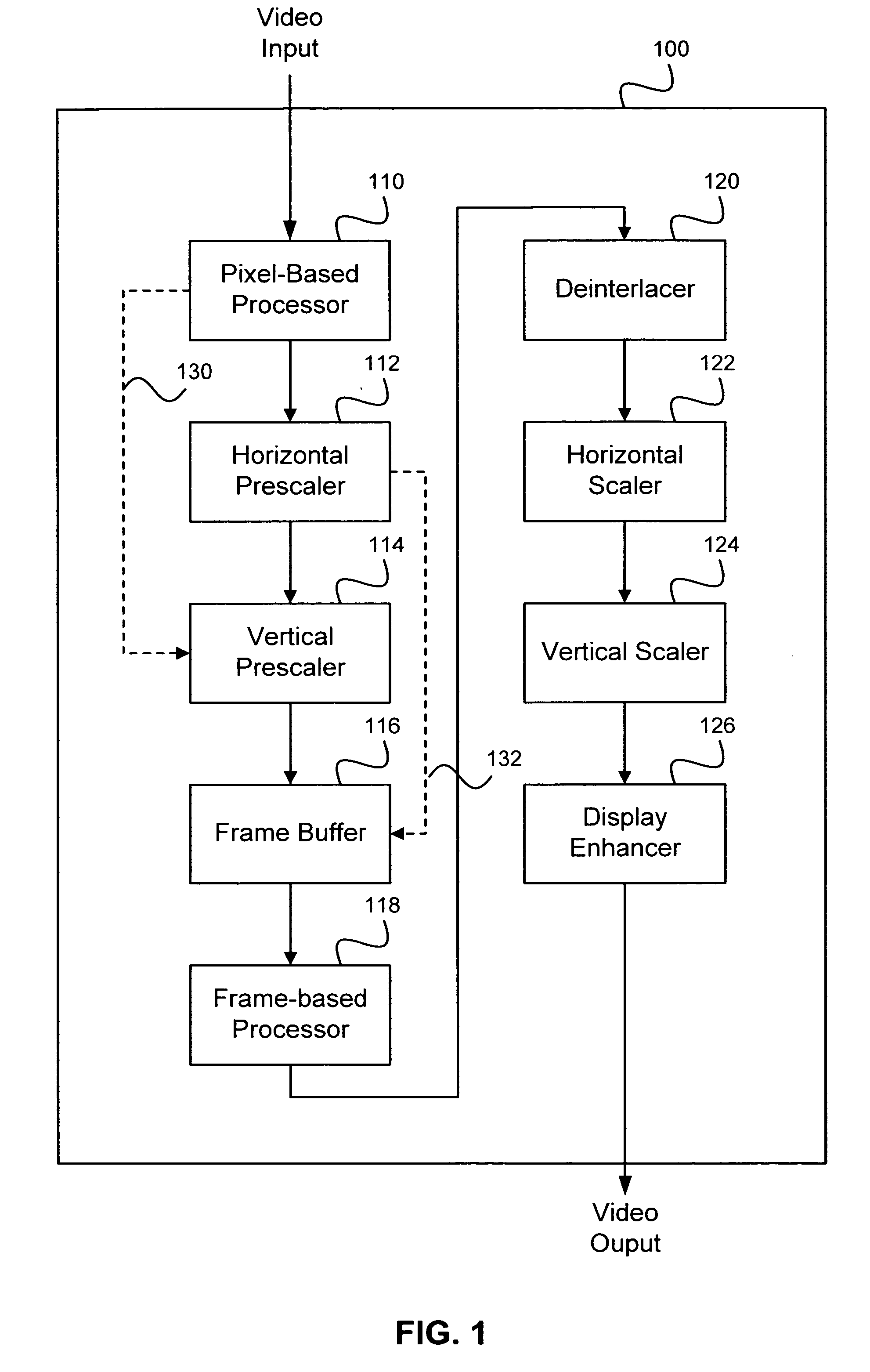

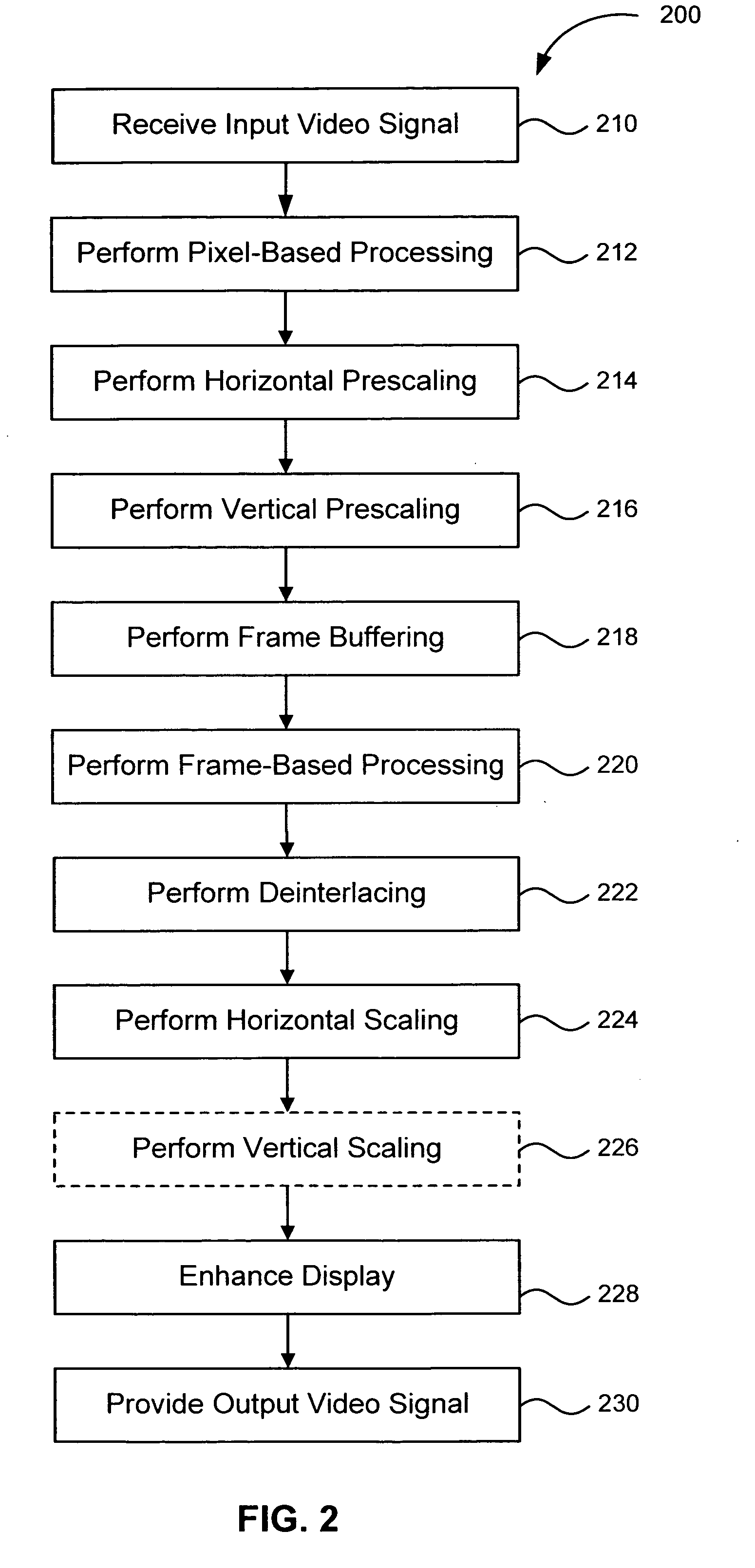

[0019] According to the present invention, techniques related to integrated circuits (ICs), and more particularly to video processor ICs, are provided. More particularly, the present invention relates to an architecture for a video processor IC. Merely by way of example, the invention has been applied to a dual-scaler architecture adapted to reduce the workload of a video processor IC receiving high definition video signals. But it would be recognized that the method and apparatus can be applied to both interlaced and progressive video signals and that the invention has a much broader range of applicability.

[0020] As discussed above, the use of video processing ICs adapted to process SDTV video signals for processing of HDTV video signals presents a number of challenges. For instance, an exemplary deinterlacing algorithm included in a video processing IC utilized to process standard interlaced SDTV signals at a pixel rate of 13.5 MHz operates at a clock rate of 50 MHz for signal pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More