Nonvolatile semiconductor storage device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

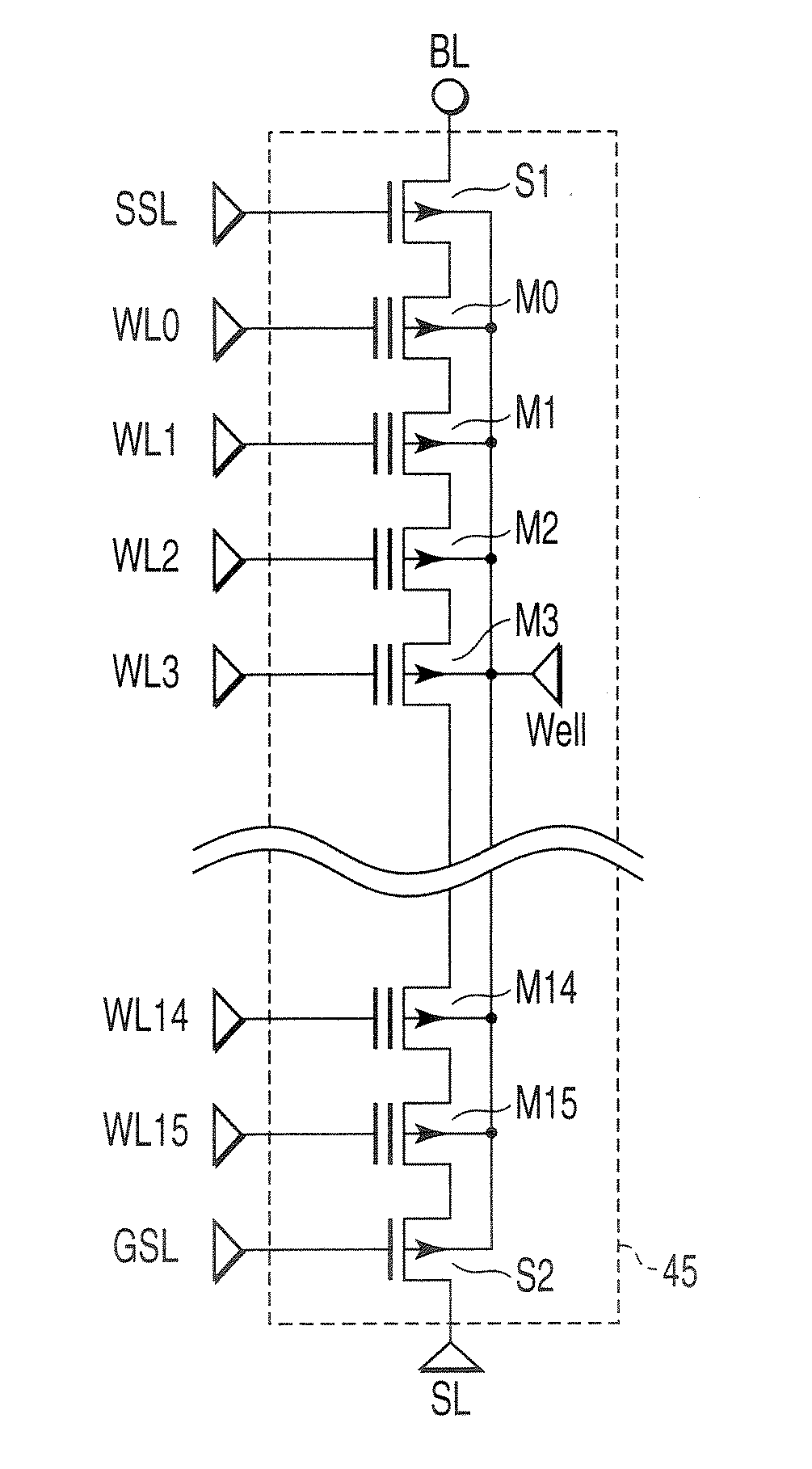

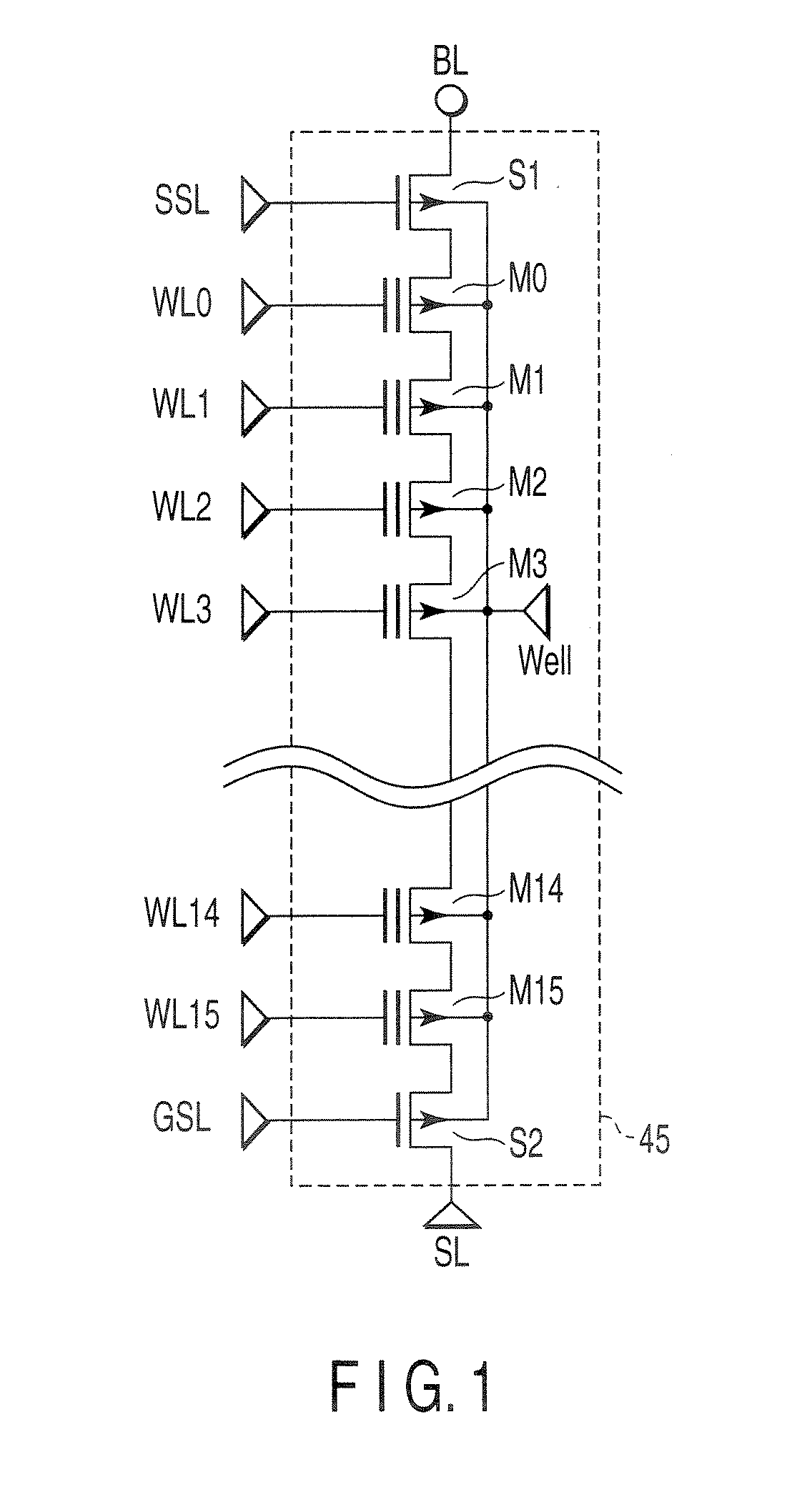

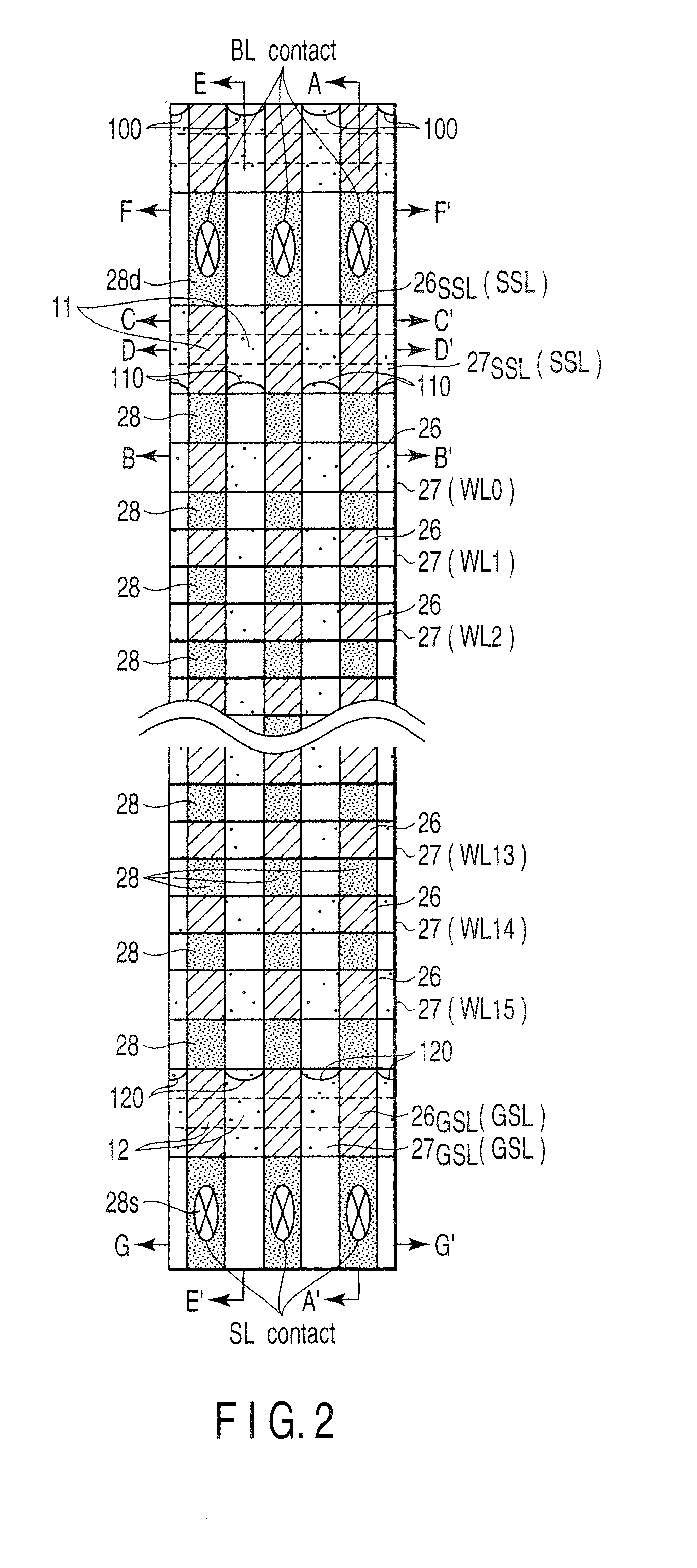

[0072]FIGS. 1 and 2 illustrate the structure of a nonvolatile semiconductor storage device according to the first embodiment of the present invention. In these figures, the suffixes of symbols represent the differences between the positions of elements used, and elements having the same main symbol indicate parts formed in the same step by using the same material.

[0073]FIG. 1 is an equivalent circuit diagram of a NAND string 45. FIG. 2 is a plan view of the layout of a plurality of juxtaposed NAND strings. FIG. 2 shows a structure obtained by juxtaposing three NAND strings shown in FIG. 1. FIG. 2 shows only a structure below control gate electrodes 27 in order to clearly indicate the structures of a memory cell and selection gate transistor.

[0074]As shown in FIG. 1, the current paths of nonvolatile memory cells M0 to M15 comprising MOS transistors each having a floating gate electrode (charge storage electrode) 26 connect in series to form a NAND memory cell block. One end of the se...

second embodiment

[0137]FIG. 18 is a plan view of the layout of a nonvolatile semiconductor storage device according to the second embodiment of the present invention. Note that in the following description, the same reference numerals as in FIG. 2 denote the same parts, and a detailed explanation thereof will be omitted. Note also that the suffixes of symbols represent the differences between the positions of elements used, and elements having the same main symbol indicate parts formed in the same step by using the same material.

[0138]FIG. 18 shows a structure obtained by juxtaposing three NAND strings shown in the equivalent circuit diagram of FIG. 1. FIG. 18 shows only a structure below gate electrodes 27 in order to clearly indicate the cell structure. Referring to FIG. 18, nonvolatile memory cells M0 to M15 comprising MOS transistors each having a floating gate electrode 26 connect in series, and one end connects to a data transfer line via a selection transistor S1. The other end connects to a ...

third embodiment

[0151]FIG. 26 is a plan view of the layout of a nonvolatile semiconductor storage device according to the third embodiment of the present invention. Note that the same reference numerals as in the nonvolatile semiconductor storage devices according to the first and second embodiments denote the same parts, and a detailed explanation thereof will be omitted. Note also that the suffixes of symbols represent the differences between the positions of elements used, and elements having the same main symbol indicate parts formed in the same step by using the same material.

[0152]FIG. 26 shows a structure obtained by juxtaposing three NAND strings shown in the equivalent circuit diagram of FIG. 1. FIG. 26 particularly shows only a structure below control gate electrodes 27 in order to clearly indicate the cell structure. Referring to FIG. 26, nonvolatile memory cells M0 to M15 comprising MOS transistors each having a floating gate electrode 26 connect in series, and one end connects to a dat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More