Patents

Literature

431 results about "Cell block" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

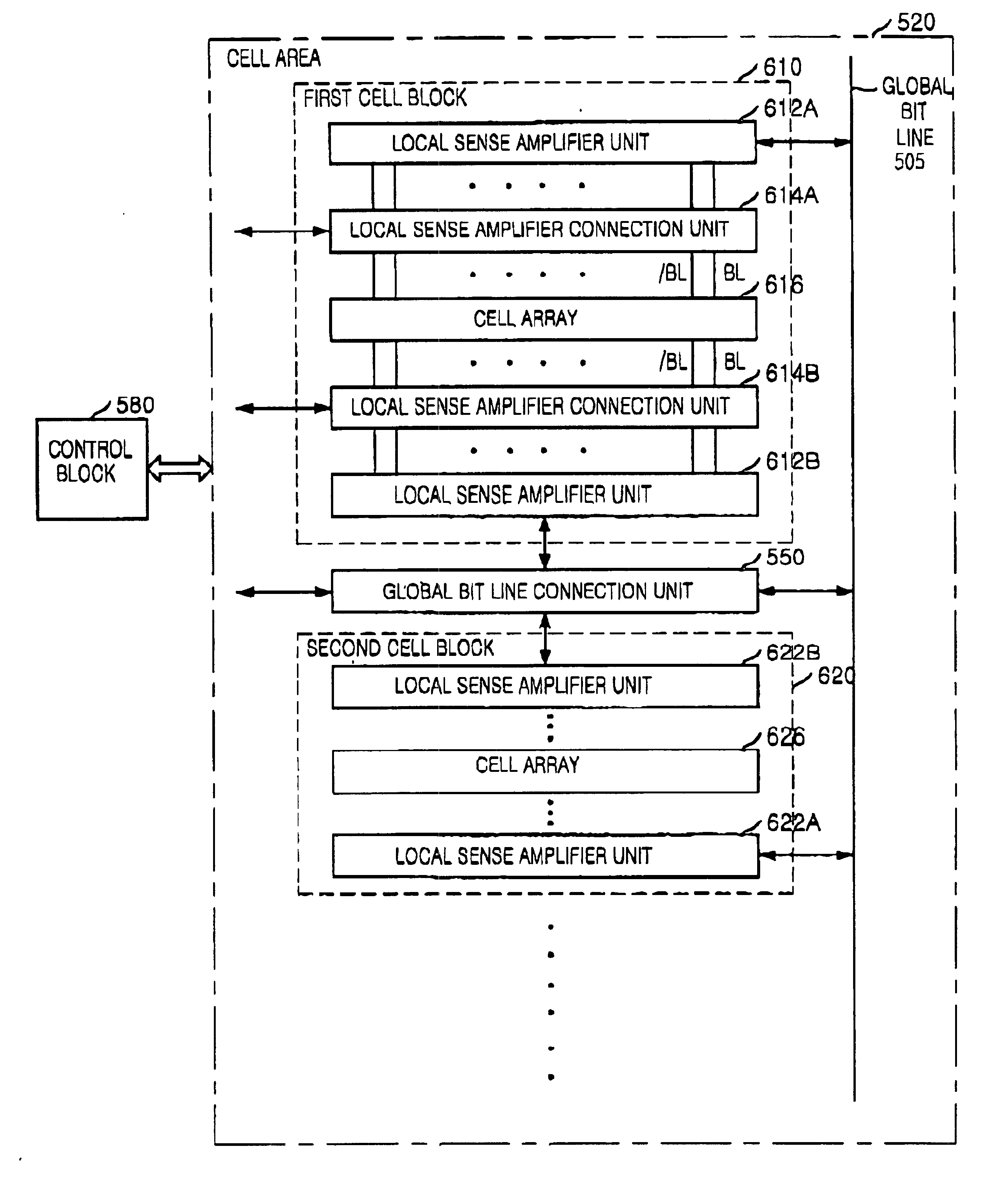

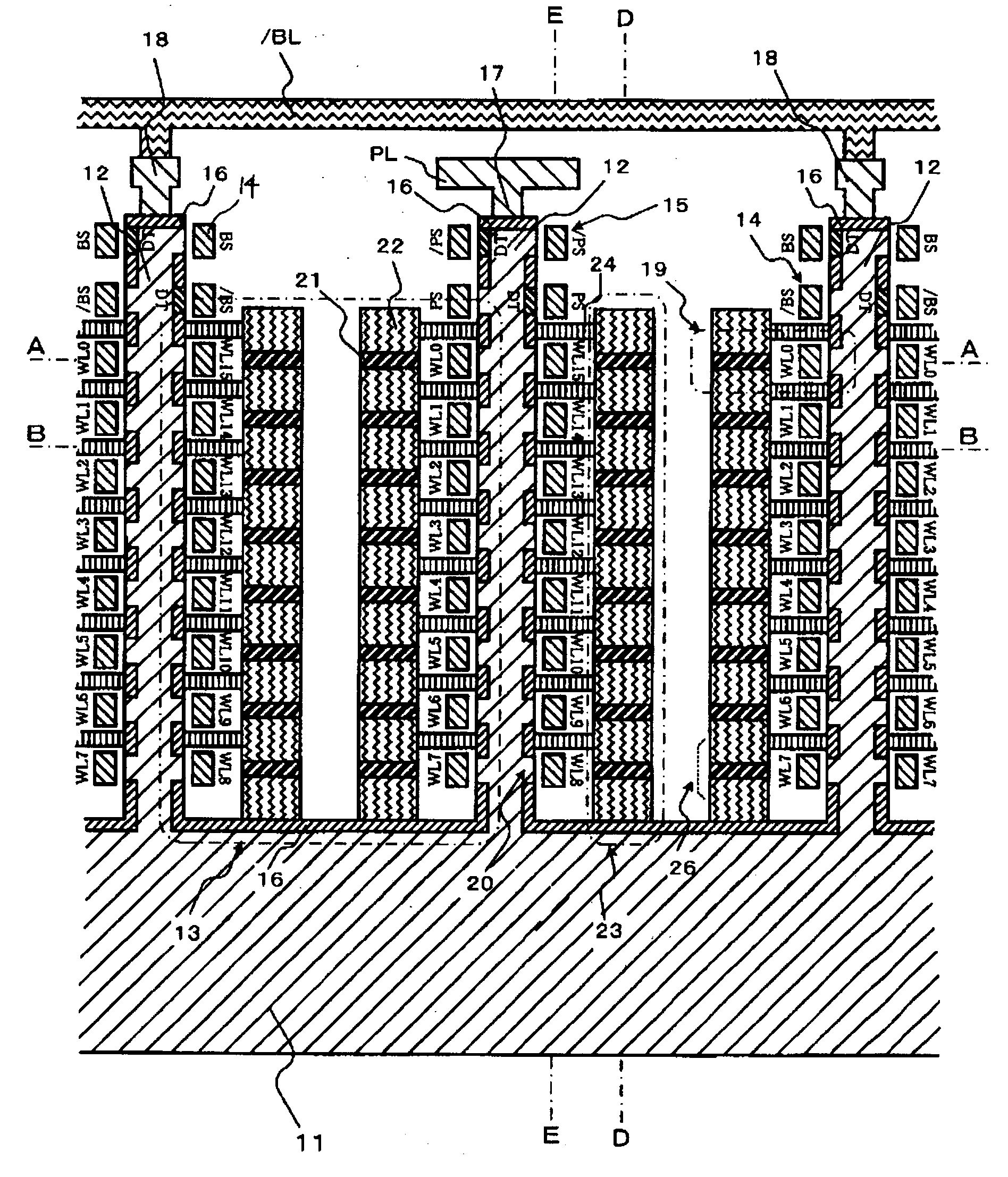

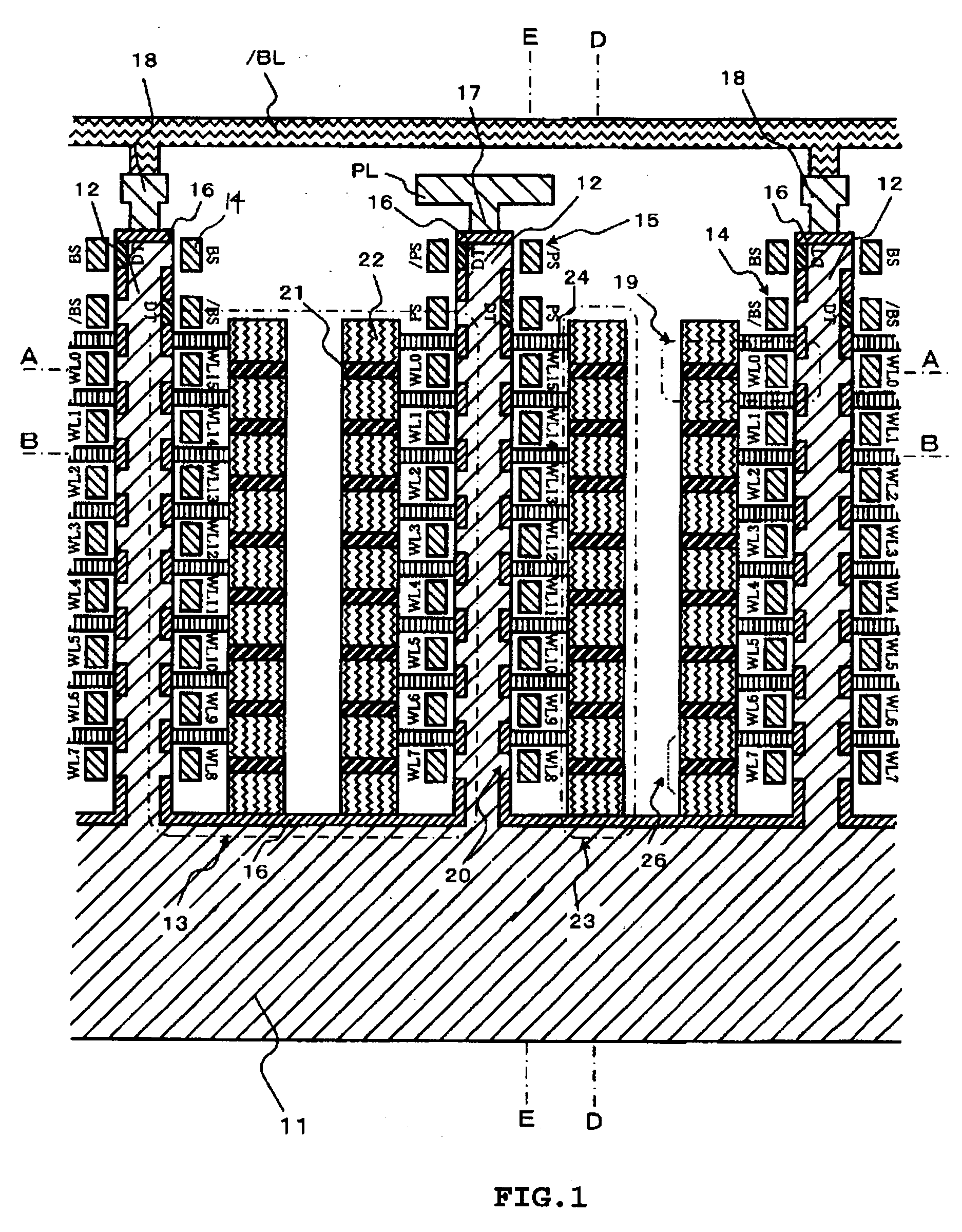

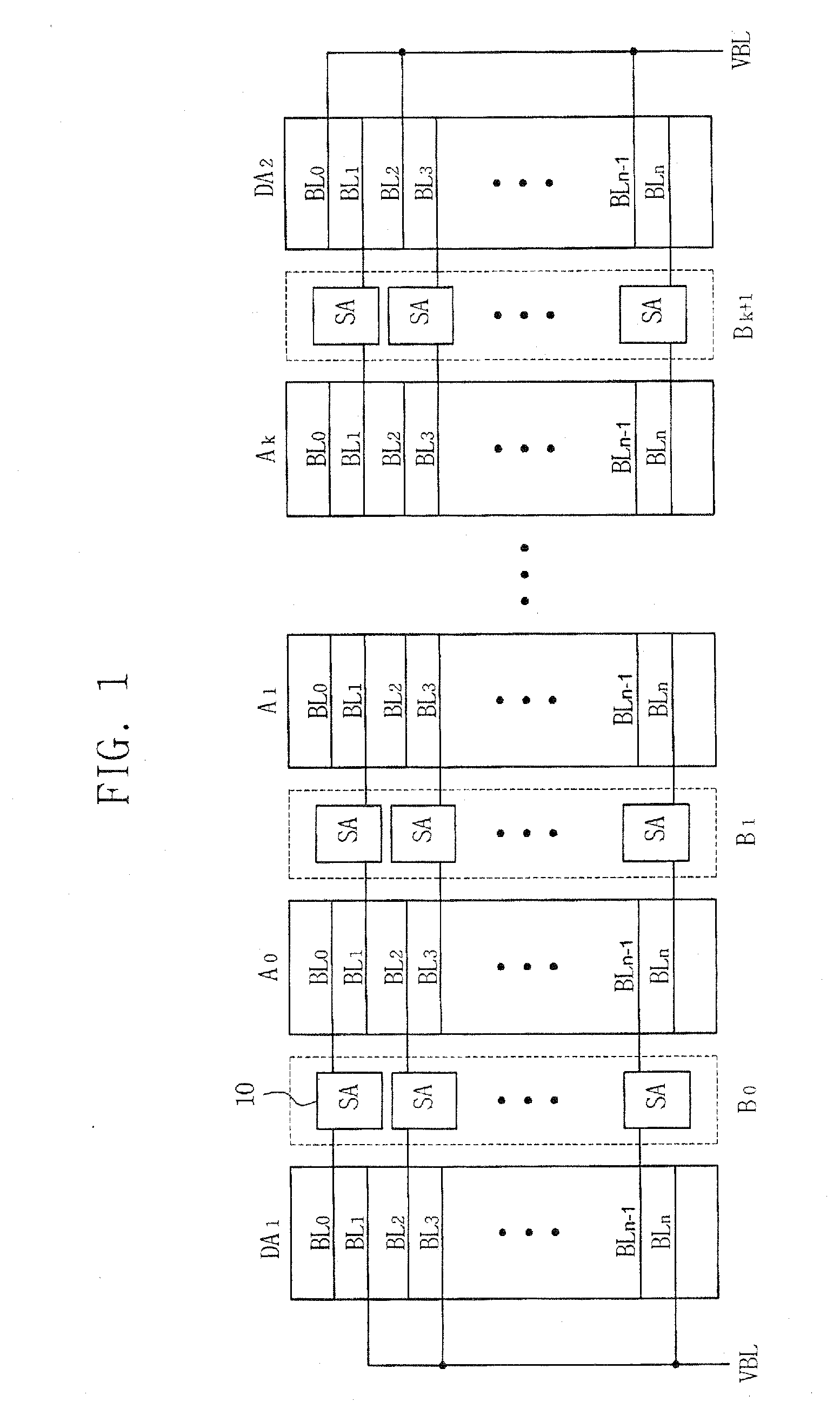

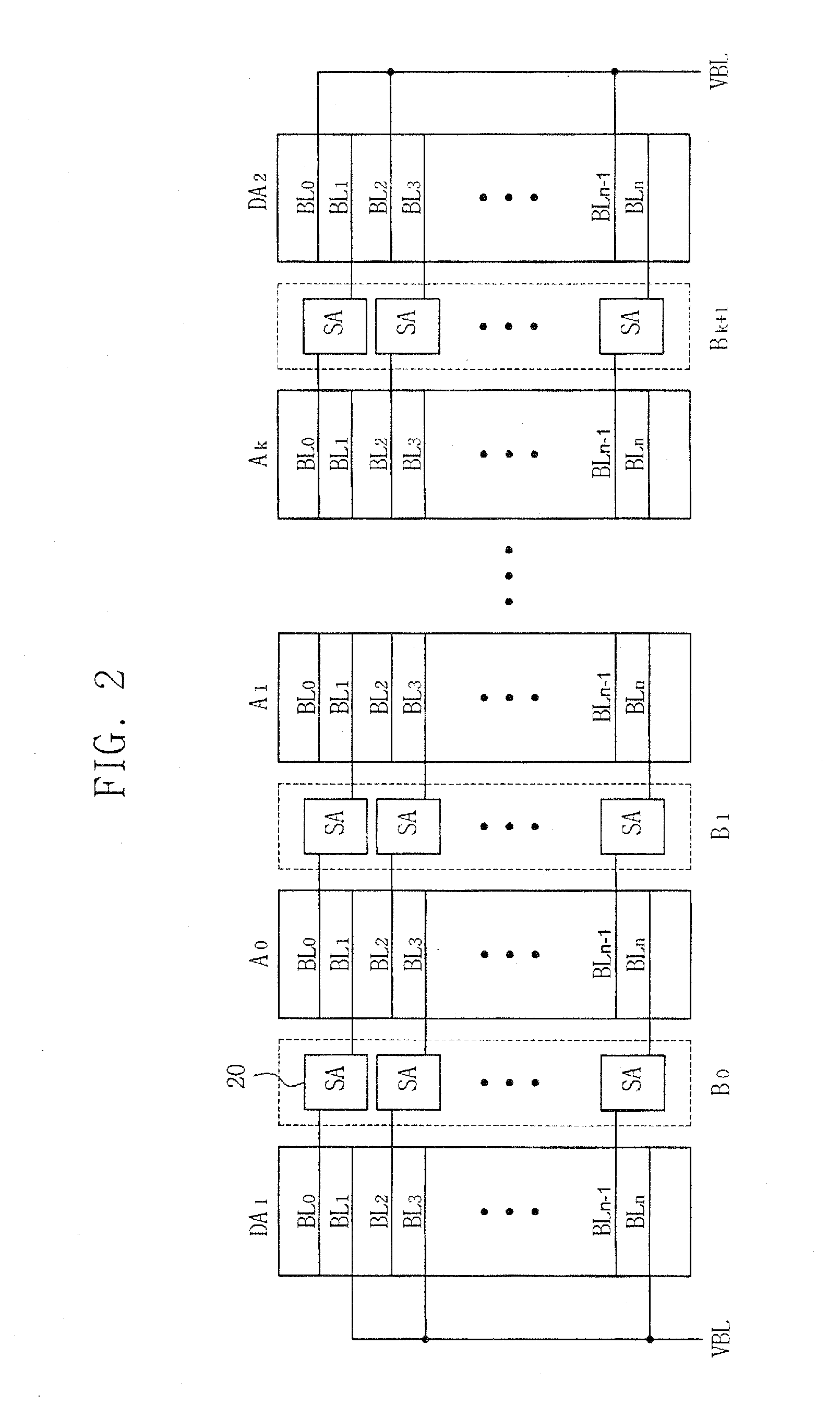

Semiconductor memory device with reduced data access time

A memory device includes at least two cell blocks connected to a global bit line for outputting data in response to an instruction; at least one global bit line connection unit for selectively connecting the global bit line to each cell block under control of a control block, one global bit line connection unit being allocated between the two cell blocks; and said control block for controlling output of data stored in each cell block to the global bit line and restoration of the outputted data of the global bit line to the original cell block or another cell block which is determined by depending upon whether data in response to a next instruction is outputted from the original cell block or another cell block.

Owner:SK HYNIX INC

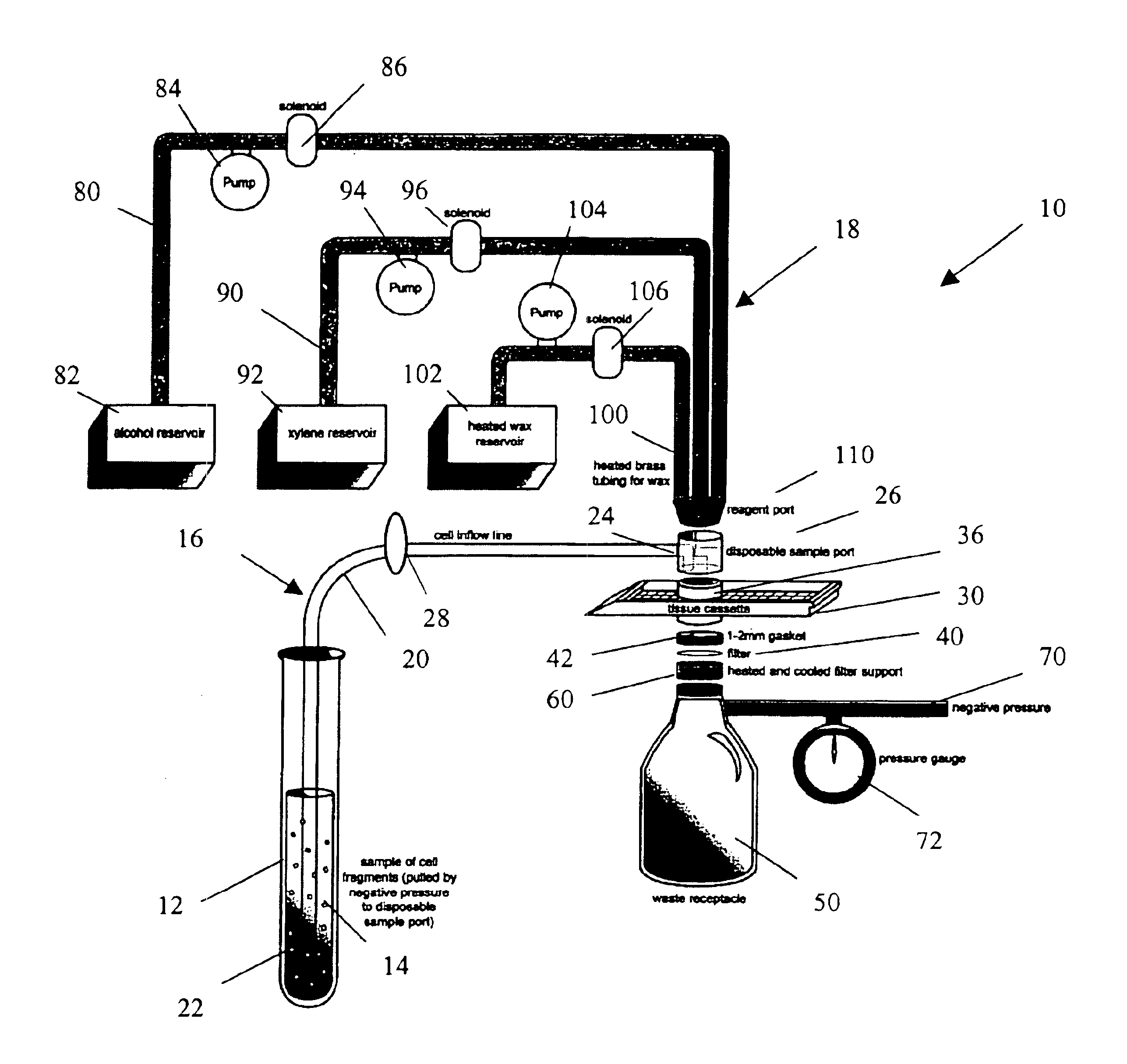

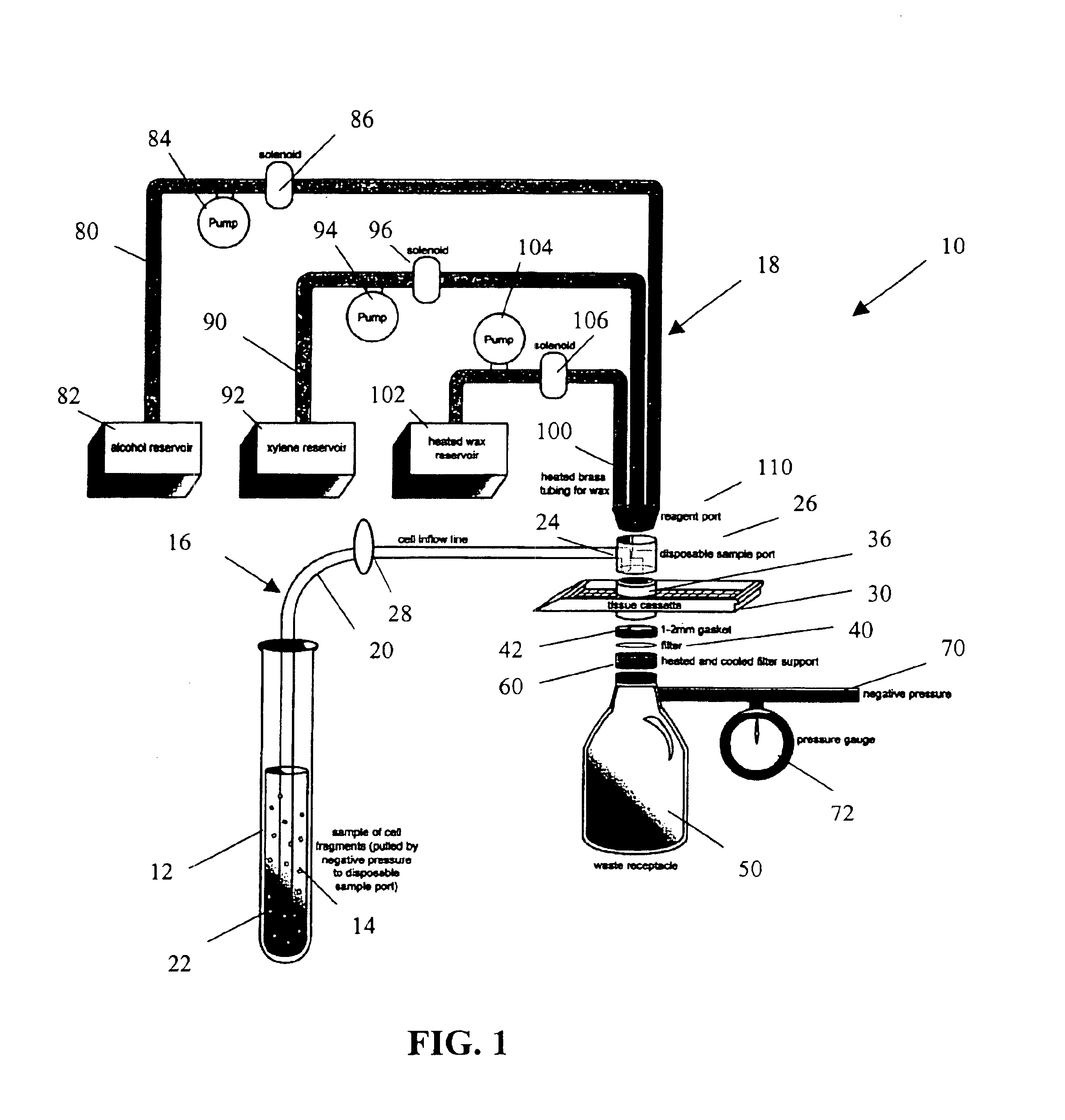

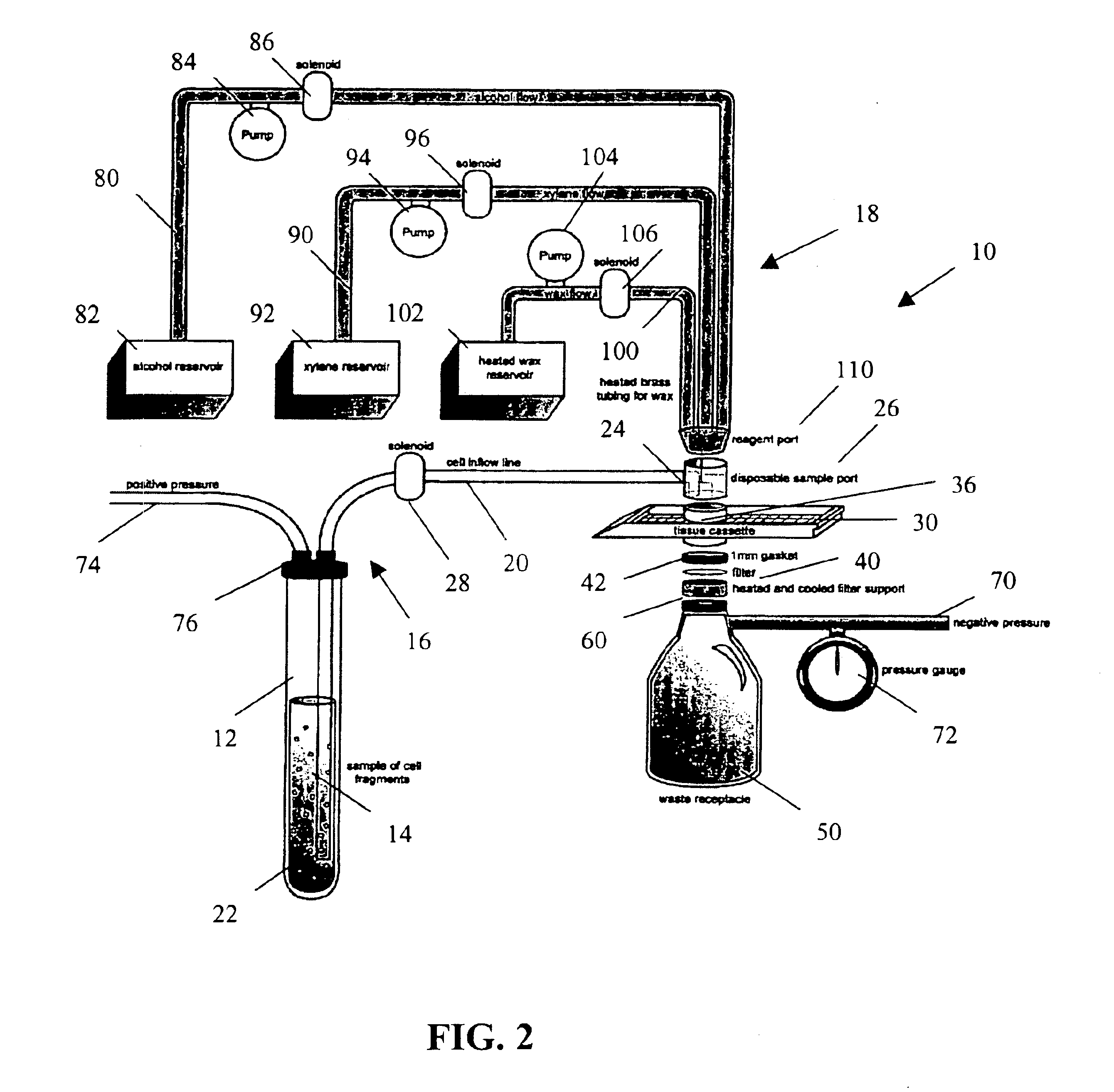

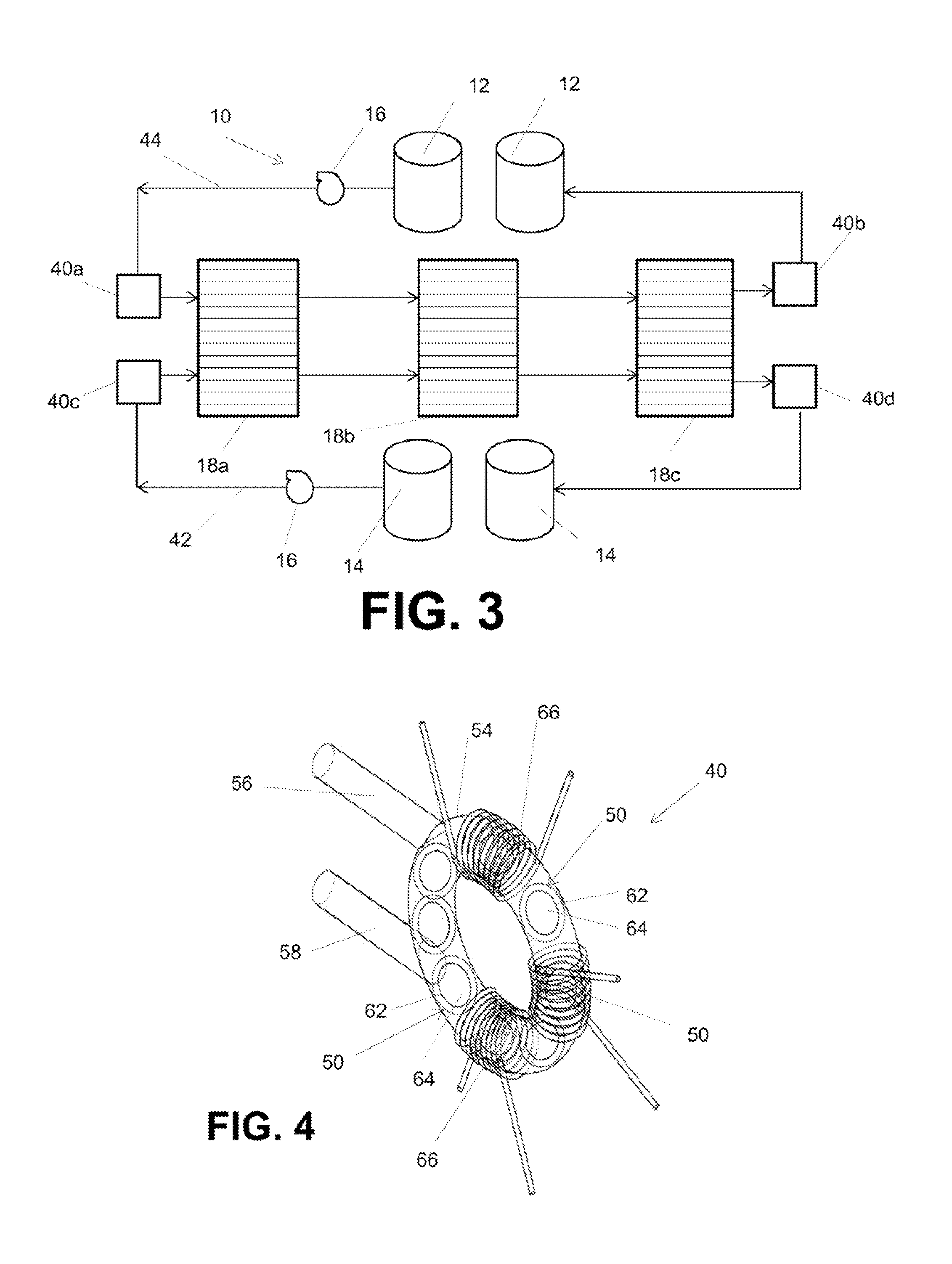

Rapid cell block embedding method and apparatus

ActiveUS6913921B2Maximize efficiencyReduce amountBioreactor/fermenter combinationsBiological substance pretreatmentsEngineeringReagent

A method and apparatus for embedding cells that utilizes a flow-through embedding technique maximizes the efficiency of extractions and decreases time for embedding the cell fragments, minimizes cell loss, and automatically positions cell samples at the position in which a microtome blade will section them. The apparatus includes a cell flow pathway defined by an inflow tube for delivering cell fragments from a cell sample to a sample port. The sample port is in fluid communication with a tissue cassette having attached thereto a filter. The cell flow pathway is in communication with a reagent flow pathway for delivering the reagents through the sample port to the cassette. The apparatus is configured such that the application of pressure directs the cell fragments from the cell sample through the cell flow pathway, and effects delivery of the reagents through the reagent flow pathway. The apparatus produces an embedded cell block having concentrated cells near the plane of the block to be sectioned in a quick and efficient manner.

Owner:MASSACHUSETTS UNIV OF

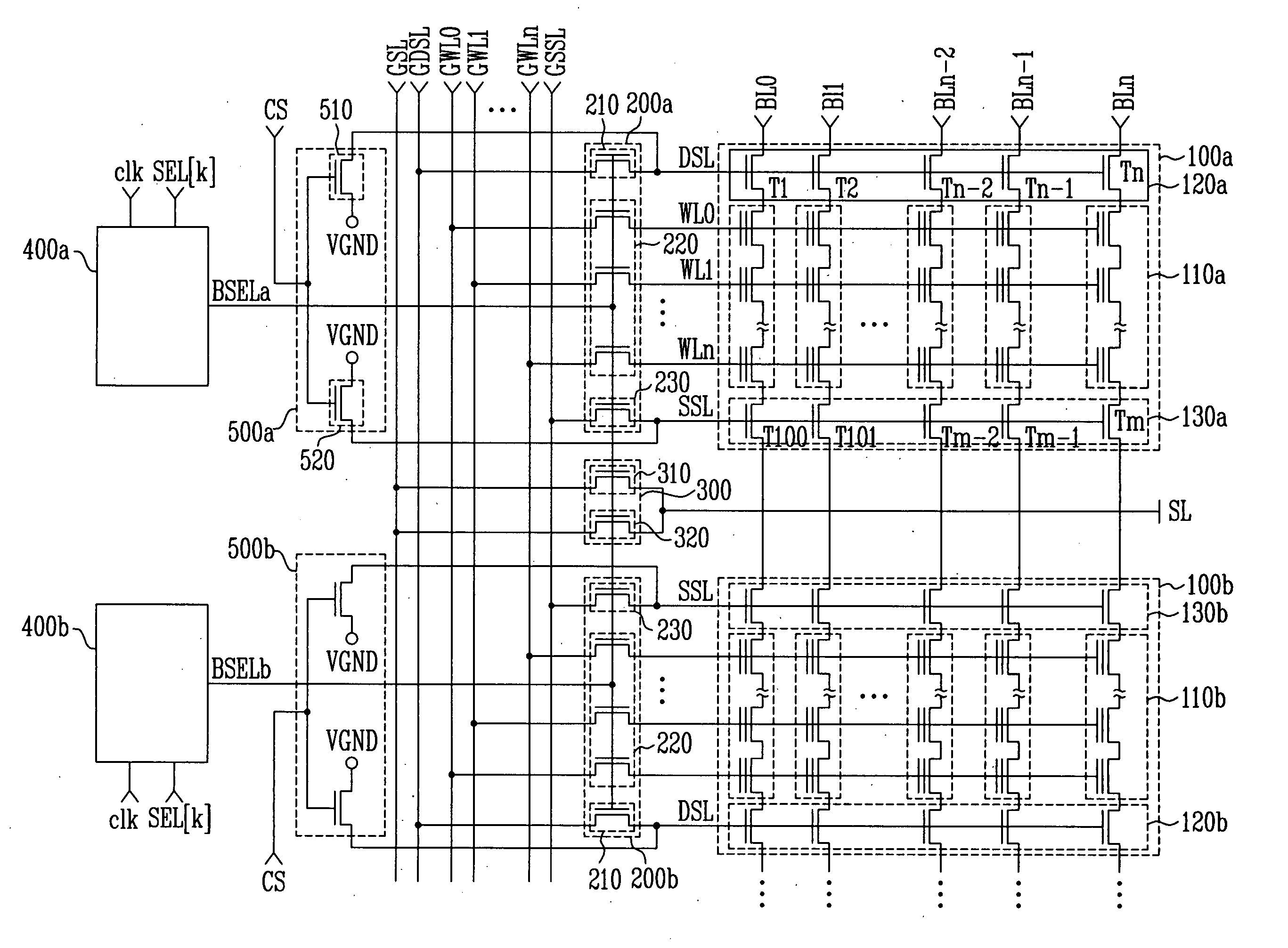

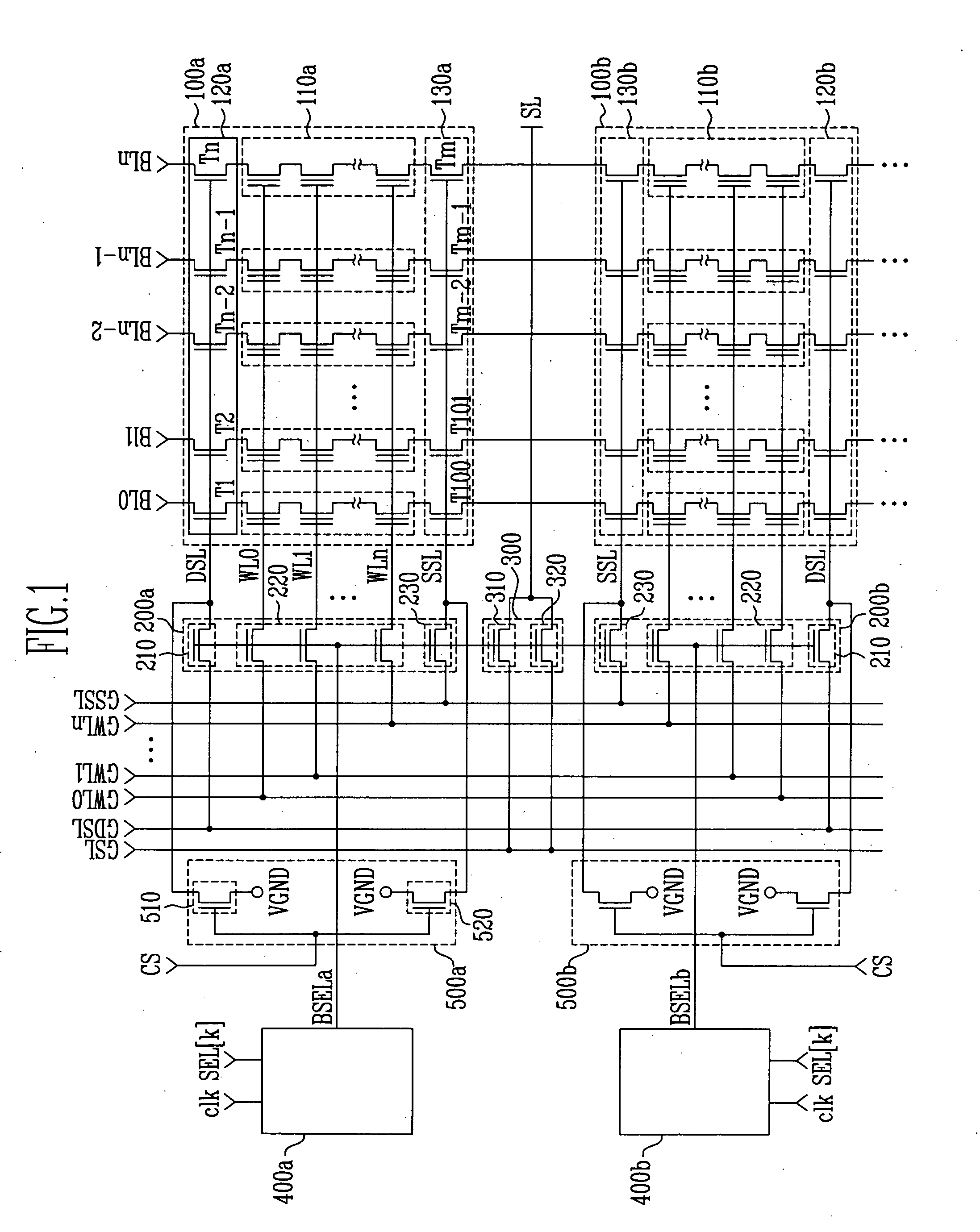

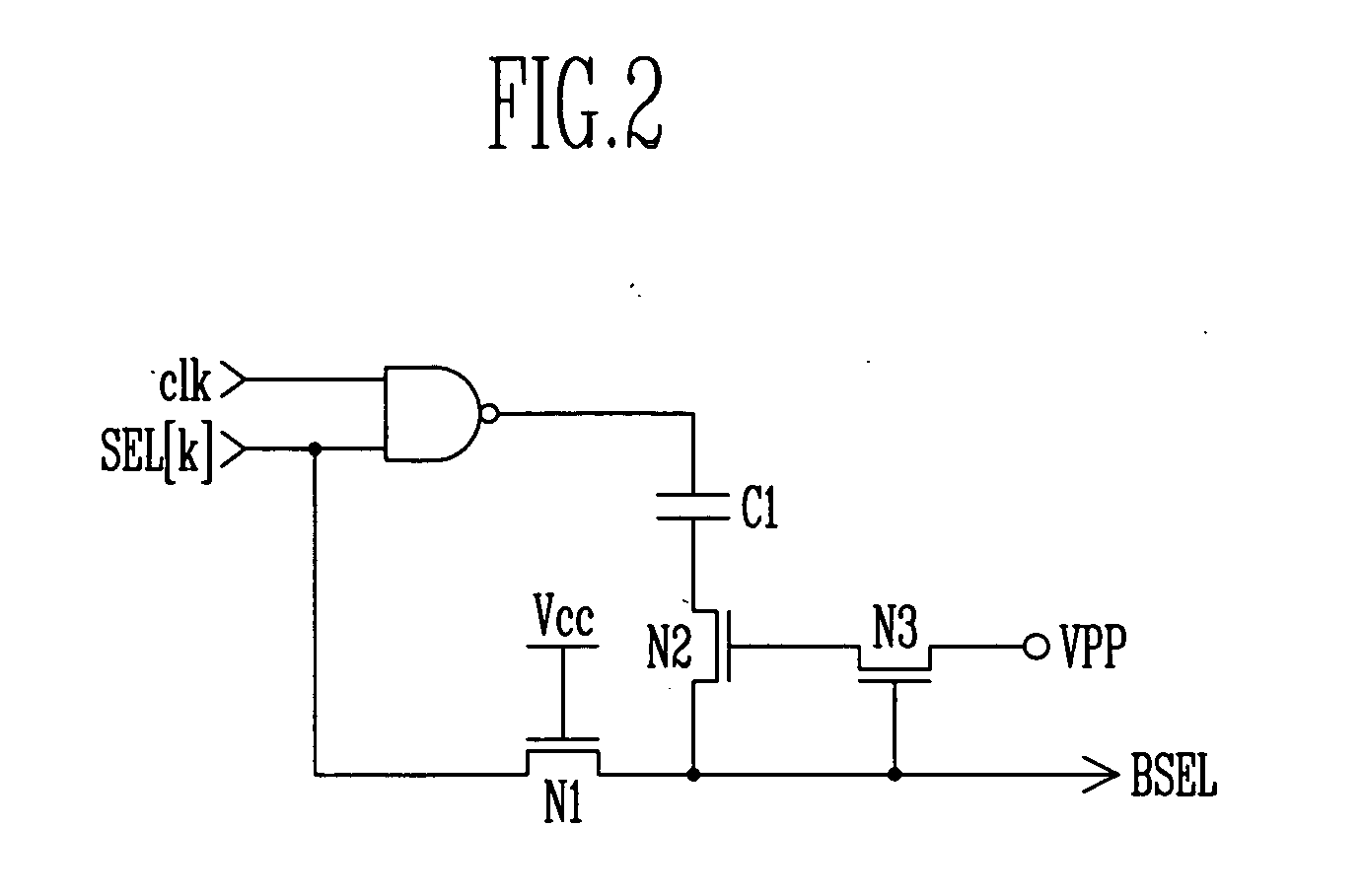

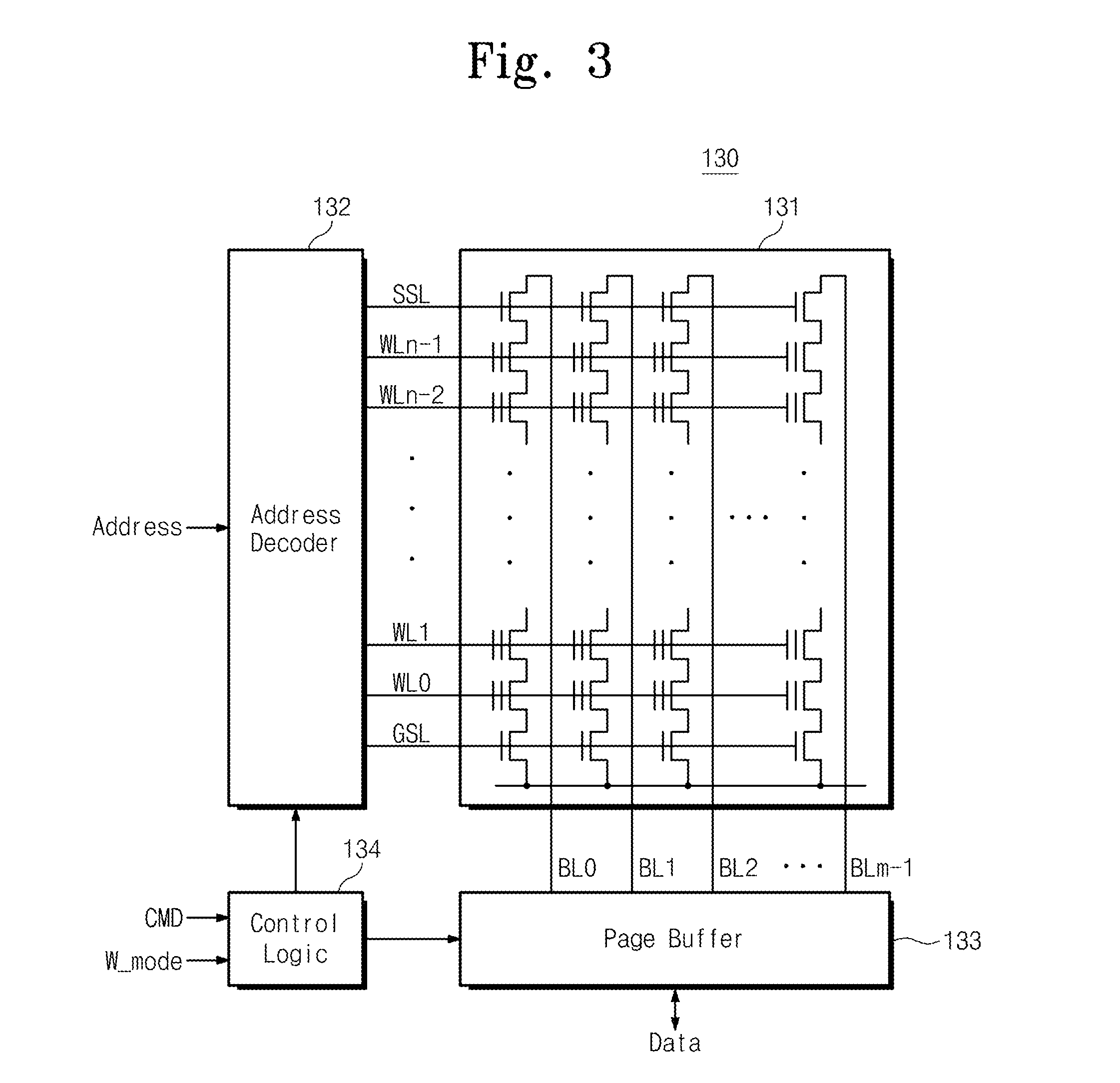

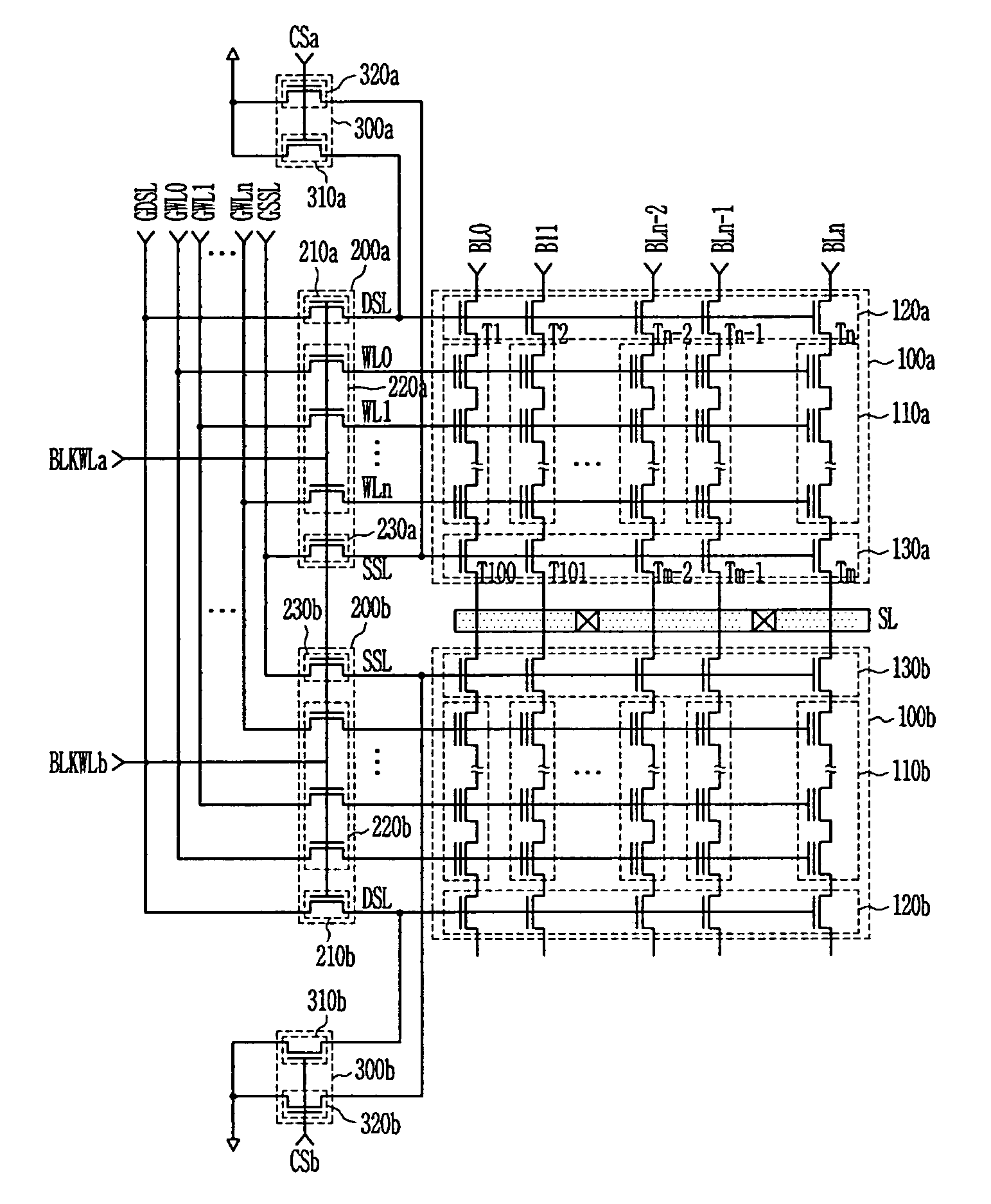

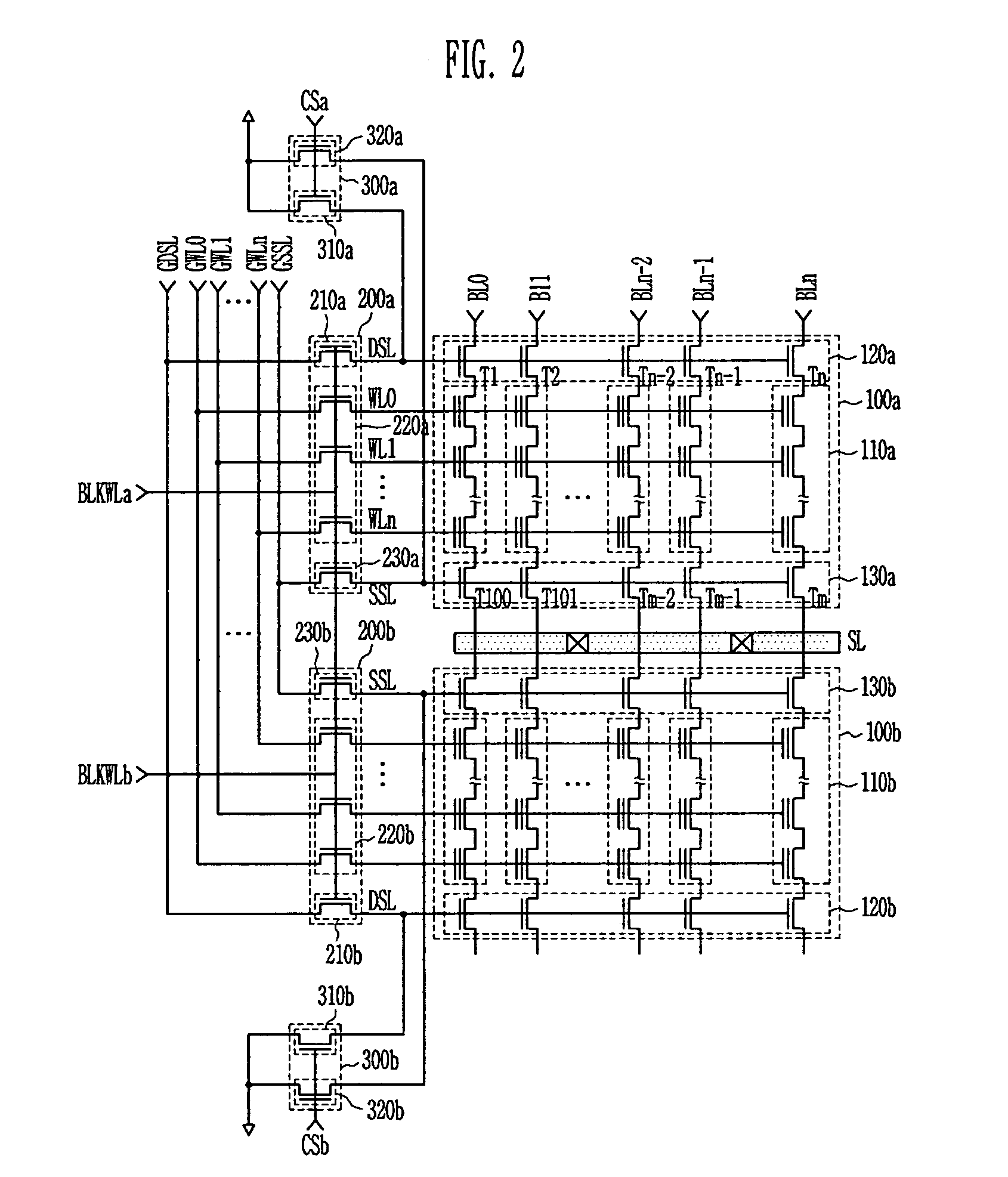

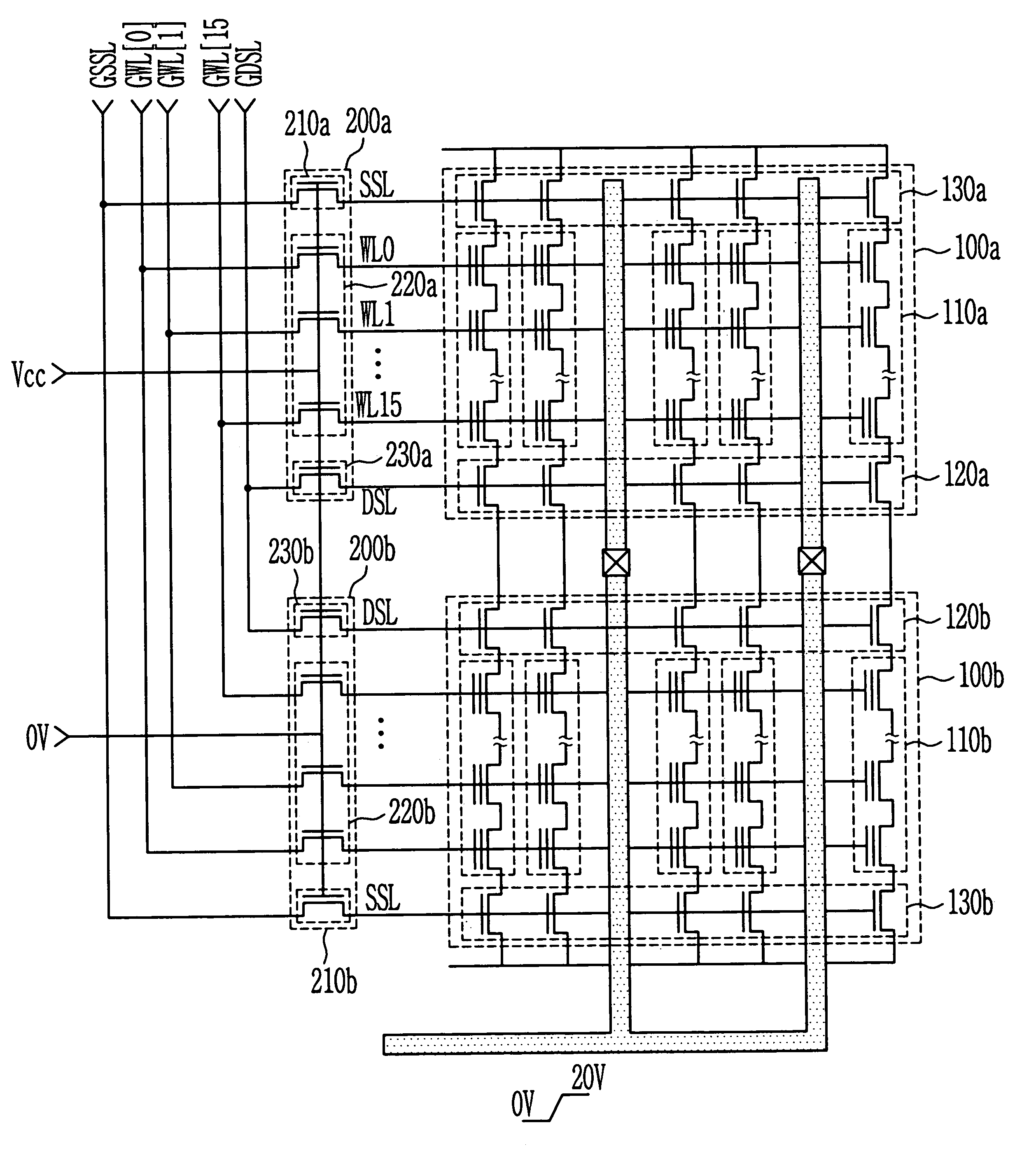

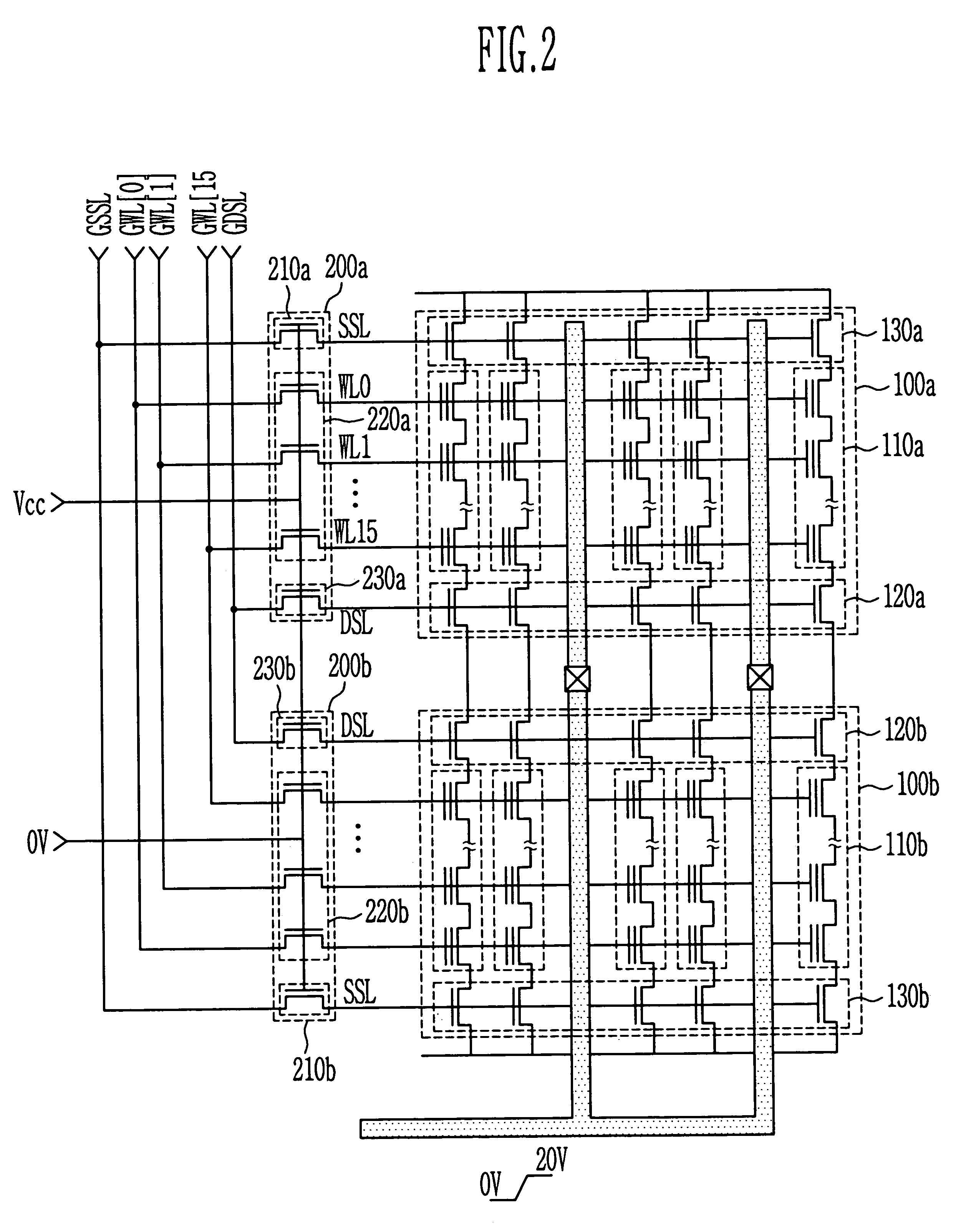

NAND flash memory device and method of programming the same

Provided is directed to a NAND flash memory device and a method of programming the same, which can improve integration of the device by removing a common source line connecting with a source line coupled to a plurality of cell blocks, control a voltage applied to a source line by each cell block, and rise a precharge level in a channel area by applying a pumping voltage to the source line relatively having low capacitance instead of a bitline having a large capacitance, and as a result of those, the NAND flash memory device can reduce disturbance, use a lower voltage than a power supply voltage on the bitline, which leads to reduce a current consumption.

Owner:STMICROELECTRONICS SRL +1

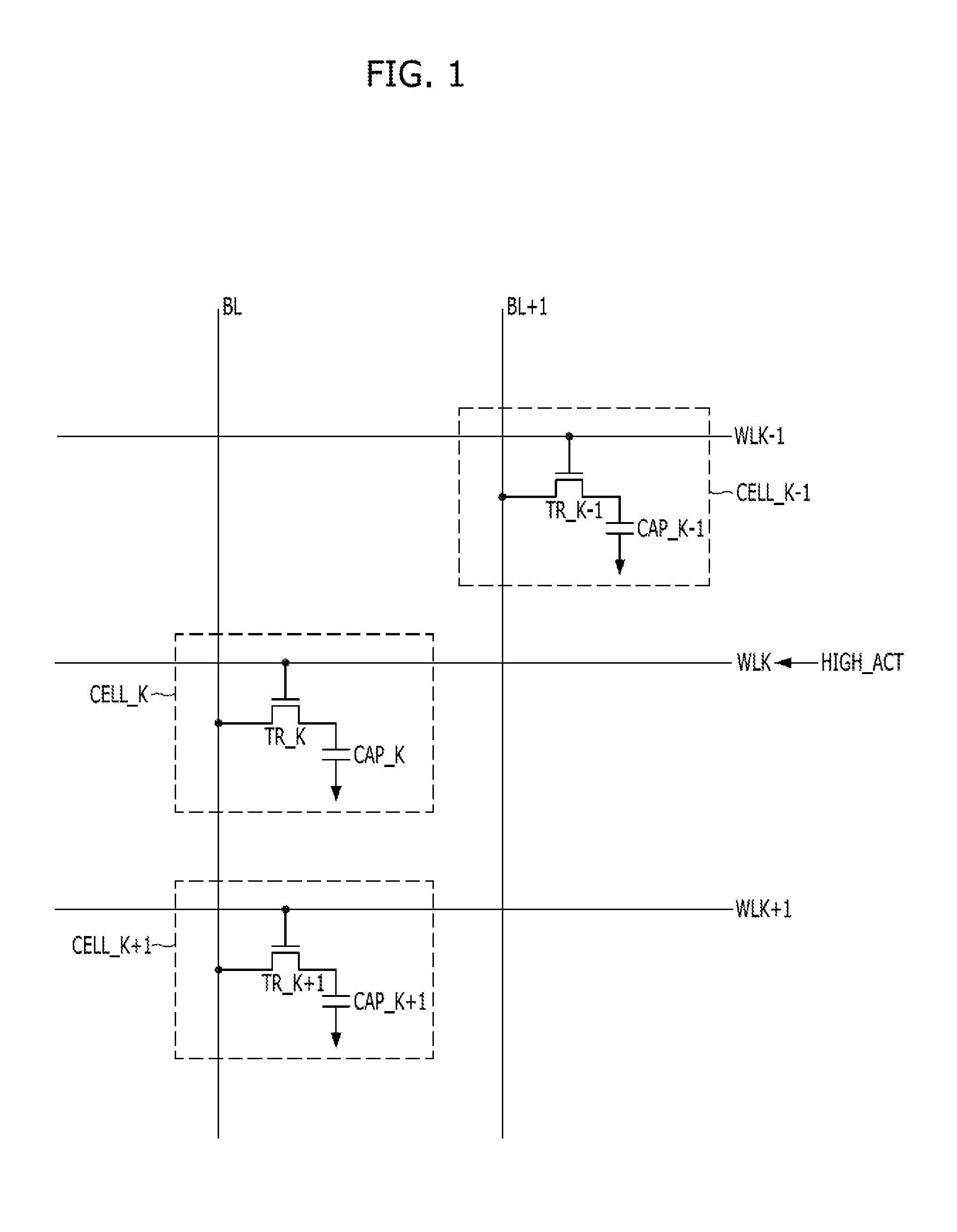

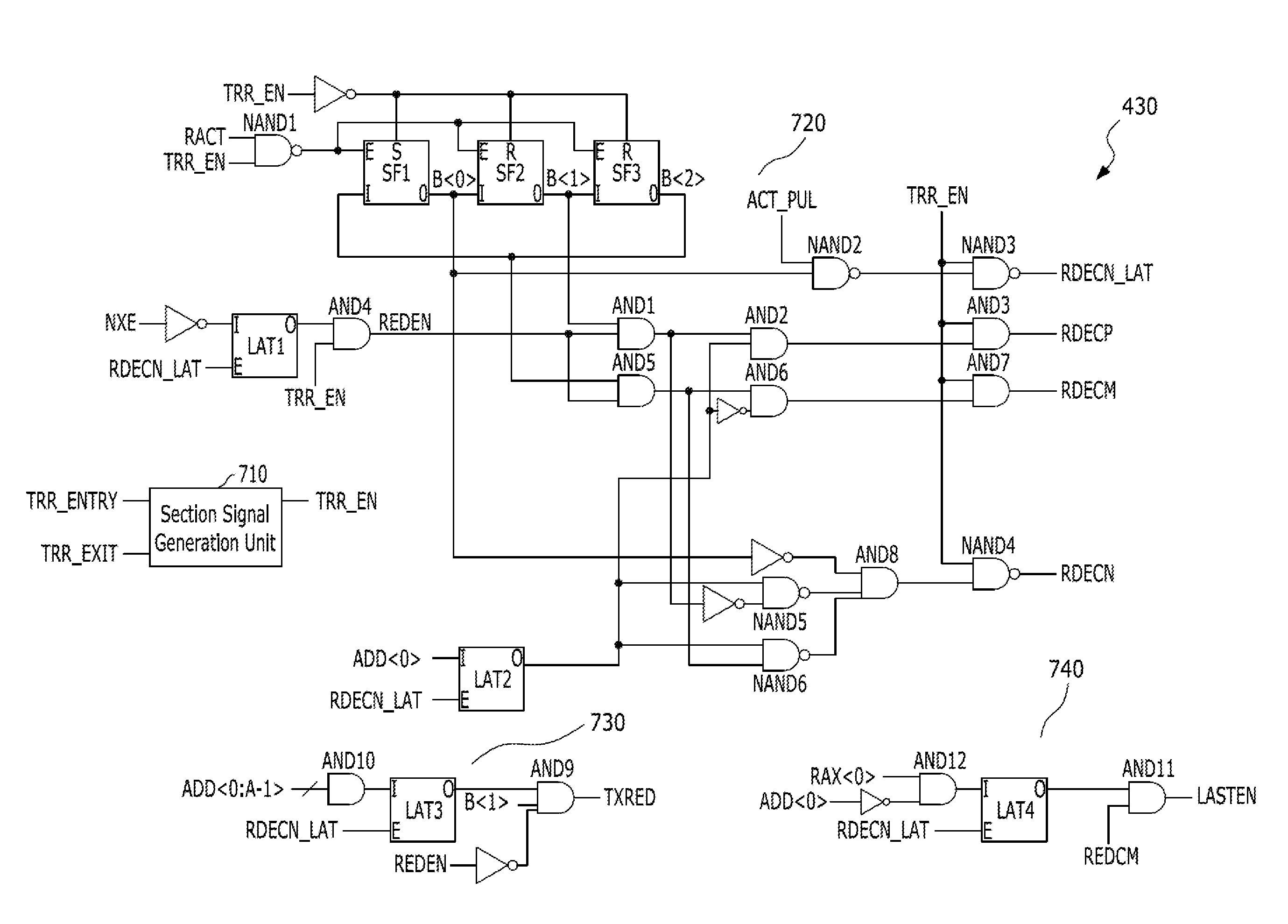

Memory and memory system including the same

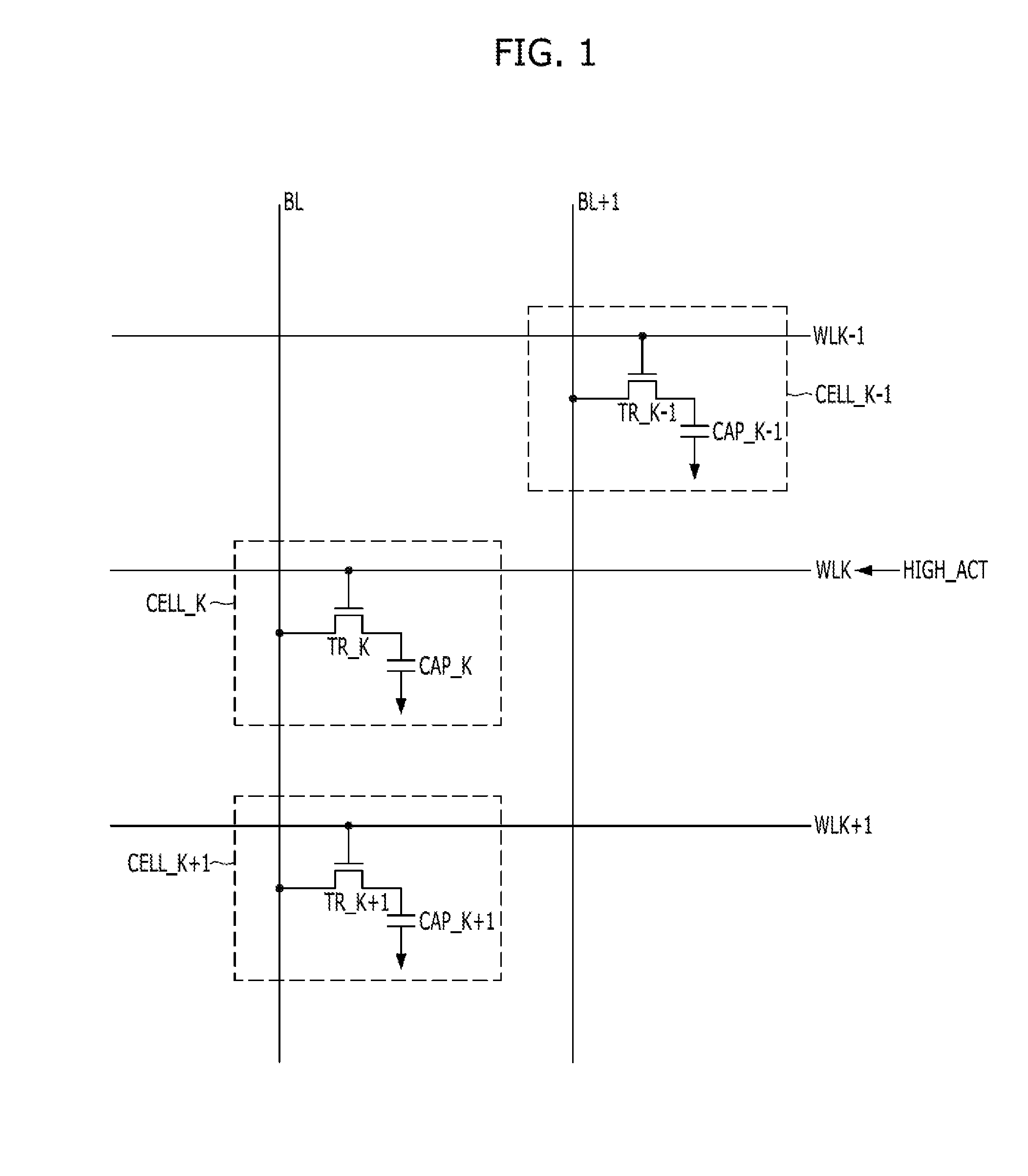

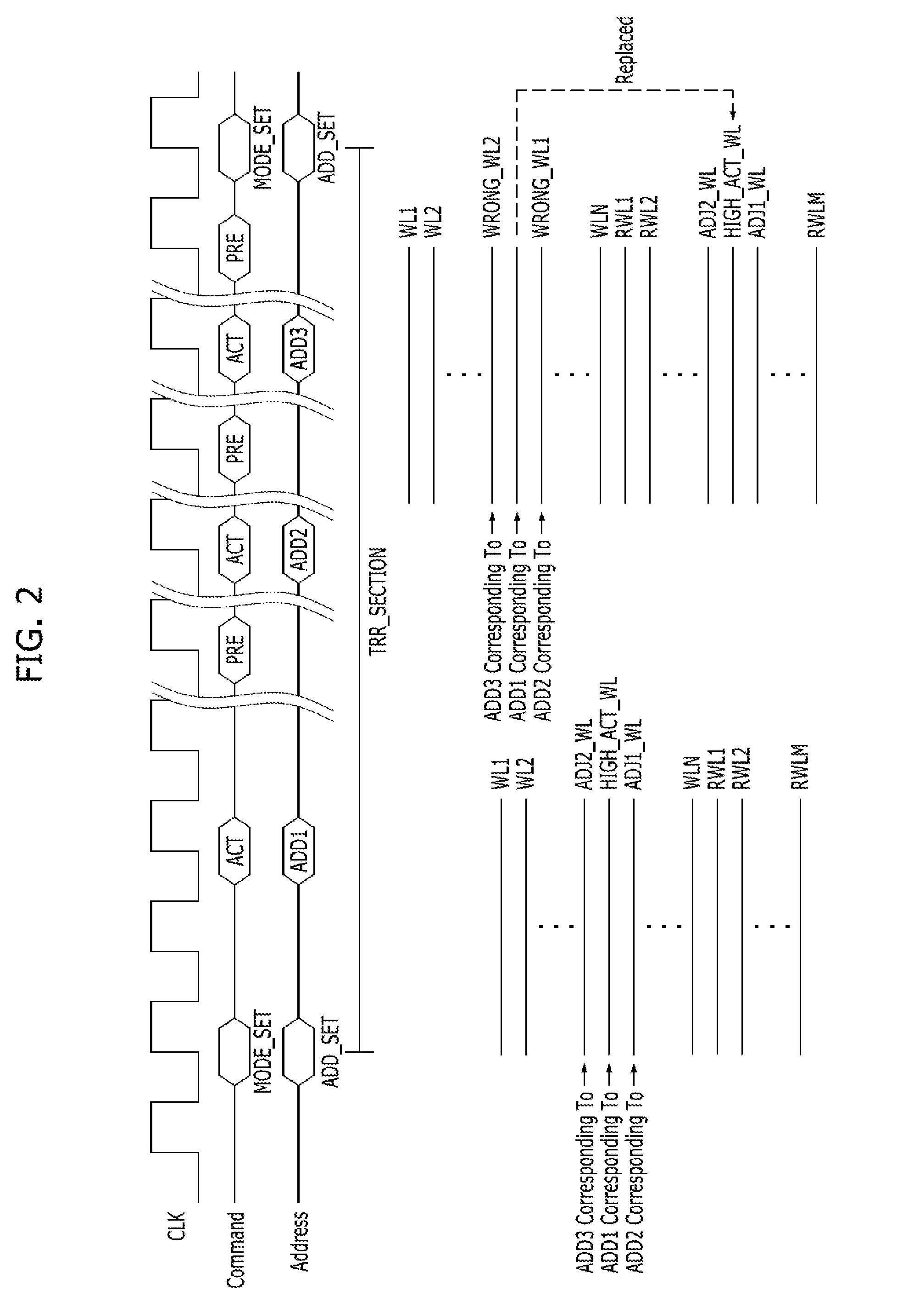

A memory includes a first cell block comprising a plurality of first word lines and one or more first redundancy word lines for replacing at least one of the plurality of first word lines; a second cell block comprising a plurality of second word lines and one or more second redundancy word lines for replacing at least one of the plurality of second word lines; and a control unit suitable for sequentially receiving one or more input addresses, during a target refresh section, selecting one of the first cell block and the second cell block and a word line included in the selected cell block in response to a first input address, and activating one or more adjacent word lines adjacent to the selected word line, which is selected based on the first input address, when the selected word line is adjacent to the redundancy word line, wherein the adjacent word lines comprise the redundancy word line.

Owner:SK HYNIX INC

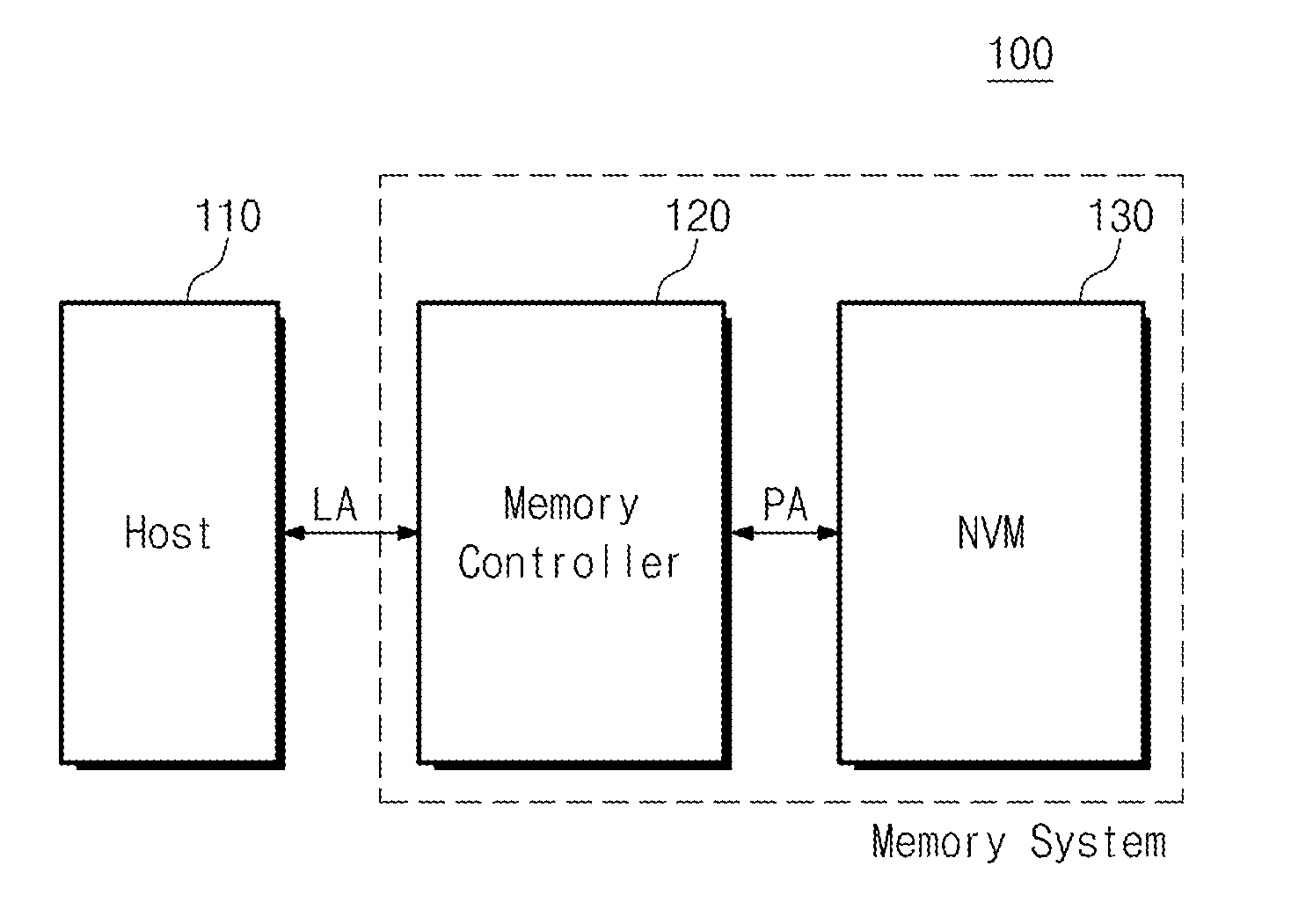

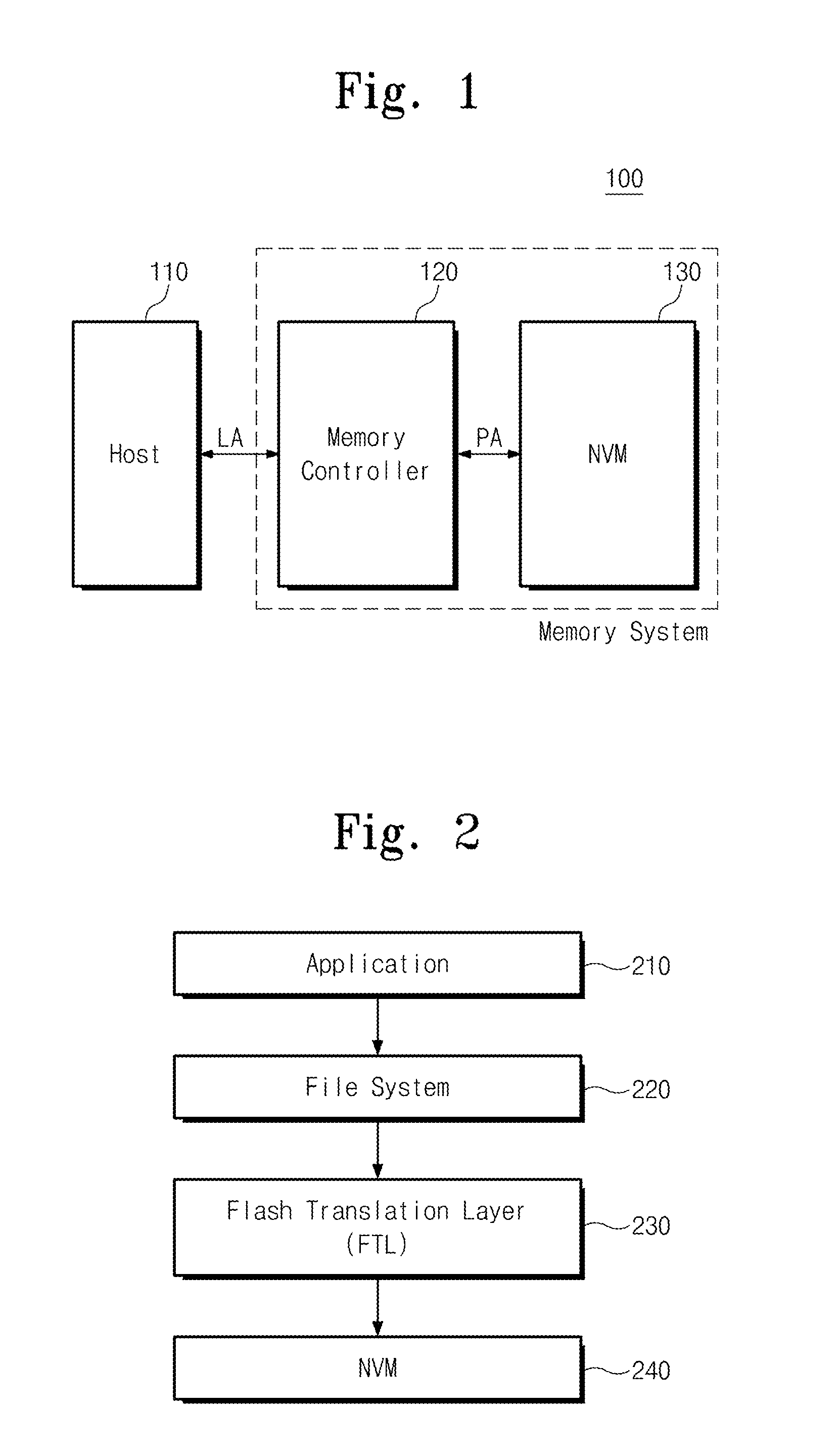

Memory system selecting write mode of data block and data write method thereof

ActiveUS20120005415A1Improve performanceMemory adressing/allocation/relocationSingle levelMulti-level cell

A method of performing a write operation in a nonvolatile memory device comprises storing write data in a log block used to update a data block, determining whether a write pattern stored in the log block is a sequential write pattern or a random write pattern, and selecting a new data block for storing merged data in the data block and the log block. The new data block is determined to be a single-level cell block or a multi-level cell block according to the determined write pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

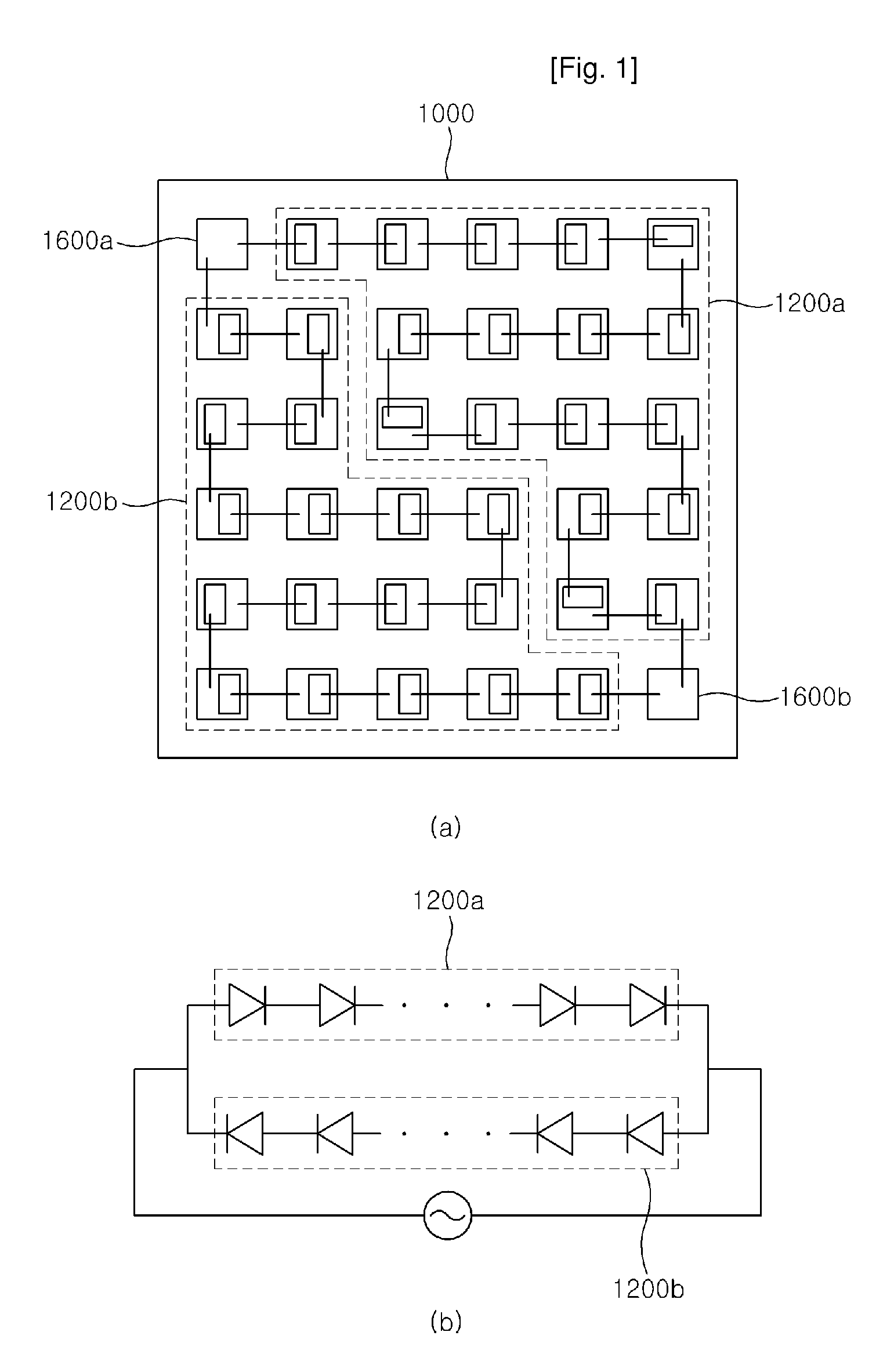

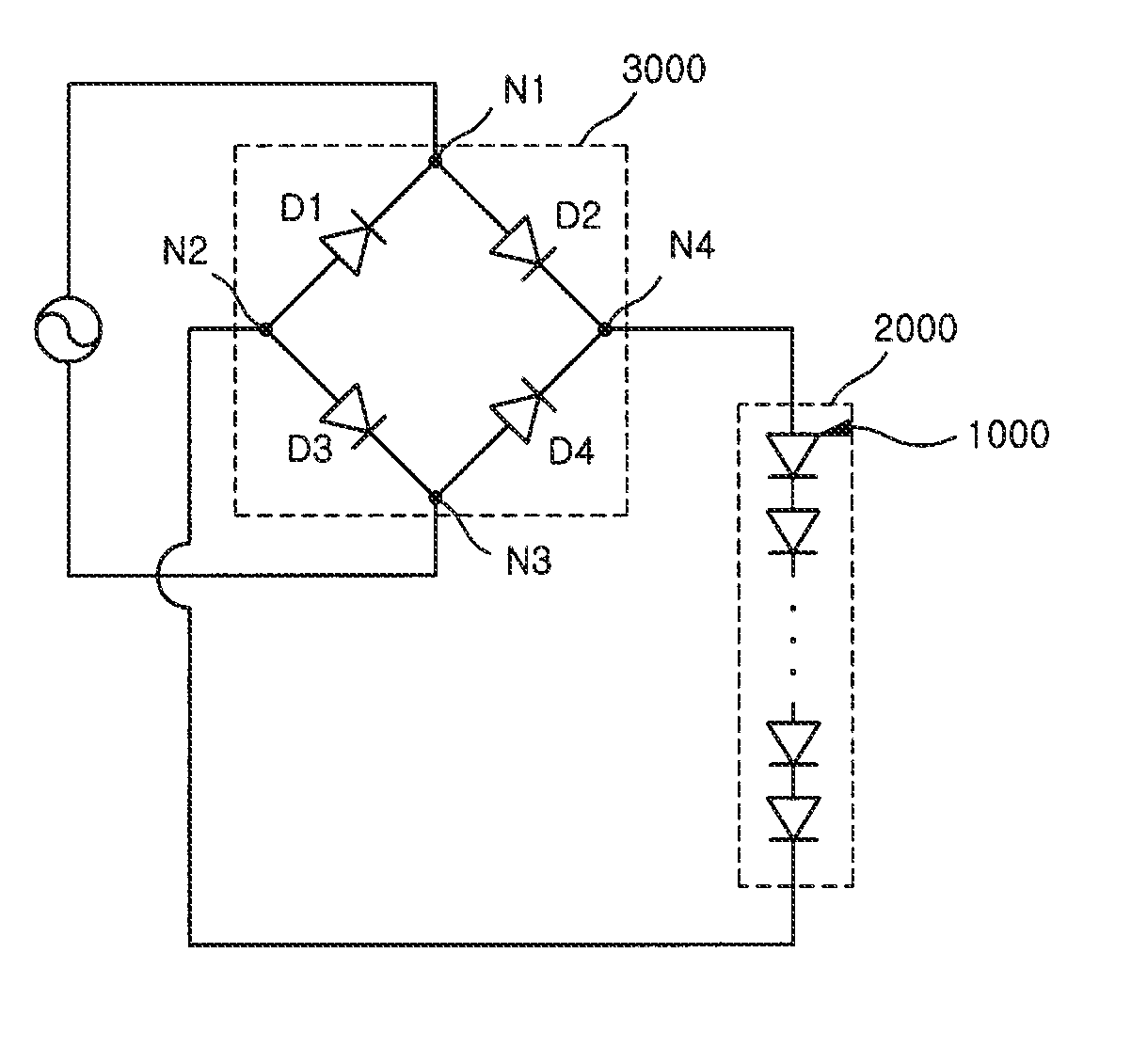

Light Emitting Device with Light Emitting Cells Arrayed

ActiveUS20080218098A1Luminance of lightReliability of of lightElectroluminescent light sourcesSolid-state devicesLight-emitting diodeLight emitting device

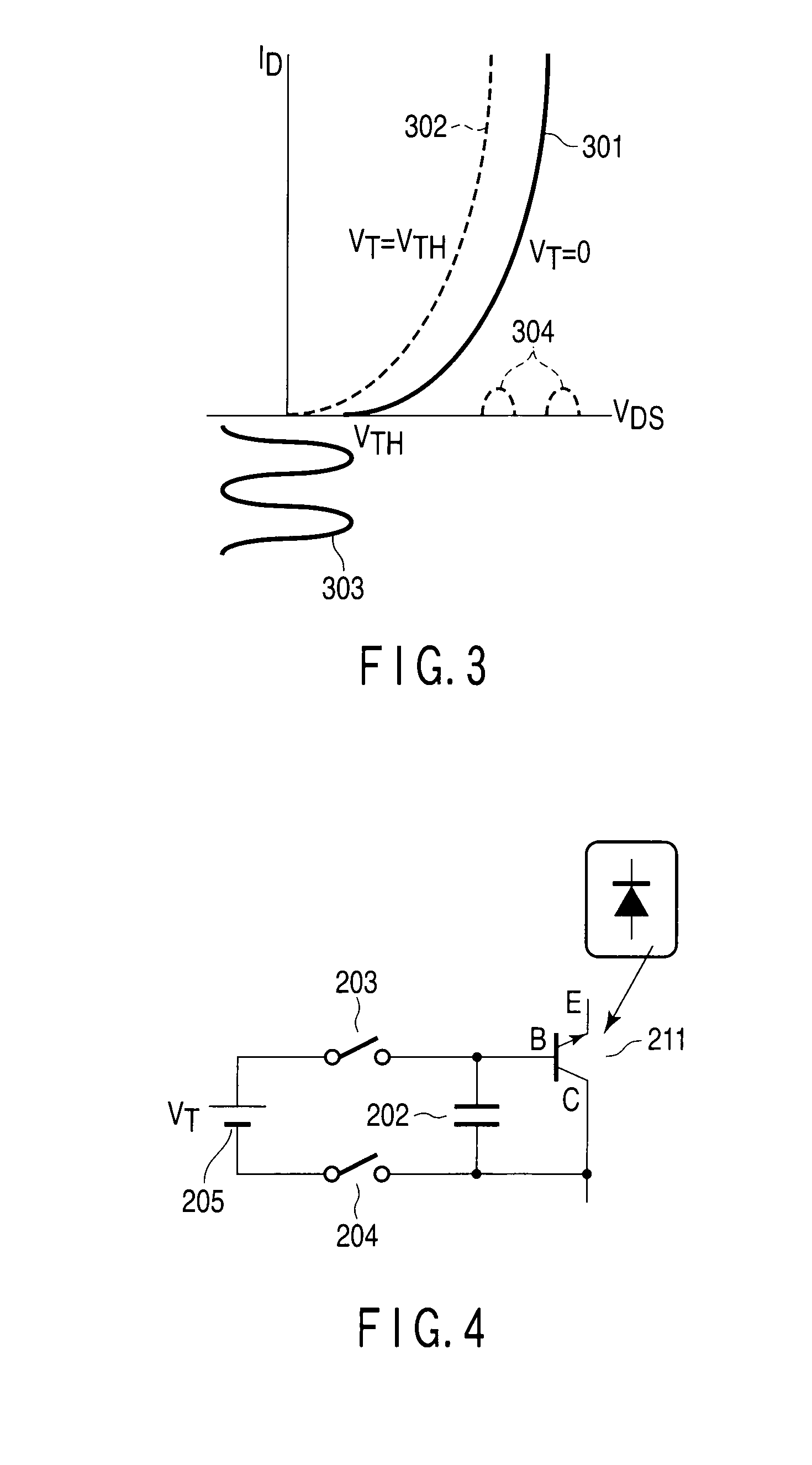

The present invention relates to a light emitting device. The light emitting device according to the present invention comprises a light emitting cell block having a plurality of light emitting cells; and a bridge rectifying circuit connected to input and output terminals of the light emitting cell block, wherein the bridge rectifying circuit includes a plurality of diodes between nodes. In manufacturing an AC light emitting device with a bridge rectifying circuit built therein, the present invention can provide a light emitting device capable of enhancing the reliability and luminance of the light emitting device by setting the size of diodes of the bridge rectifying circuit to be a certain size and controlling the number thereof.

Owner:SEOUL VIOSYS CO LTD

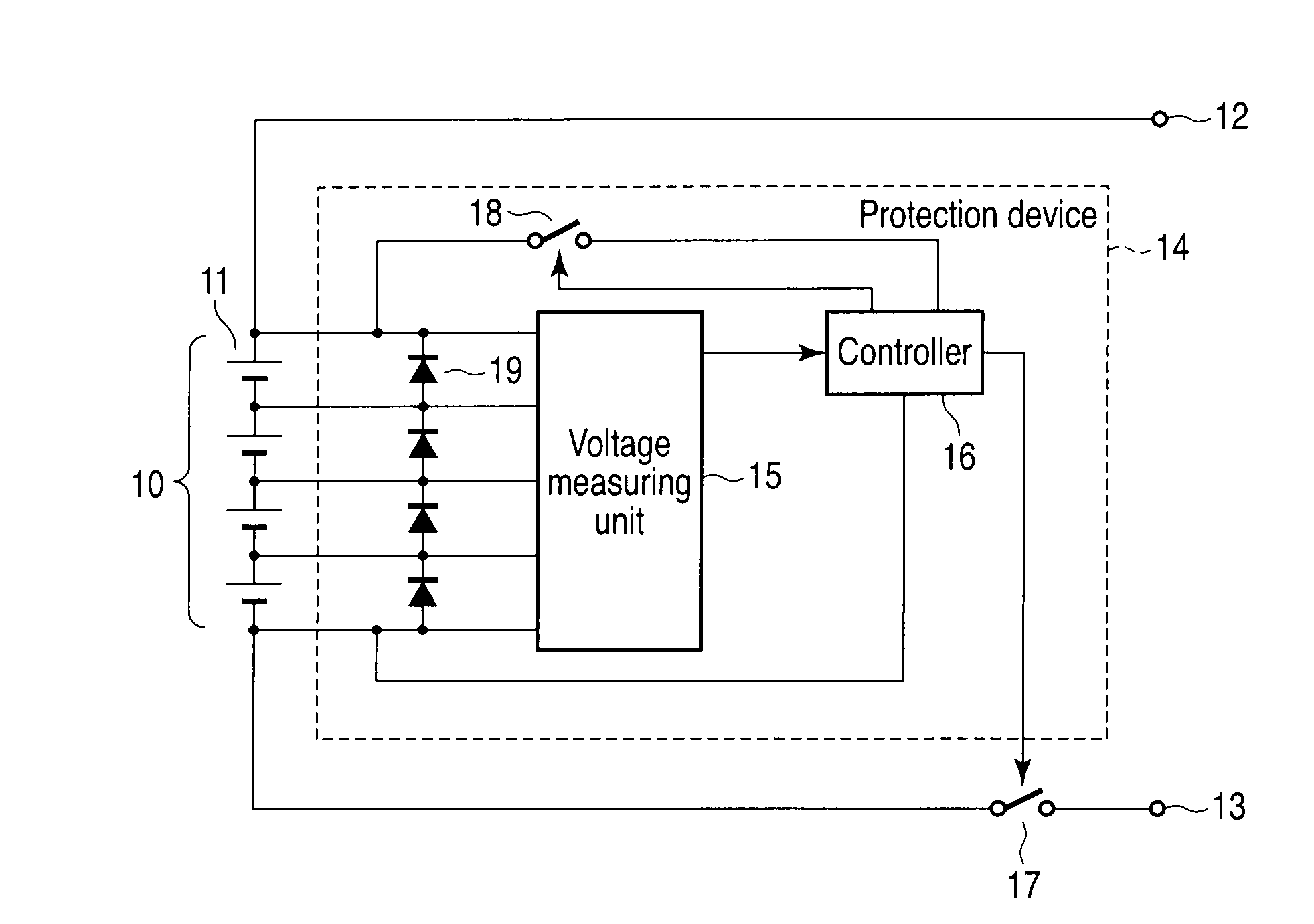

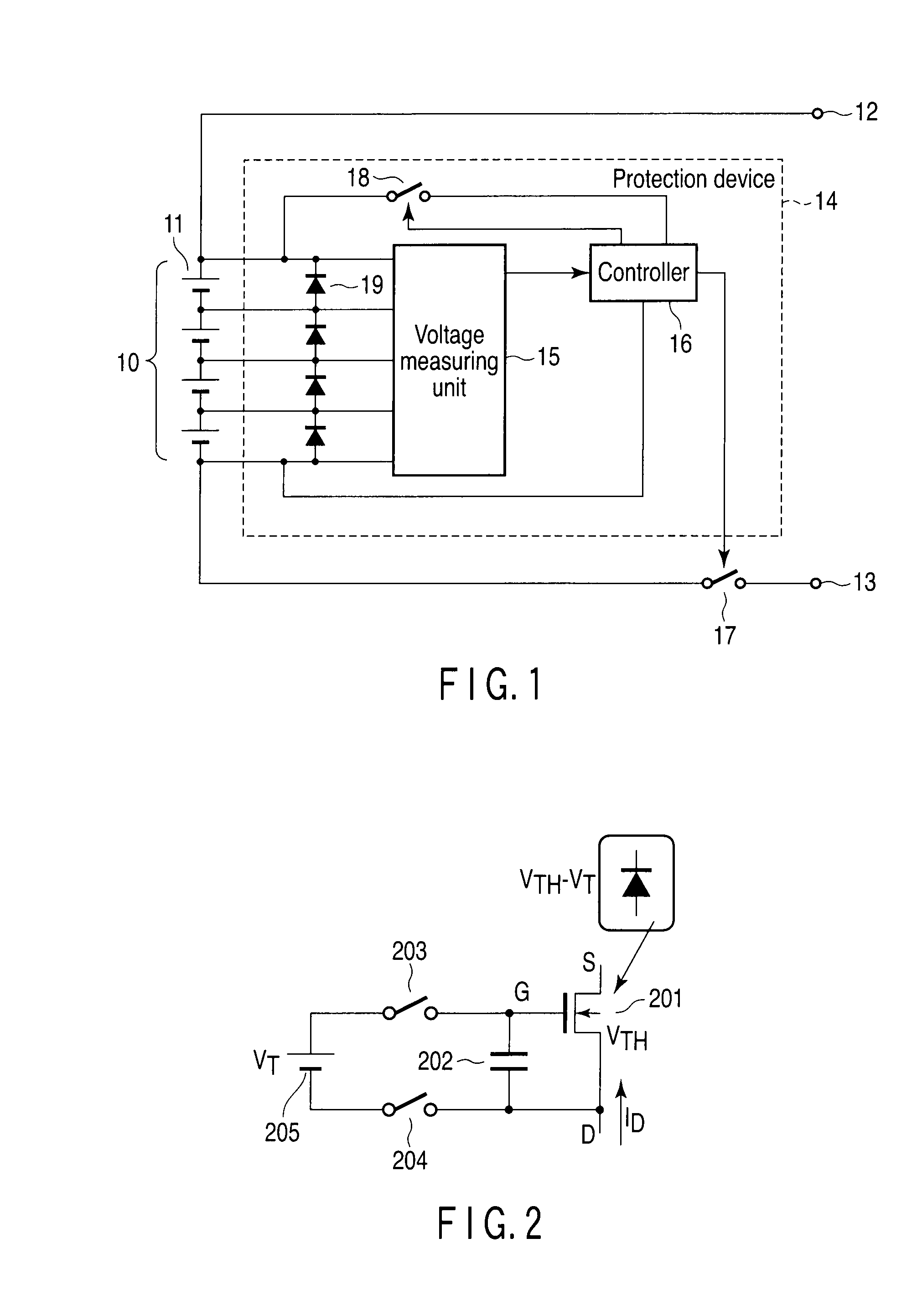

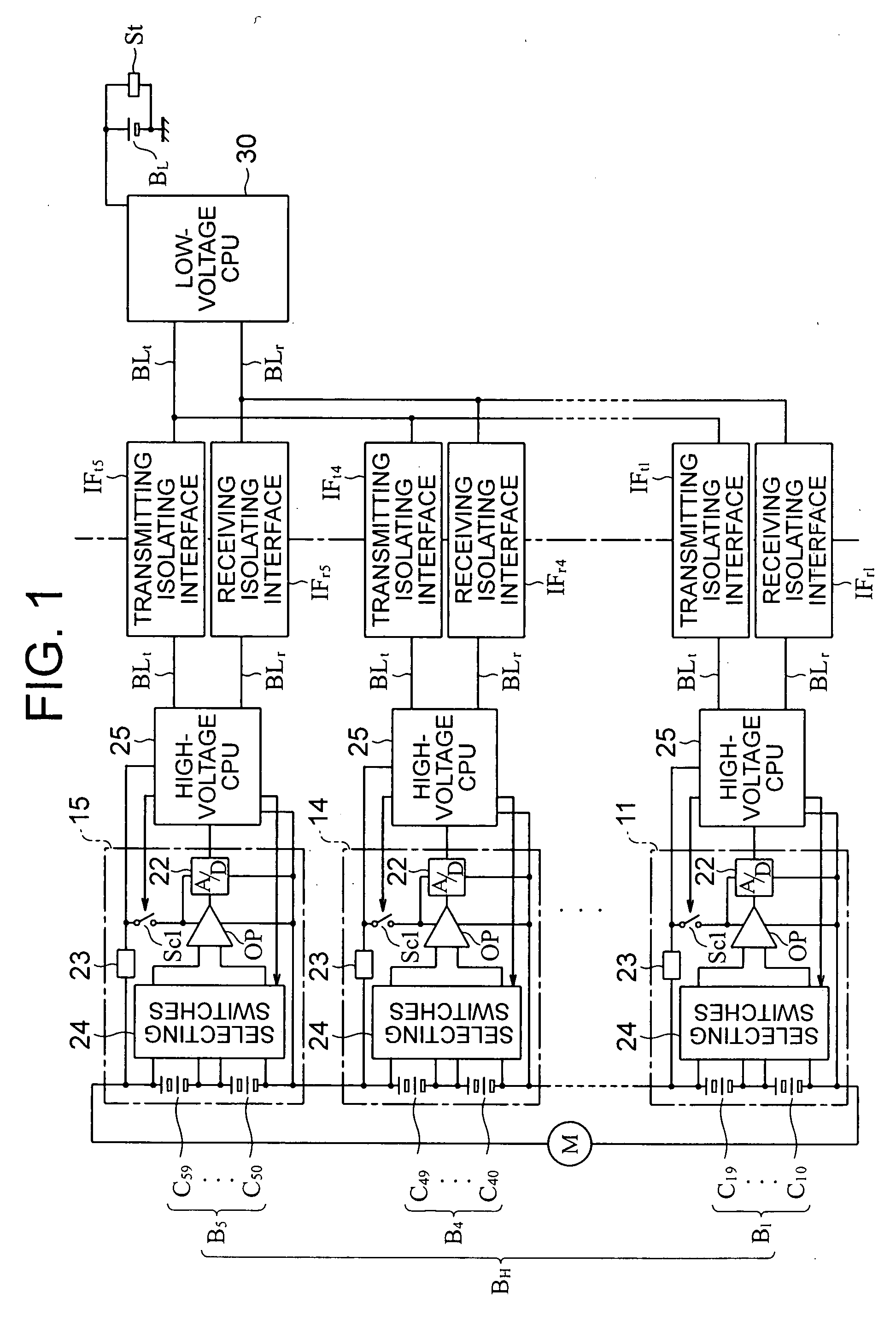

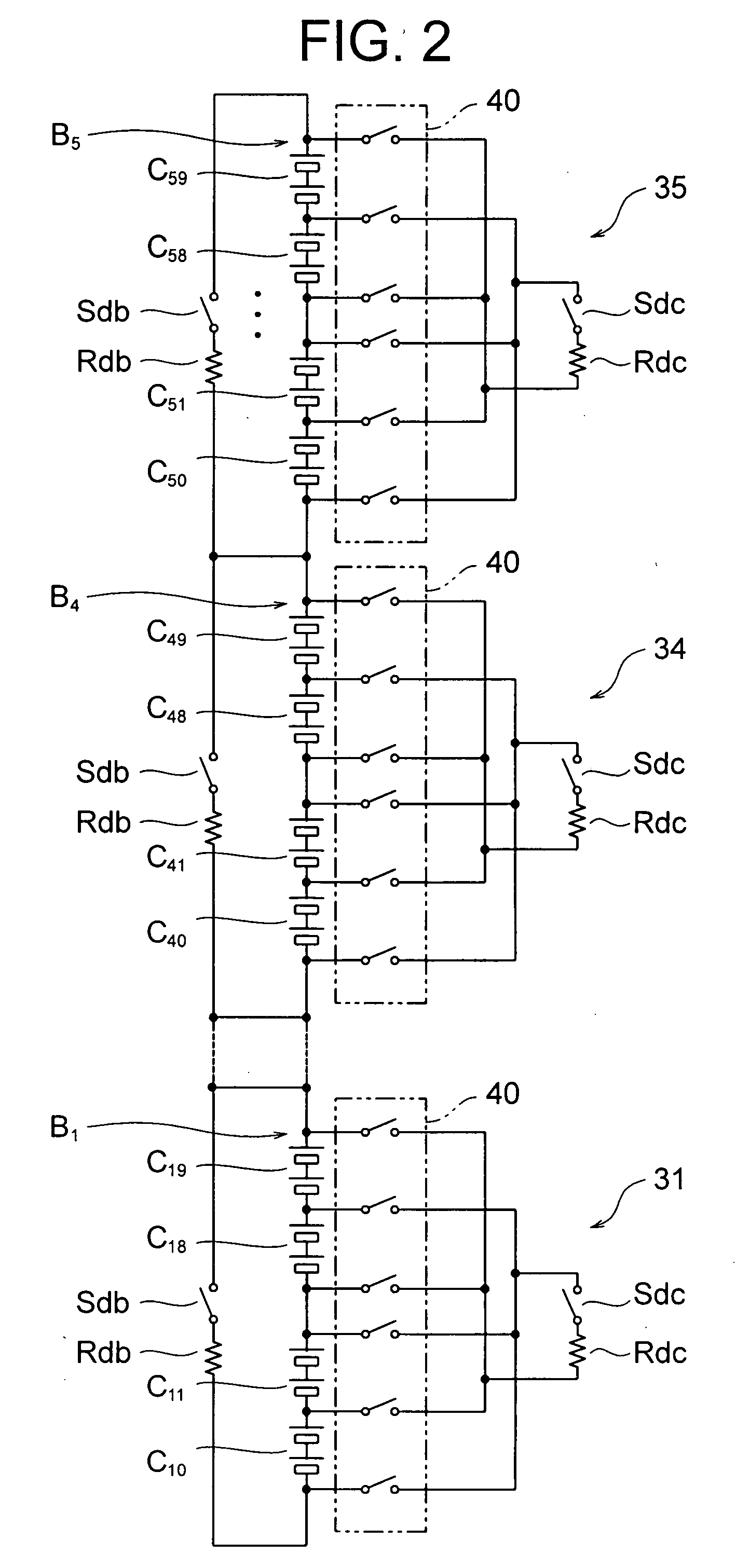

Assembled battery system and assembled battery protection device

An assembled battery system includes an assembled battery including a plurality of electric cell blocks connected in series, the electric cell blocks each including at least one nonaqueous electrolyte secondary battery provided with a negative electrode current collector formed of aluminum or an aluminum alloy, a voltage measuring unit configured to measure a plurality of voltages of the electric cell blocks, a controller which controls charge / discharge of the assembled battery in accordance with the measured voltages, and bypass circuits connected in parallel to the electric cell blocks, the bypass circuits each bypassing a current that flows from a negative electrode of one of the electric cell blocks to a positive electrode of the one of electric cell blocks when the measured voltage of the one of electric cell blocks is a negative value not greater than a threshold value.

Owner:KK TOSHIBA

Optimized battery performance

InactiveUS20050116686A1Improve the level ofPrimary cell to battery groupingSequential battery dischargeBattery cellBattery pack

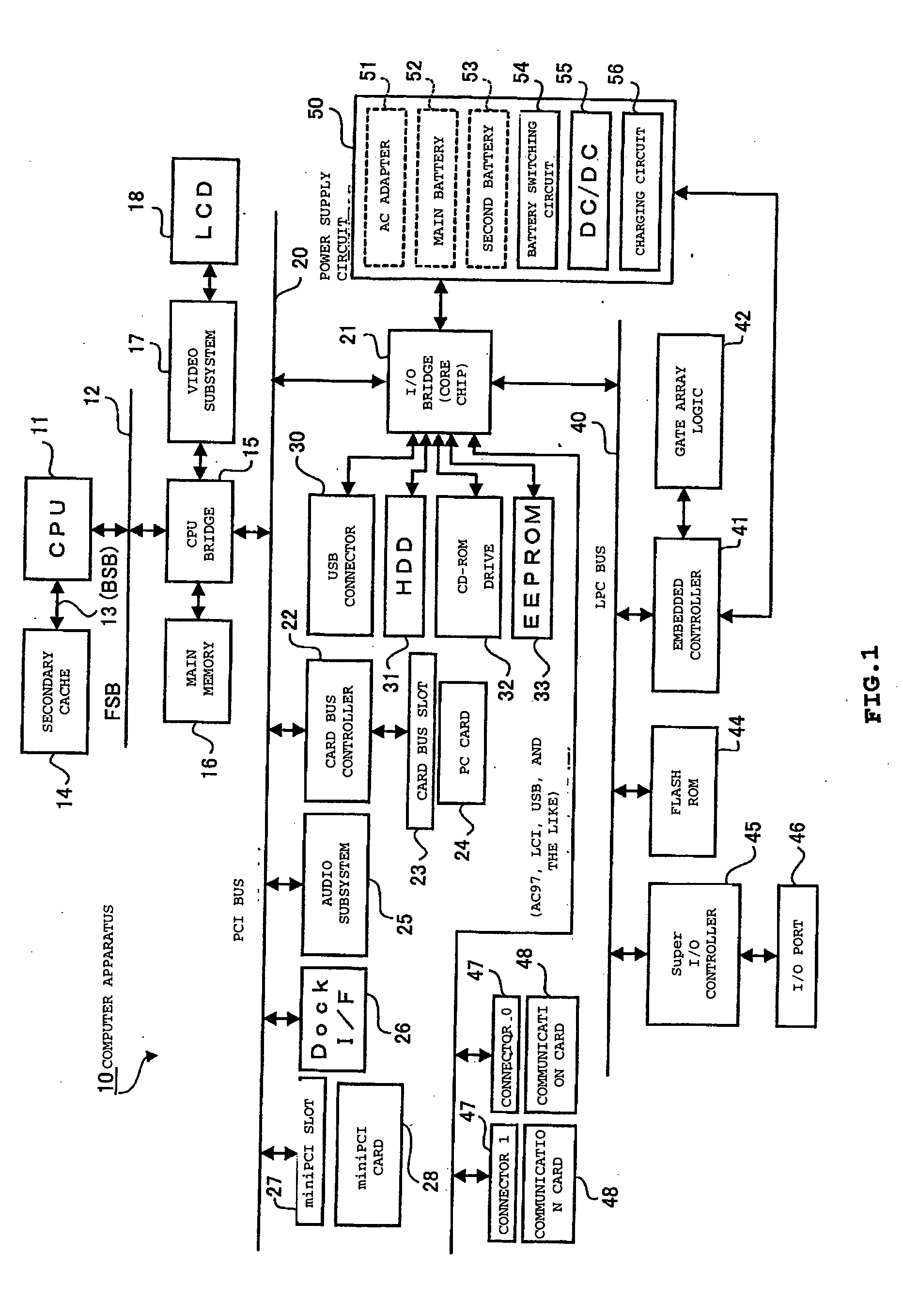

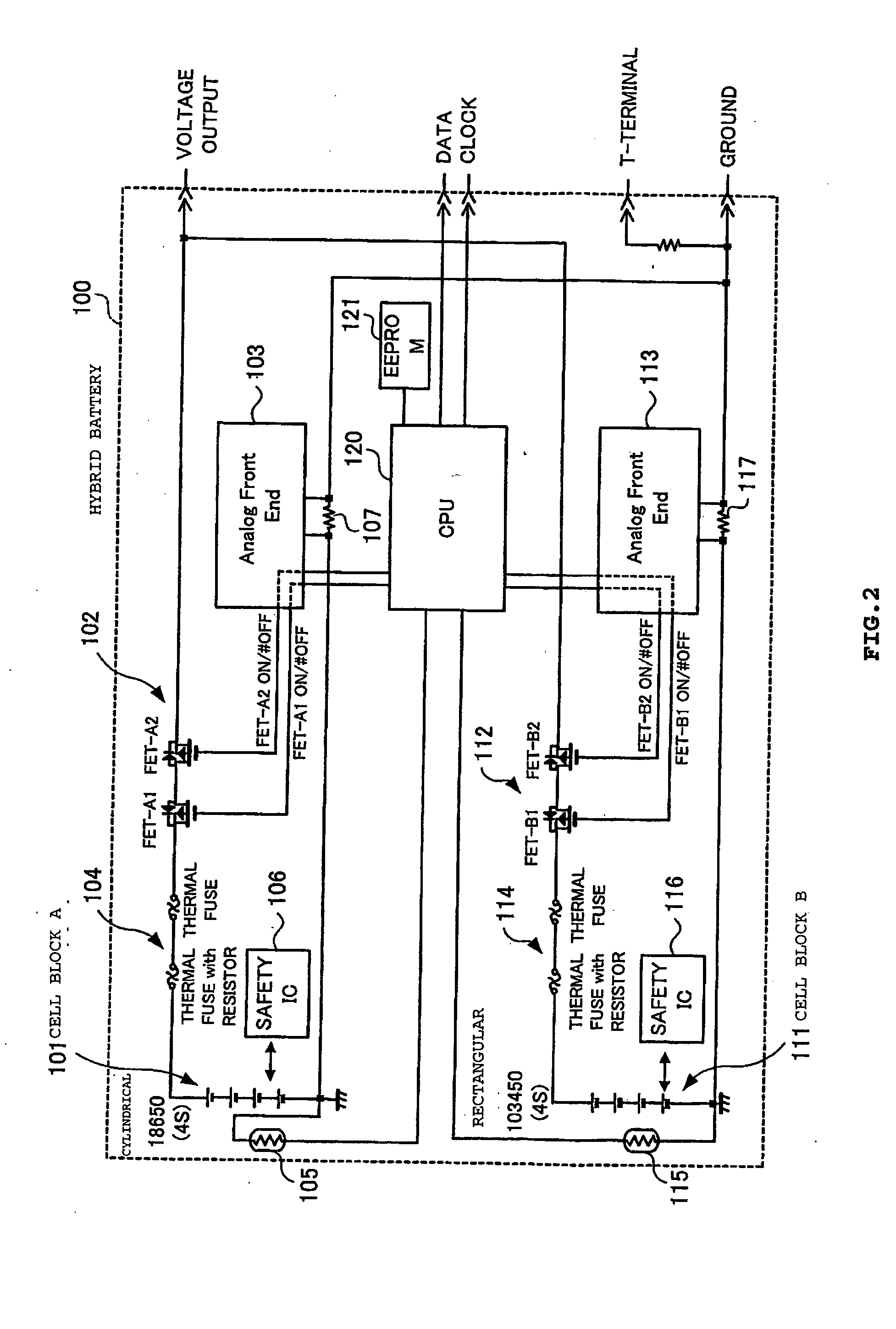

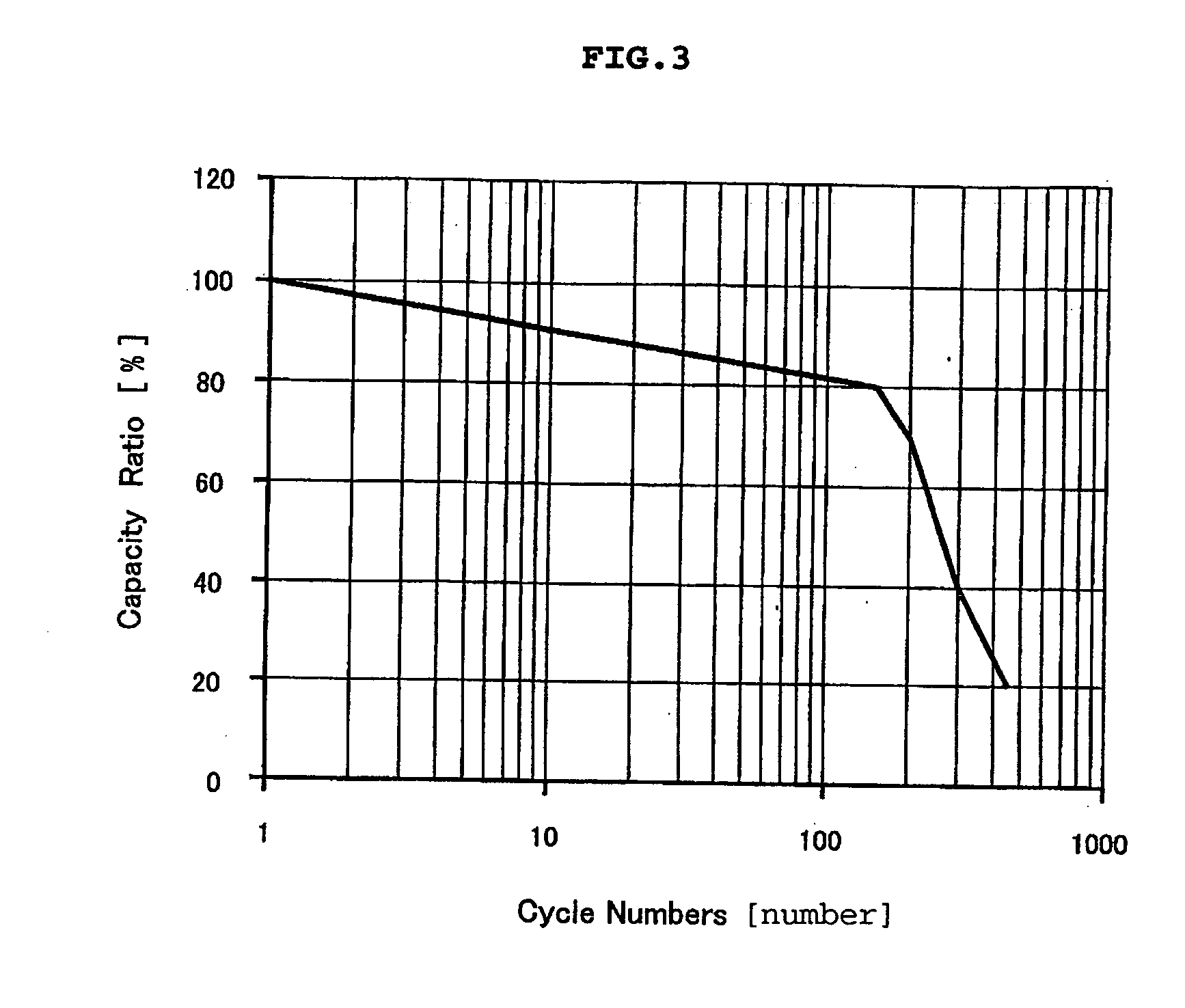

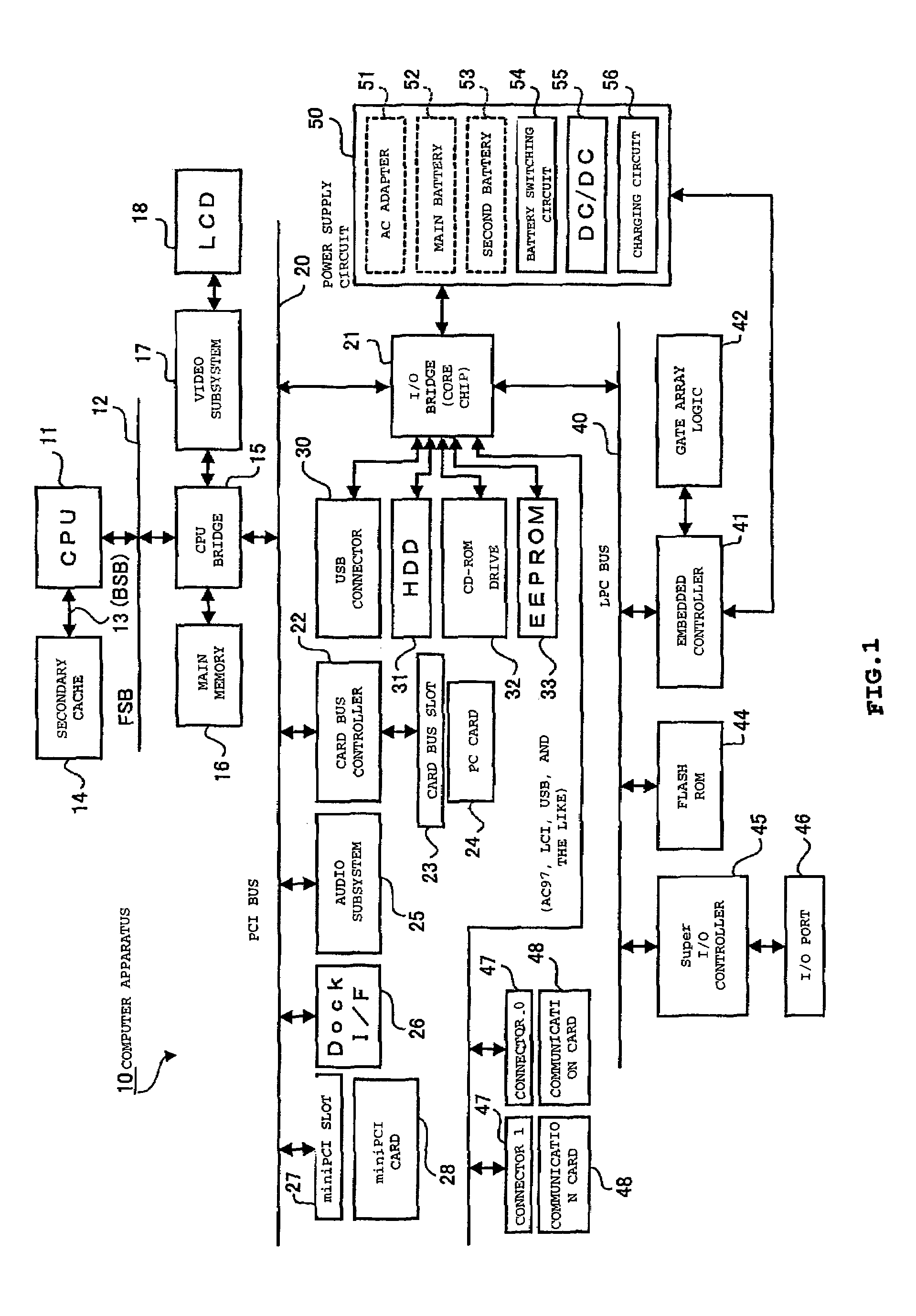

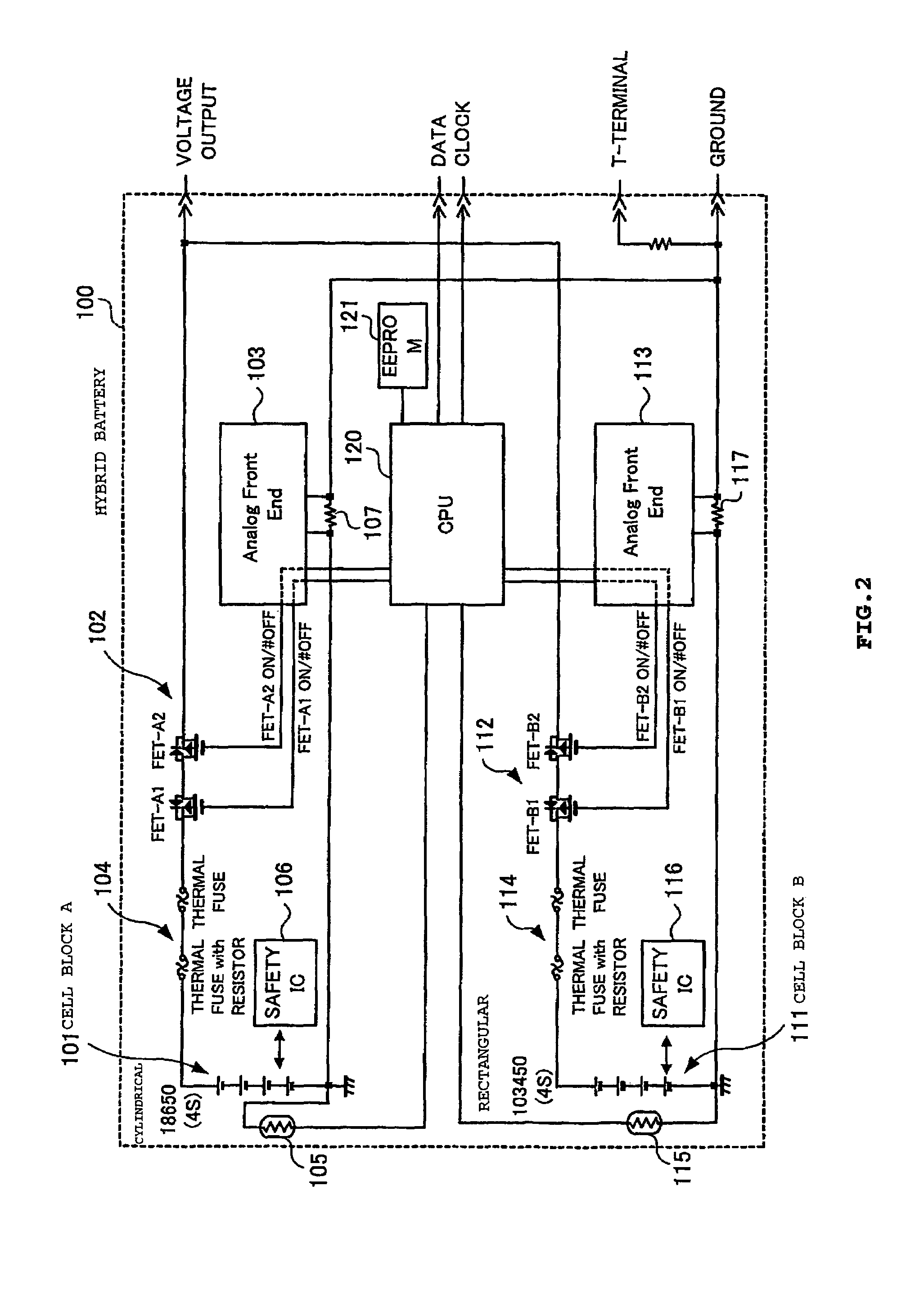

In an electrical instrument to which a plurality of battery blocks and / or a plurality of batteries are detachably connectable, to prevent a phenomenon that only specific battery and battery block are deteriorated. A hybrid battery connectable to a body of an electrical instrument consuming electrical power includes: a cell block which includes one or more battery cells, and supplies electrical power to the body of the electrical instrument by discharging after being charged; and a cell block which includes one or more battery cells, supplies electrical power to the body of the electrical instrument by discharging after being charged, and becomes active selectively with the former cell block. In the hybrid battery, a CPU selects a cell block becoming active based on the number of charge / discharge cycles of the former cell block and the number of charge / discharge cycles of the latter cell block.

Owner:LENOVO GLOBAL TECH INT LTD

Nonvolatile ferroelectric memory

According to an aspect of the invention, there is provided a nonvolatile ferroelectric memory, including a ferroelectric capacitor composed of a ferroelectric film sandwiched by capacitor electrodes made of a conductive material, a cell capacitor block stacked a plurality of the capacitor electrodes and the ferroelectric film of the ferroelectric capacitor perpendicular to a main surface of a silicon substrate in layer, a cell transistor having a drain electrode and a source electrode, the drain electrode and the source electrode are electrically connected to the ferroelectric capacitor in parallel, a memory cell composed of the ferroelectric capacitor and the cell transistor, a cell block having the plurality of memory cells electrically connected in series, the drain electrode and the source electrode being as a terminals, a word line, a bit line connected to one end of the cell block, the bit line being arranged along orthogonal direction to the word line and a plate line connected to the other end of the cell block, the plate line arranged along the word line.

Owner:KIOXIA CORP

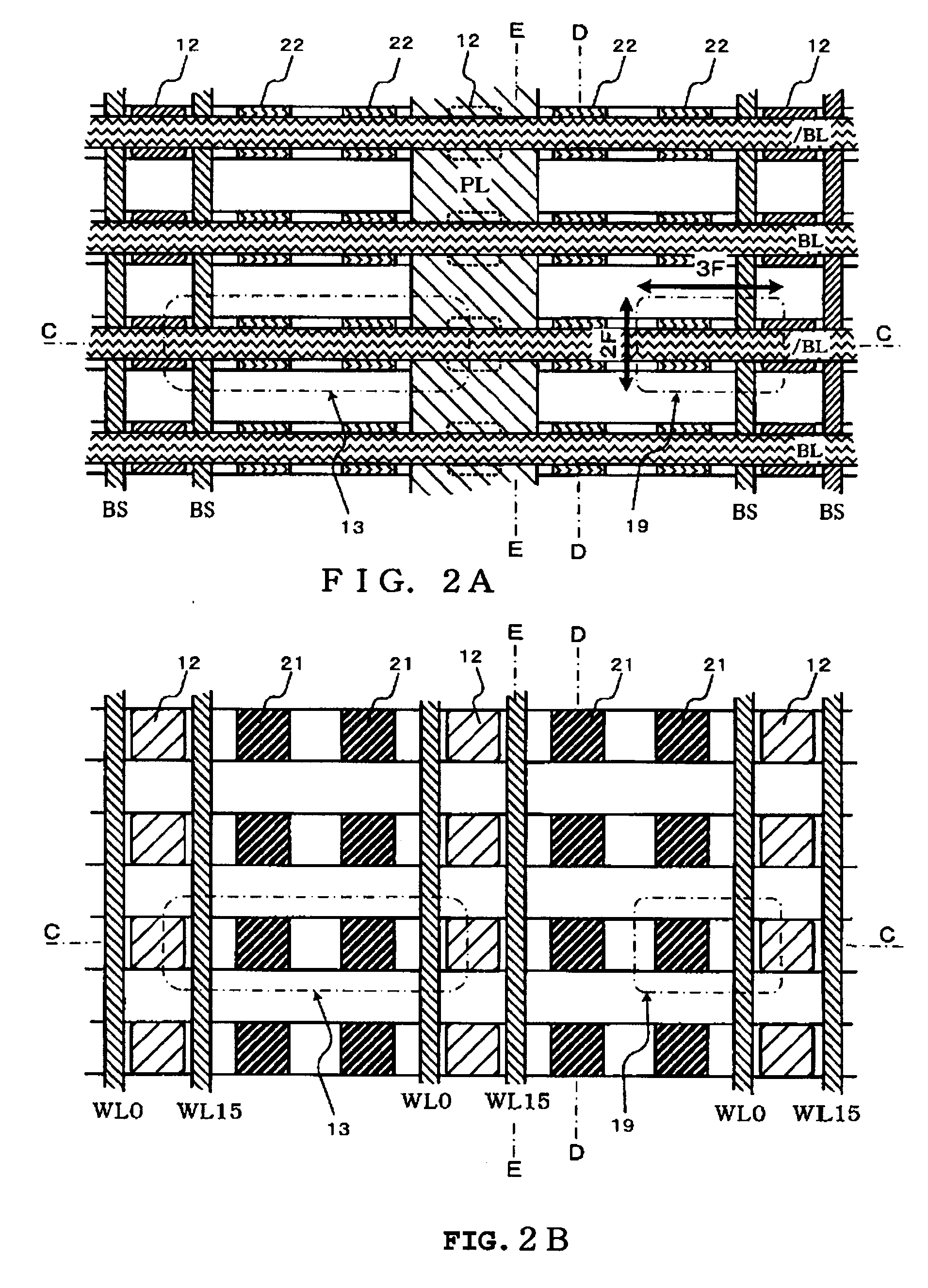

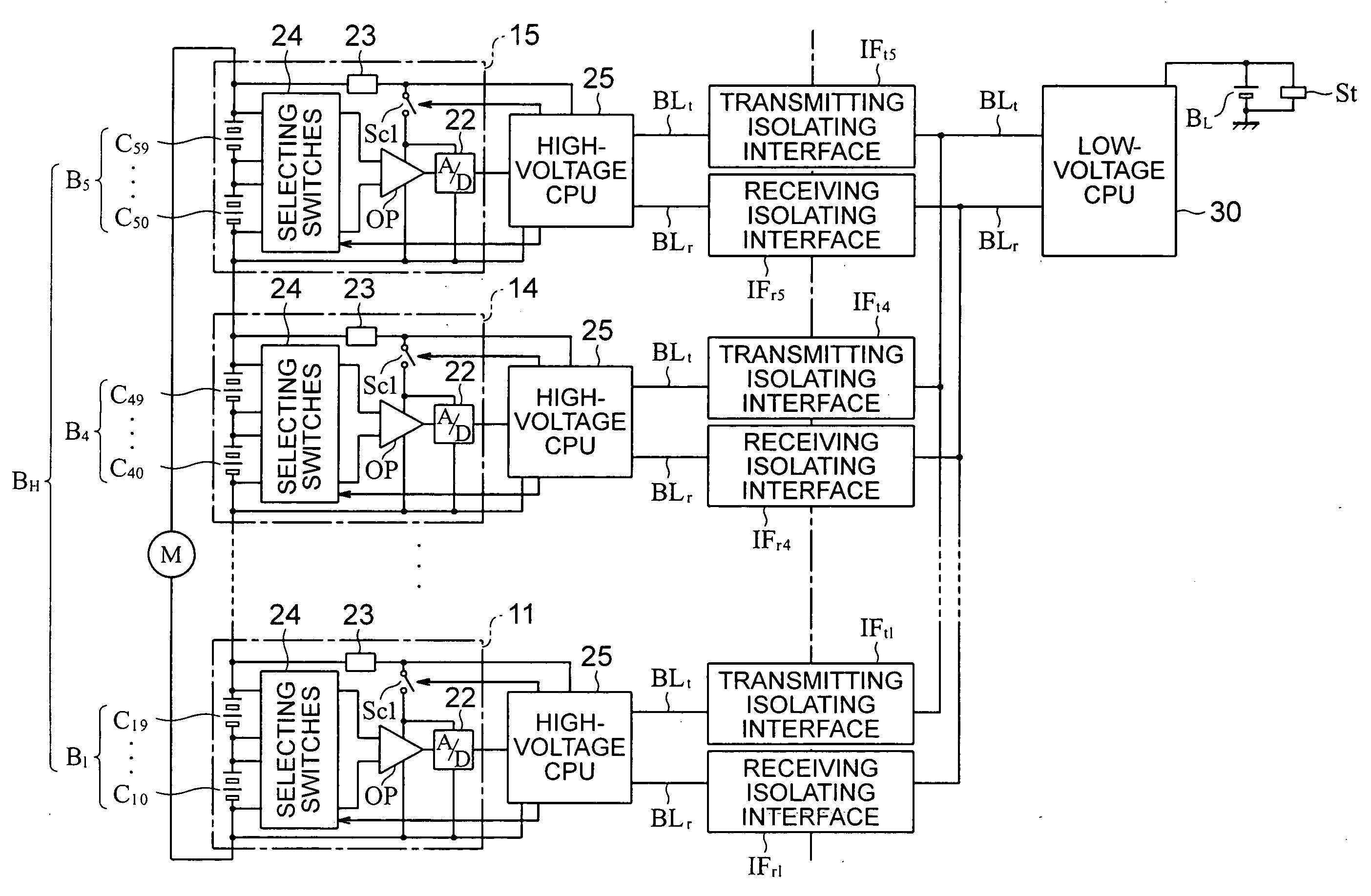

Charge condition adjusting apparatus

ActiveUS20070247115A1Shorten equalization timeFast equalizationCharge equalisation circuitElectrical testingLow voltageElectrical battery

Providing a charge condition adjusting apparatus, which can shorten a time for equalization of each charge in unit cells, a low-voltage CPU selects each smallest unit cell in the each cell block, which has each smallest voltage between the both electrodes, from among plural unit cells structuring the cell blocks. The low-voltage CPU controls ON / OFF of a block-discharging switch to connect the both electrodes of each cell block and each block-discharging resistor for discharging the each cell block until the each voltage between the both electrodes of the selected smallest unit cell reaches the target voltage. Successively, the low-voltage CPU controls ON / OFF of a selecting switches and a cell-discharging switch to connect the both electrodes of each unit cell and each cell-discharging resistor to discharge the each unit cell until the each voltage between the both electrodes of the unit cells reaches the target voltage.

Owner:YAZAKI CORP

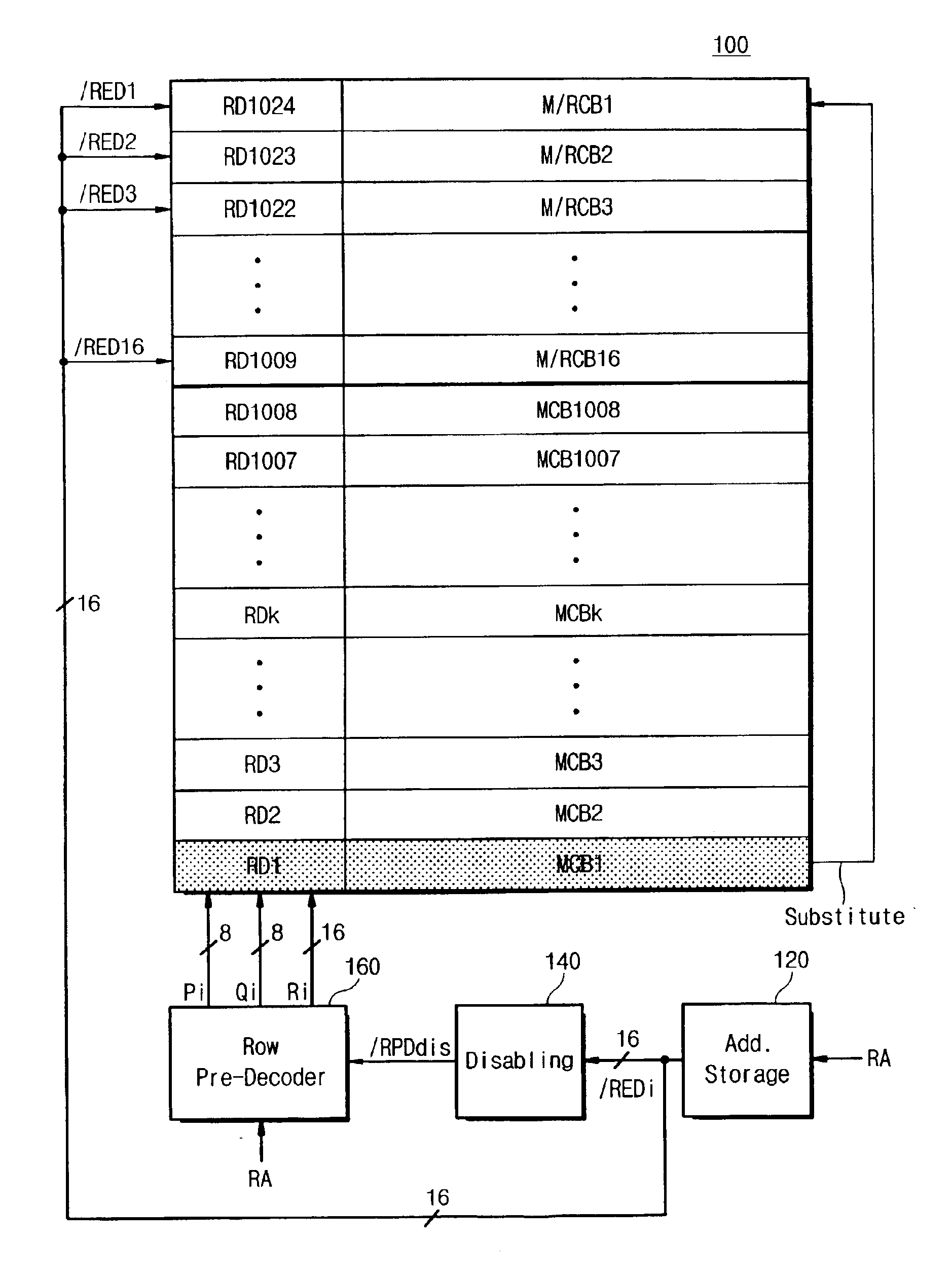

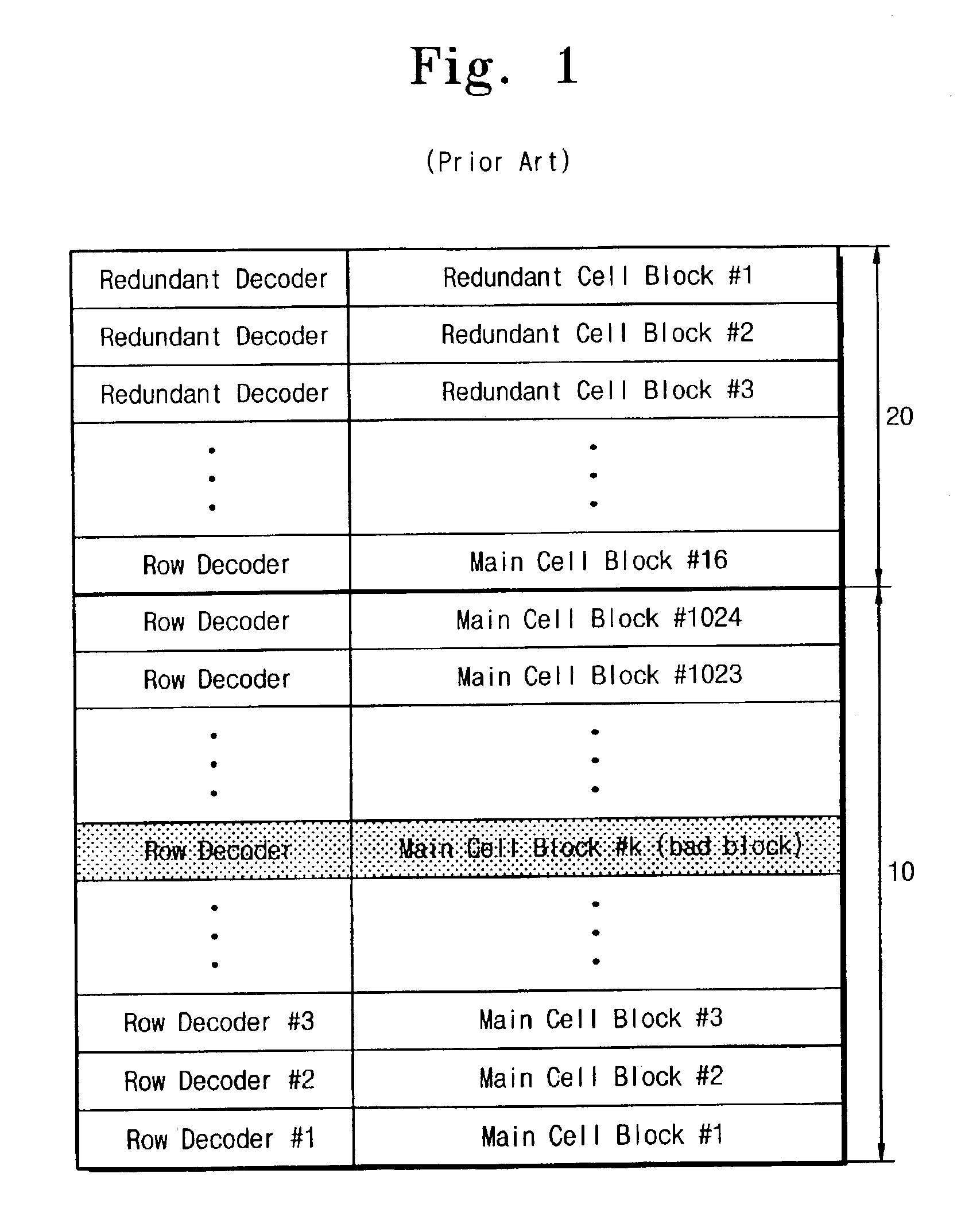

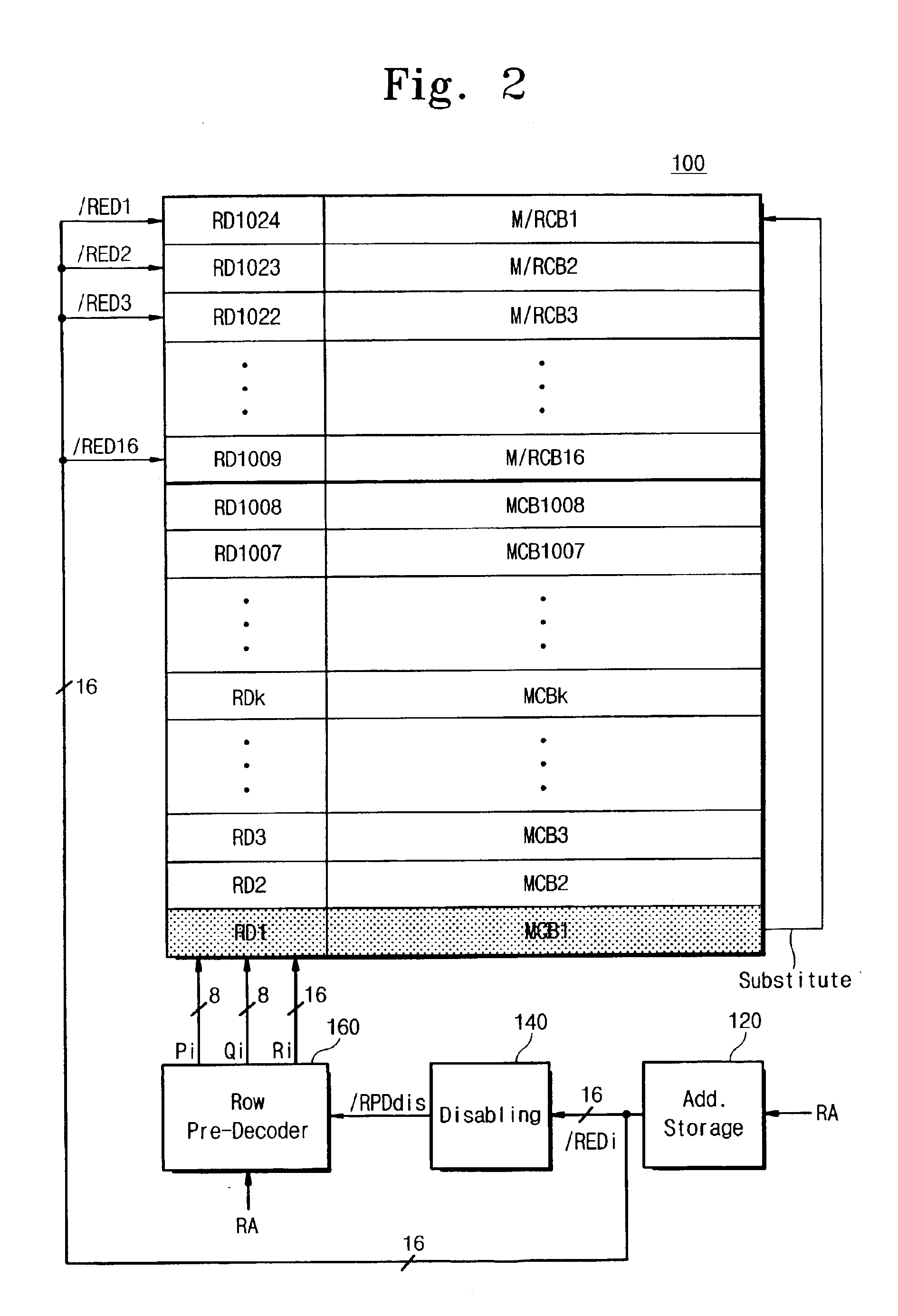

Semiconductor memory device with a flexible redundancy scheme

A semiconductor memory device including an array with a first memory cell block having redundancy blocks and a second memory cell block having normal blocks. A redundancy block in the first memory cell block is substituted for a defective normal block in the second memory cell block. The substitution is performed by a block selection circuit. When substitution is required, the block selection circuit selects from among the first memory cell blocks in inverse order, beginning with the first memory cell block having the highest address. First memory cell blocks that are not substituted for defective cell blocks are used as normal memory cell blocks by the block selection circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

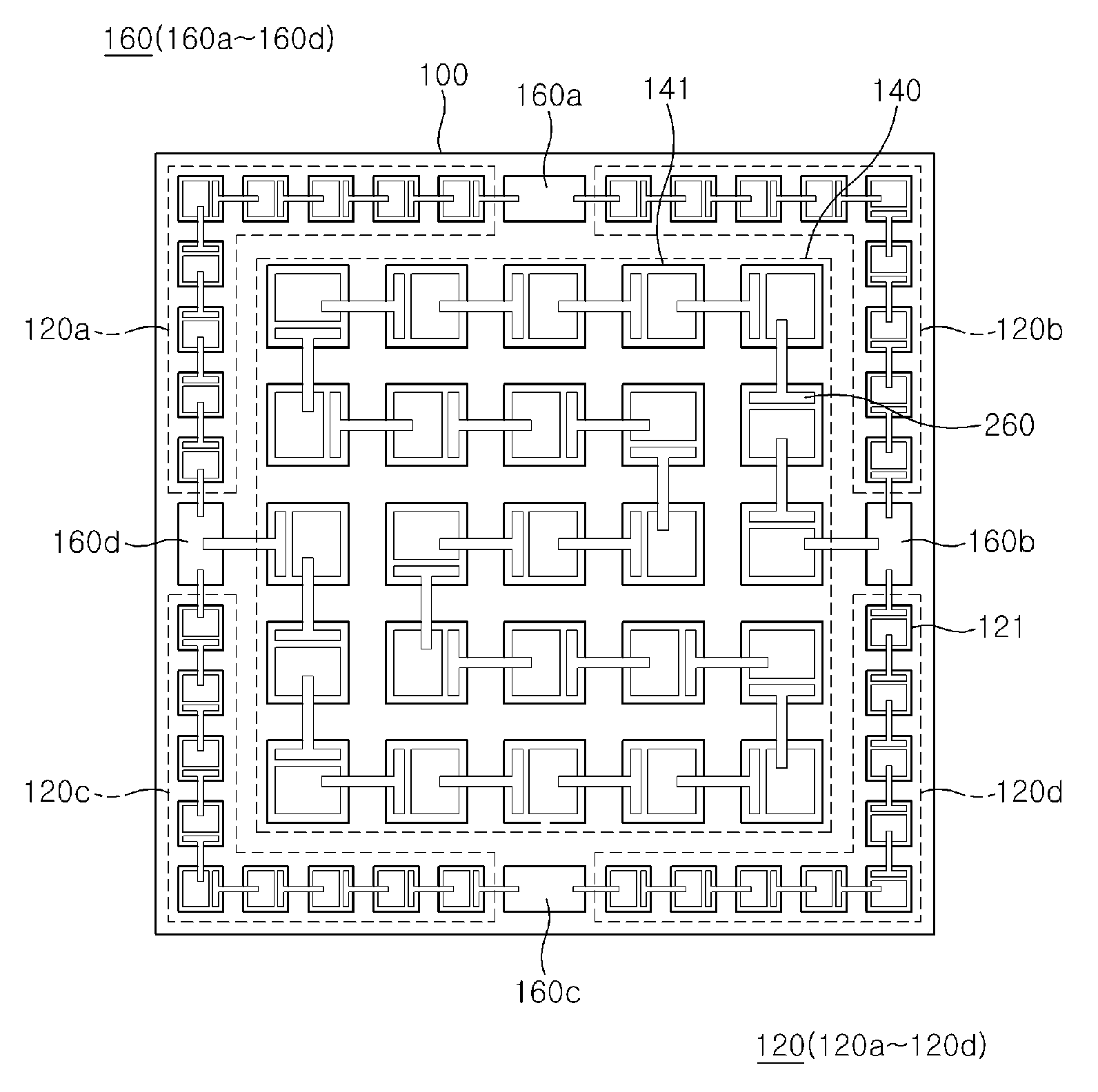

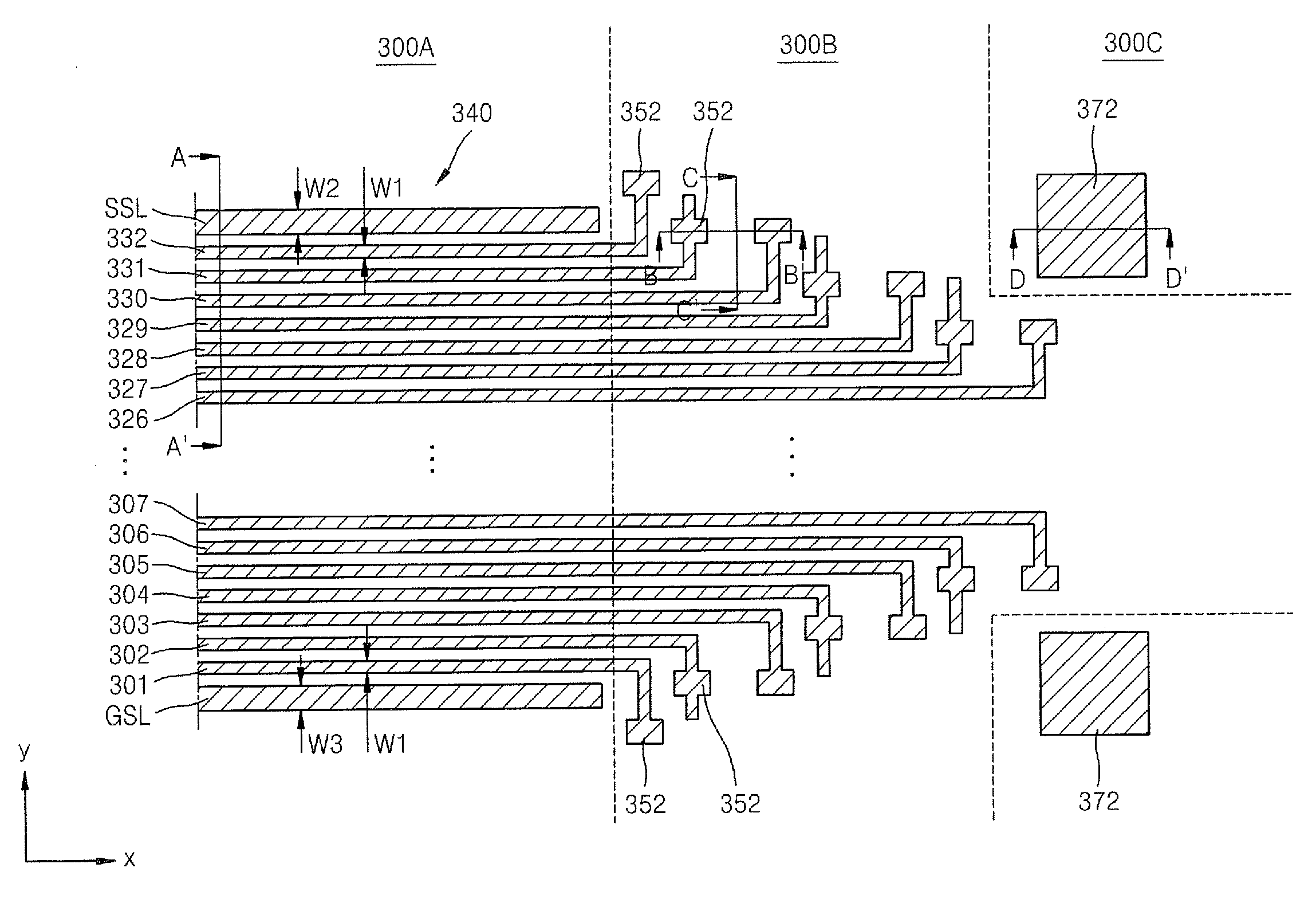

Method of forming fine patterns of semiconductor device

ActiveUS20090263749A1Simplifying trimming processHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingContact padDevice material

A method of forming fine patterns of a semiconductor device, in which a plurality of conductive lines formed in a cell array region are integrally formed with contact pads for connecting the conductive lines to a peripheral circuit. In this method, a plurality of mold mask patterns, each including a first portion extending in a first direction and a second portion which is integrally formed with the first portion and extends in a second direction, are formed within a cell block on a substrate comprising a film which is to be etched. A first mask layer covering sidewalls and an upper surface of each of the plurality of mold mask patterns is formed on the substrate. First mask patterns are formed by partially removing the first mask layer so that a first area of the first mask layer remains and a second area of the first mask layer is removed. The first area of the first mask layer covers sidewalls of adjacent mold mask patterns from among the plurality of mold mask patterns by being located between the adjacent mold mask patterns, and the second area of the first mask layer covers portions of the sidewalls of the plurality of mold mask patterns, the portions corresponding to an outermost sidewall of a mold mask pattern block.

Owner:SAMSUNG ELECTRONICS CO LTD

Two-dimension bar code system and its positioning method

ActiveCN101430768ASmall footprintLarge information capacityCharacter and pattern recognitionRecord carriers used with machinesPattern recognitionGraphics

The invention discloses a 2D bar code system and a locating method thereof. A code word is formed by arranged quadrate cell blocks, and a code word area is divided into a locating area, a spacer area, a data area and a pattern area. A sampled and preprocessed digital image signal is binarized by a maximum between-cluster variance algorithm; and a plurality of deep-color and light-color connected domains are obtained by a fast filling algorithm; a plurality of dead square deep-color and light-color connected domains are selected according to a shape factor and an area factor; then concentric selection is performed to obtain a plurality of candidate location graphs; in succession, square topologic selection is performed to determine an effective code word area, and finally, the space is sampled, thus achieving 2D code location.

Owner:成都市思博睿科技有限公司

Cell voltage detection device and cell system using the same

InactiveUS20070202371A1Prevent false detectionBatteries circuit arrangementsFuel cells groupingFuel cellsCell system

A fuel cell detection device according to the present invention includes: a cell block formed with a plurality of cells serially connected to each other; a voltage detection element for detecting voltages of the cells within the cell block; and another voltage detection element for detecting a voltage of the operating power source of the voltage detection element, where the operating power source of the voltage detection element is supplied from a voltage of the inside or both ends of the cell block, and the operating power source of another voltage detection element is supplied from a voltage of the outside of the cell block, the operating power source of another voltage detection element being less variable than the operating power source of the voltage detection element.

Owner:HITACHI LTD

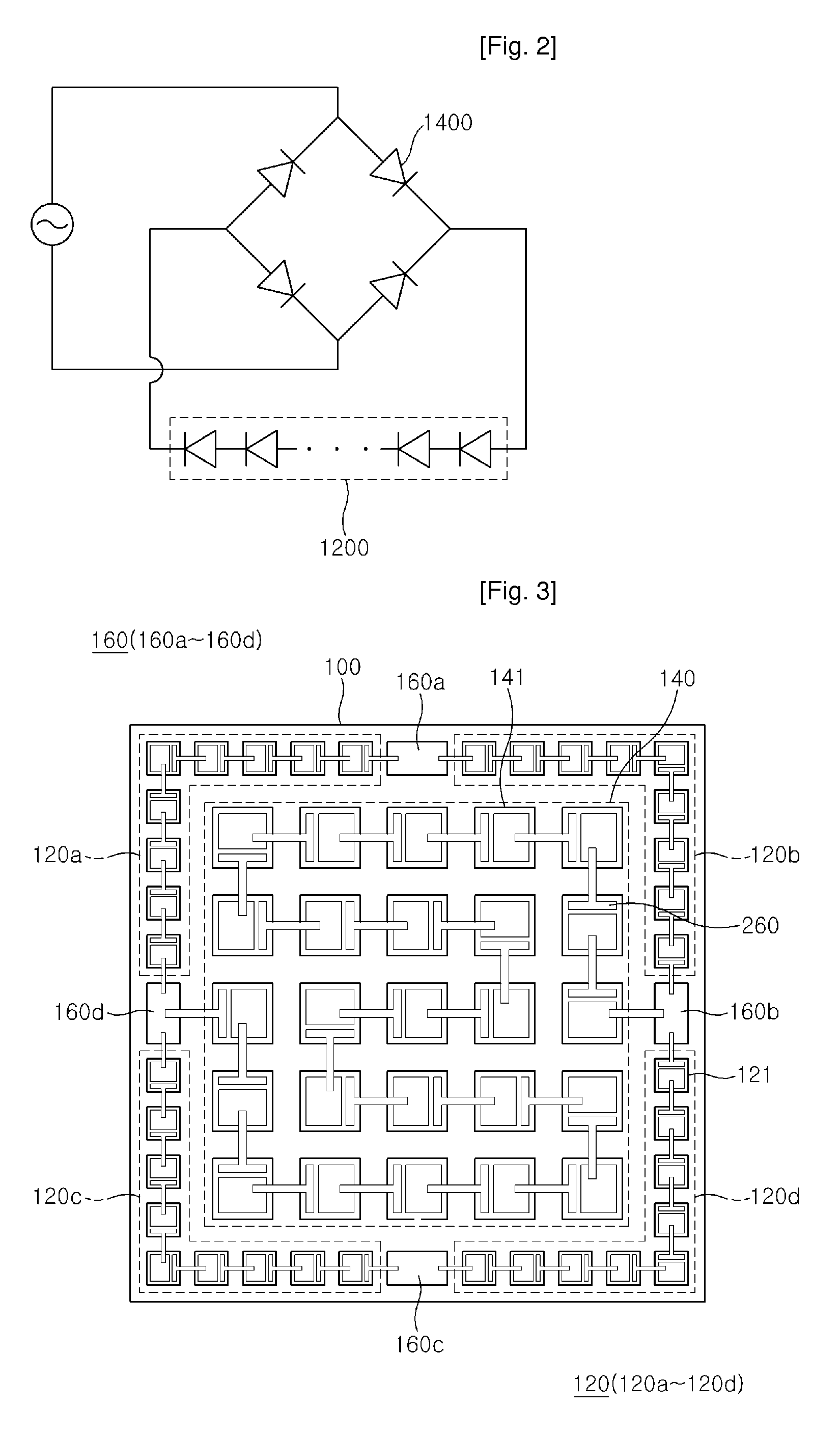

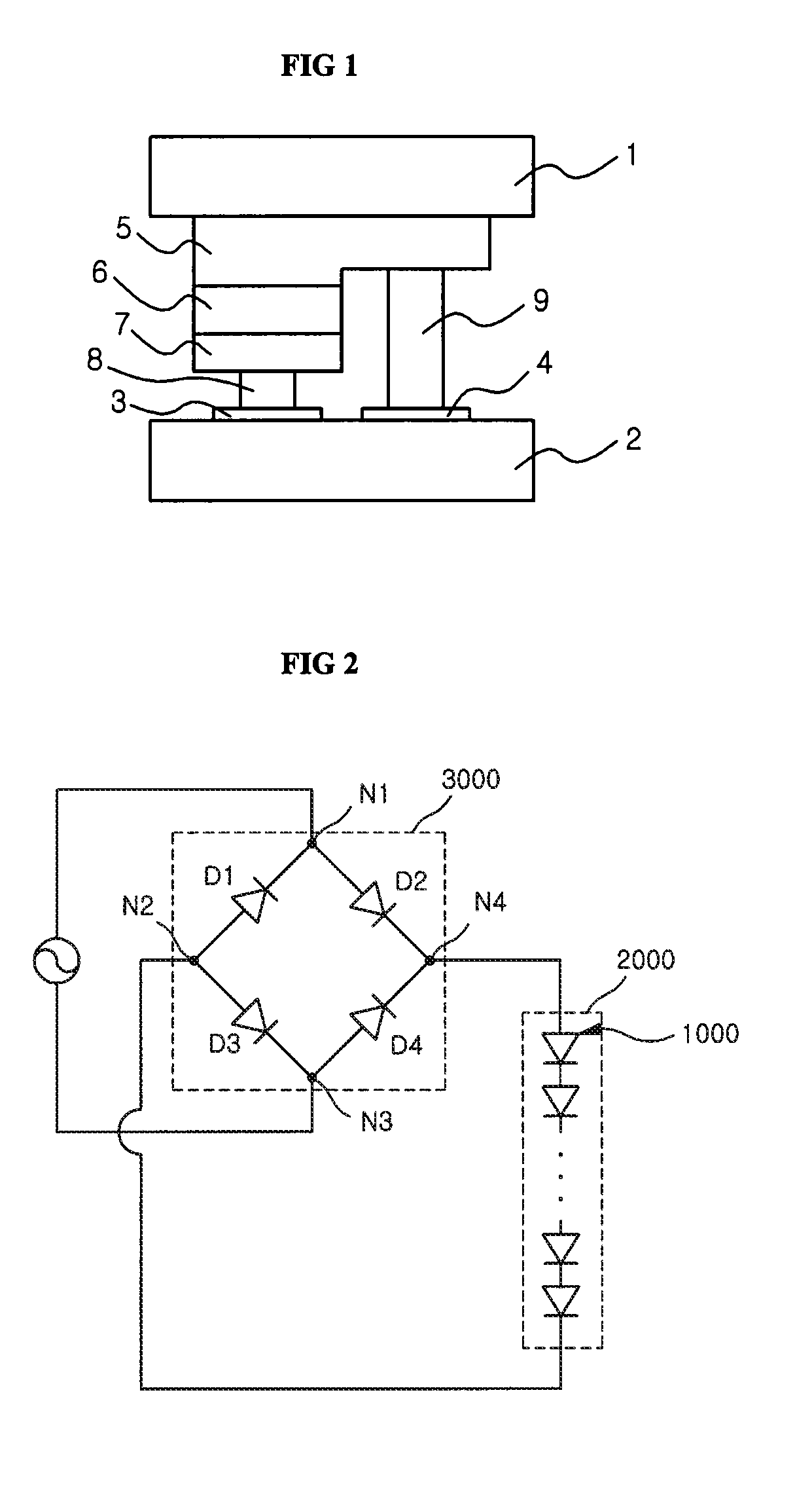

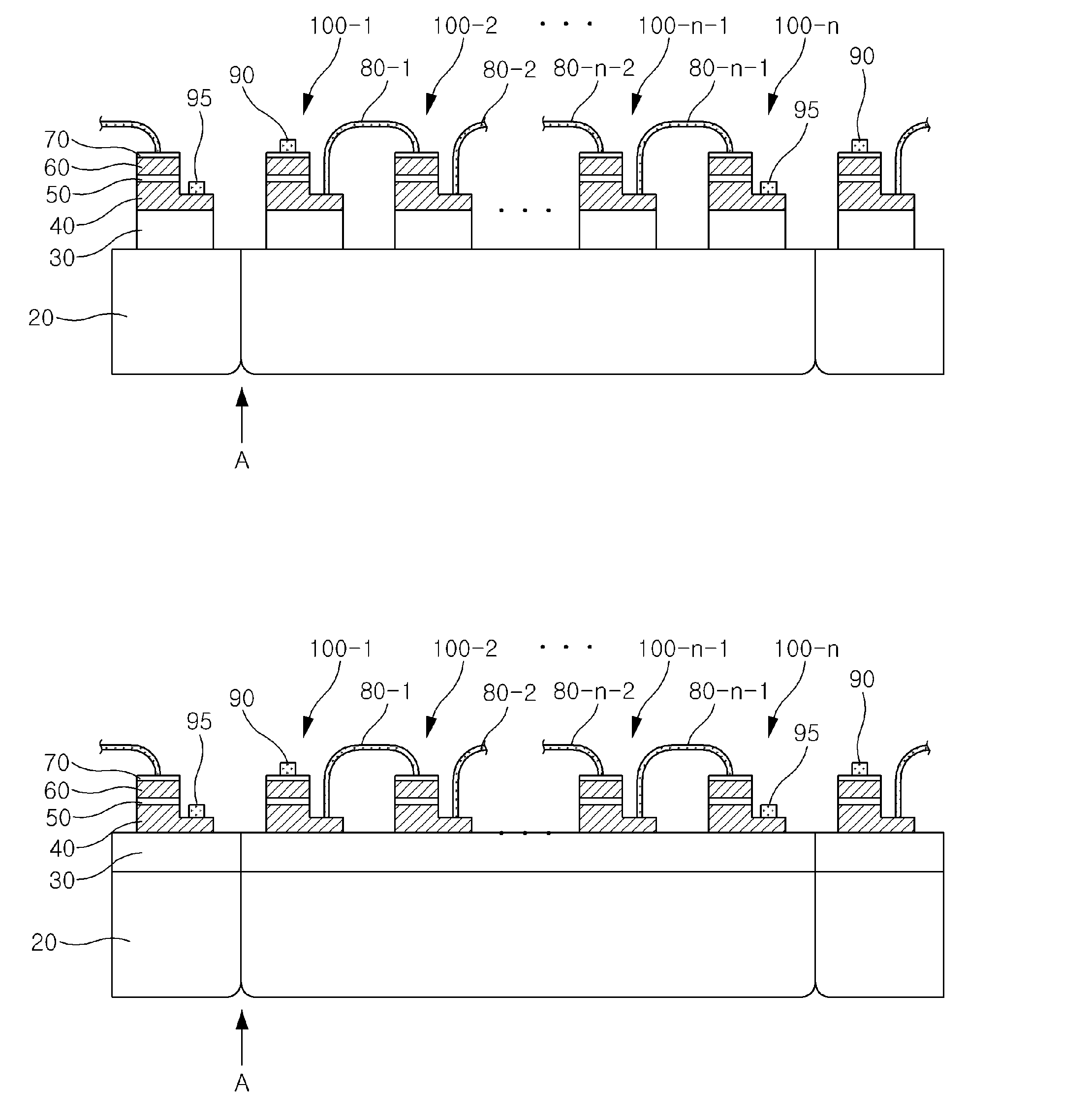

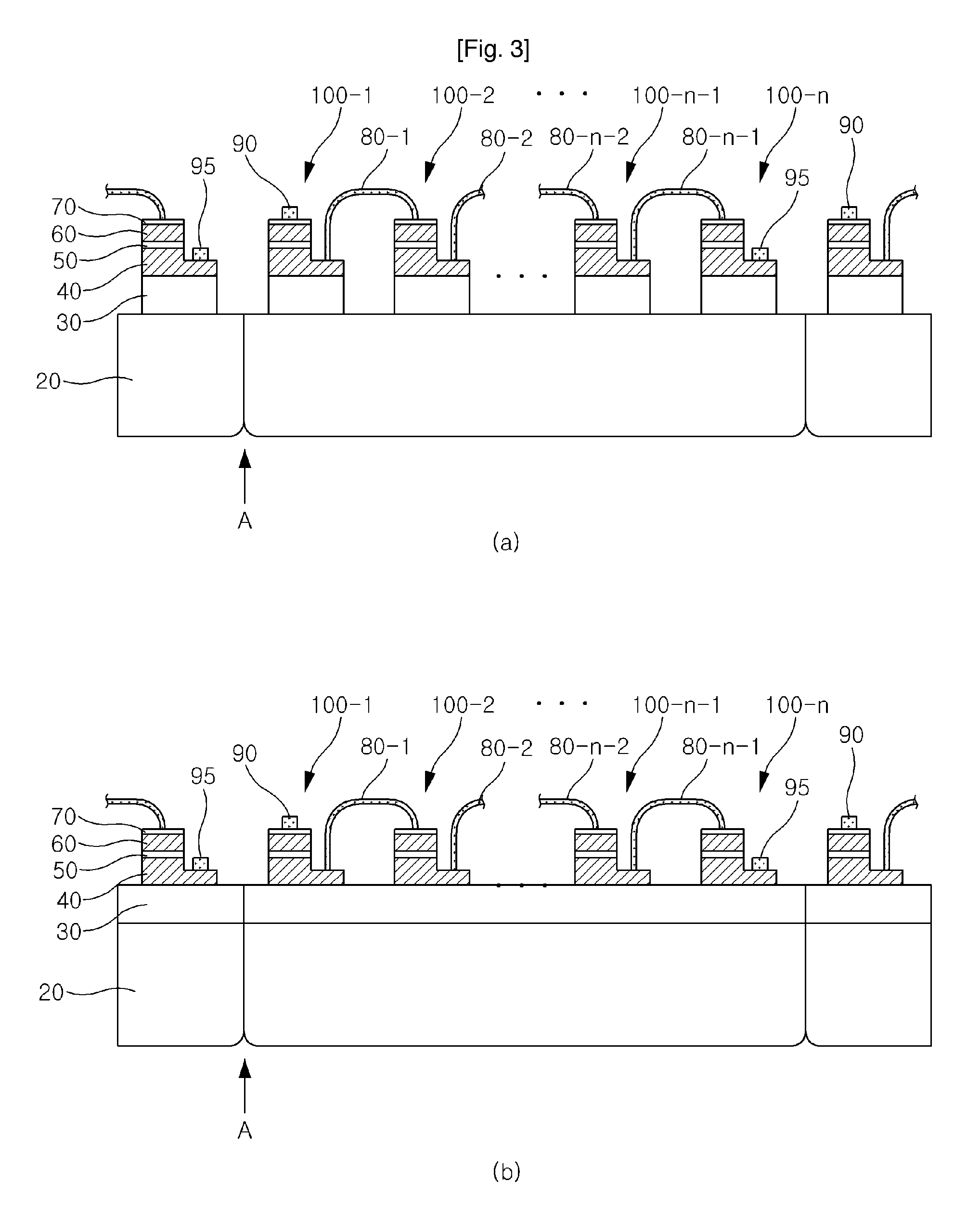

Light Emitting Device and Method of Manufacturing the Same

InactiveUS20080191632A1Semiconductor/solid-state device detailsSolid-state devicesVoltage variationAC power

The present invention provides a light emitting device comprising a first semiconductor substrate including a light emitting cell block having a plurality of light emitting cells connected in series on one surface thereof; a second semiconductor substrate having one surface formed with a rectifying bridge and the other surface bonded to the other surface of the first semiconductor substrate; and a submount substrate to which the second semiconductor substrate is flip-chip bonded to be in contact with the one surface of the second semiconductor substrate, wherein rectified power is applied to the light emitting cell block through the rectifying bridge. The present invention further provides a method of manufacturing the light emitting device. The light emitting device and the method of manufacturing the same according to the present invention have advantages in that a flicker effect generated from an AC power source can be minimized and constant brightness can be maintained even in changes in the voltage of the AC power source by integrating a rectifying circuit into a light emitting device with a flip-chip structure, and in that there is no cumbersomeness of mounting an additional auxiliary device, resulting in increase of the degree of utilization of space and improved light output.

Owner:SEOUL VIOSYS CO LTD

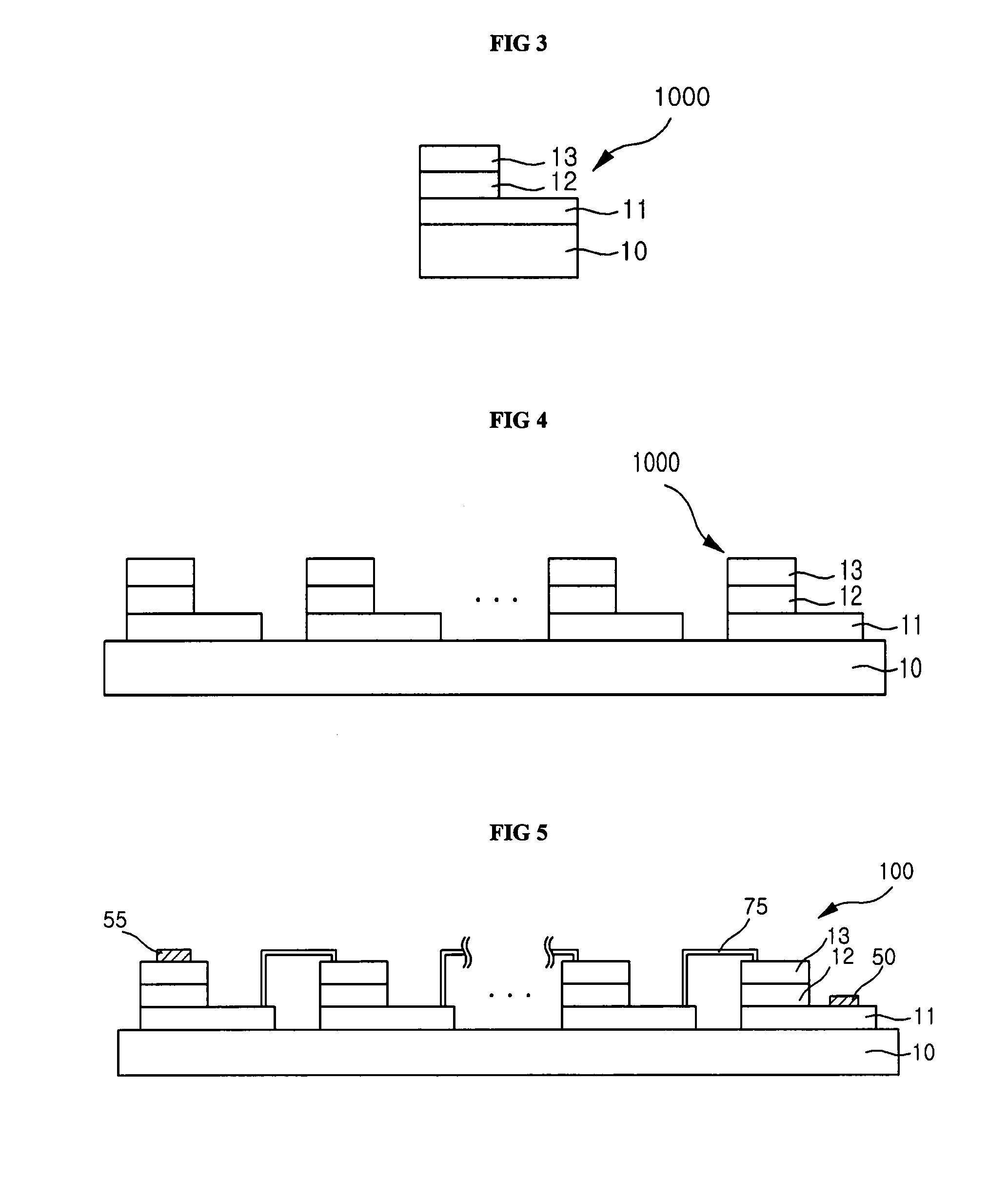

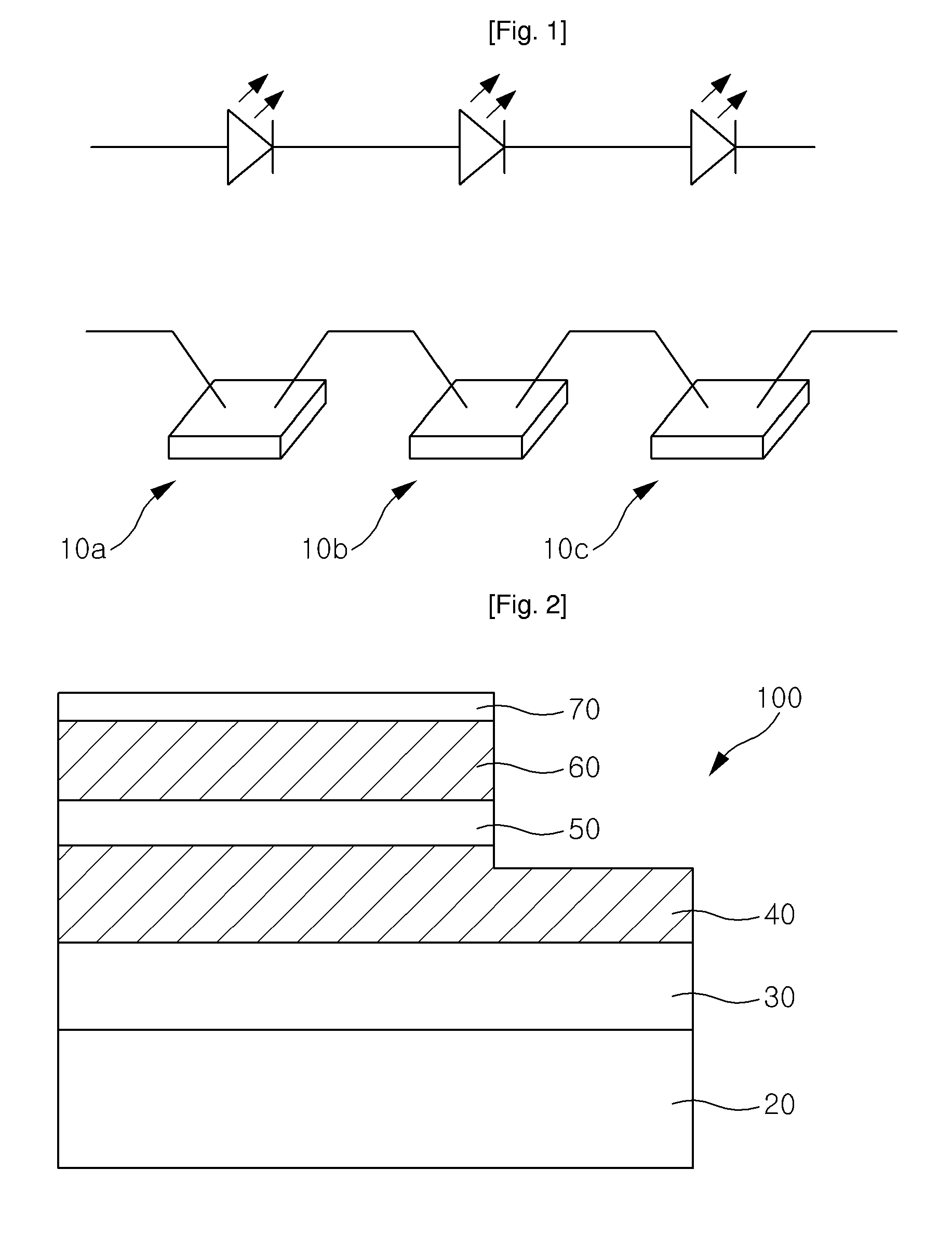

Light Emitting Element With A Plurality Of Cells Bonded, Method Of Manufacturing The Same, And Light Emitting Device Using The Same

ActiveUS20080017871A1High voltageSimple manufacturing processElectroluminescent light sourcesSolid-state devicesAC powerLight emitting device

The present invention relates to a light emitting element with arrayed cells, a method of manufacturing the same, and a light emitting device using the same. The present invention provides a light emitting element including a light emitting cell block with a plurality of light emitting cells connected in series or parallel on a single substrate, and a method of manufacturing the same, wherein each of the plurality of light emitting cells includes an N-type semiconductor layer and a P-type semiconductor layer, and the N-type semiconductor layer of one light emitting cell is electrically connected to the P-type semiconductor layer of another adjacent light emitting cell. Further, the present invention provides a light emitting device including a light emitting element with a plurality of light emitting cells connected in series. Accordingly, it is possible to simplify a manufacturing process of a light emitting device for illumination capable of being used with a household AC power source, to decrease a fraction defective occurring in manufacturing a light emitting device for illumination, and to mass-produce the light emitting device for illumination. Further, there is an advantage in that DC driving efficiency can be enhanced in an AC operation by installing a predetermined rectifying circuit outside the light emitting element.

Owner:SEOUL VIOSYS CO LTD

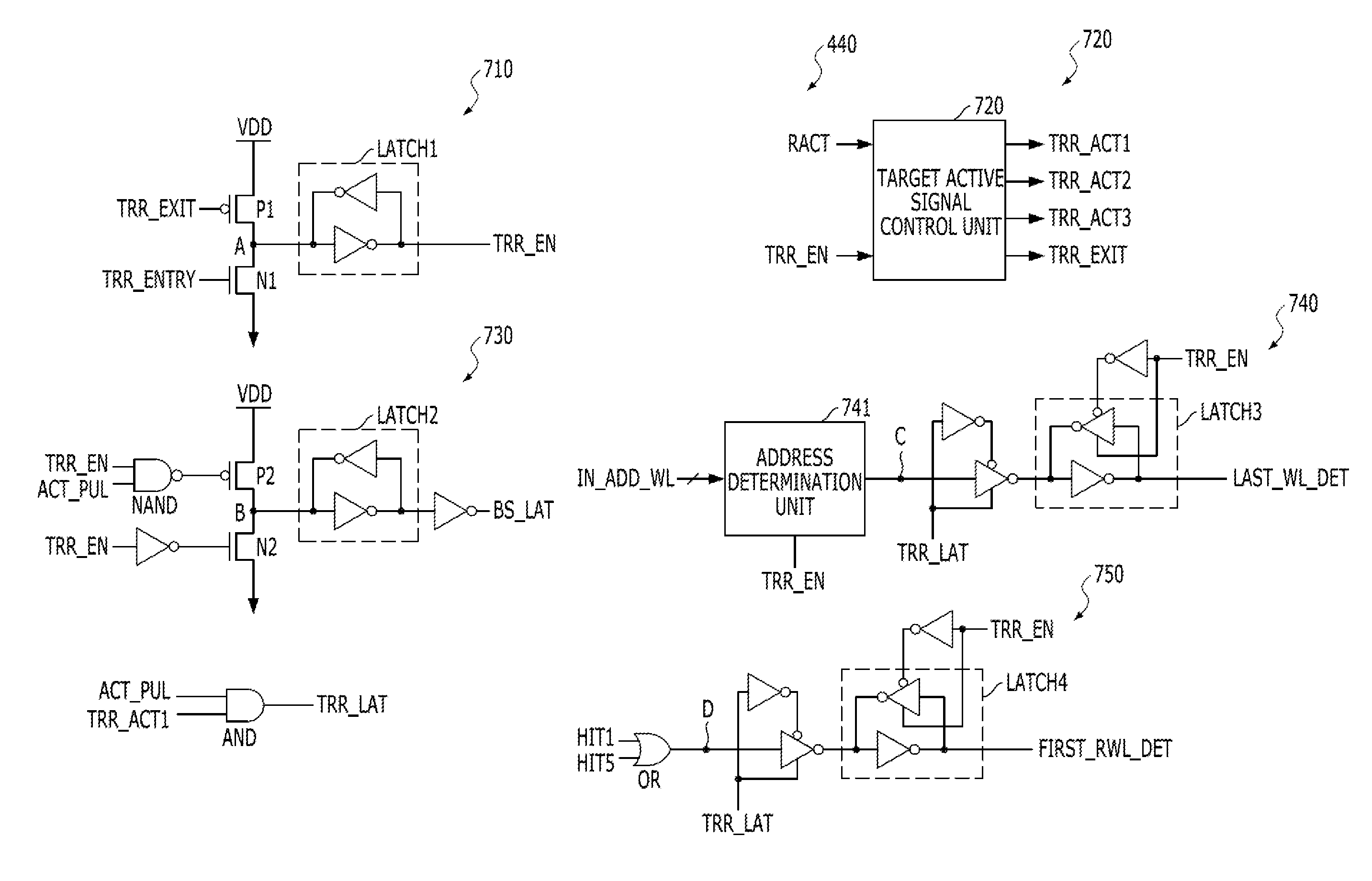

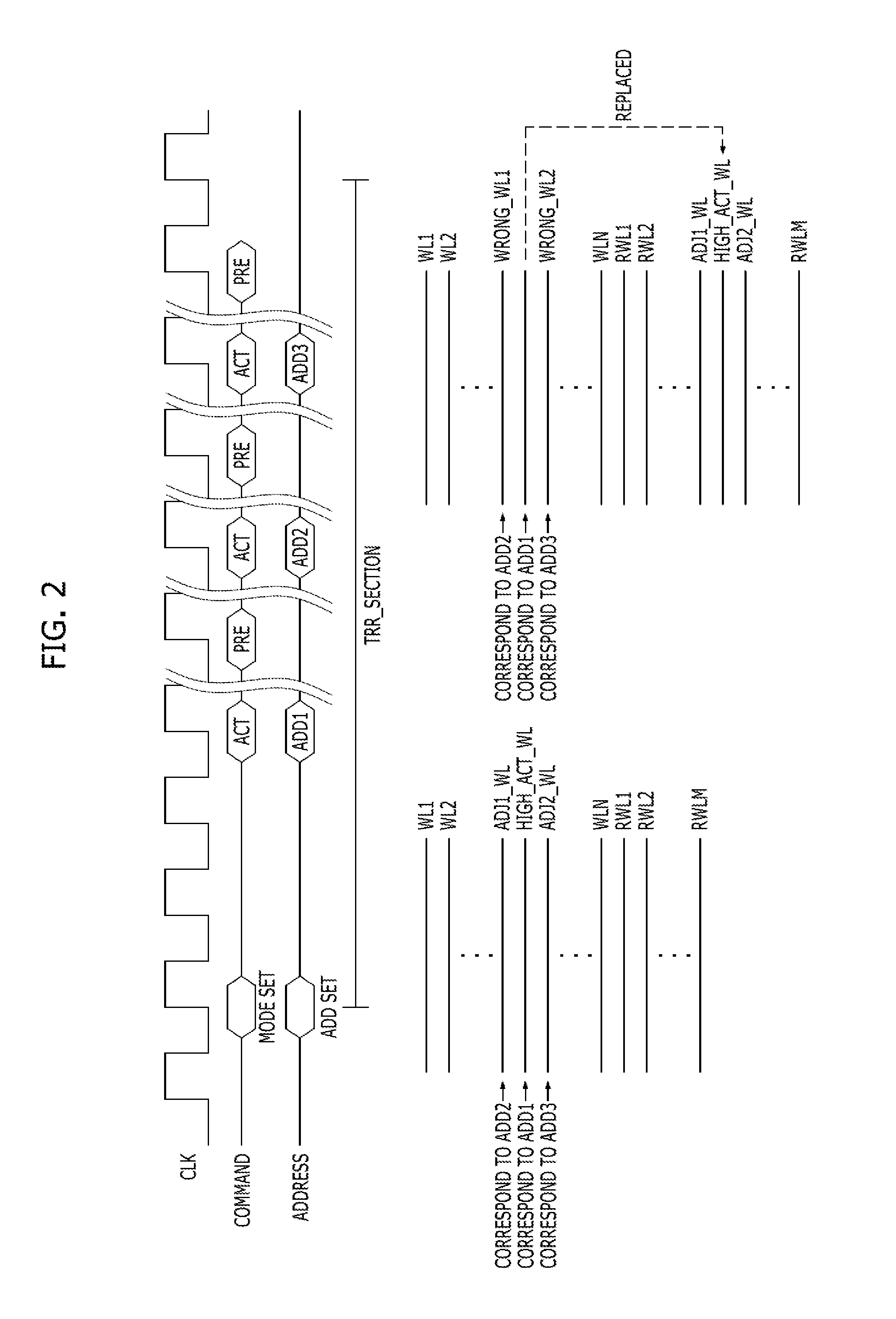

Memory and memory system including the same

A memory including a first cell block comprising a plurality of first word line groups, and one or more first redundancy word line groups each corresponding to one hit signal of a plurality of hit signals; a second cell block comprising a plurality of second word line groups, and one or more second redundancy word line groups each corresponding to one hit signal of the plurality of hit signals; and a control unit suitable for selecting a cell block and a word line in response to a first input address and refreshing a selected word line based on an input address inputted after the first input address, while refreshing one or more adjacent word lines adjacent to a first selected word line, which is selected by the first input address, in response to the first input address and the hit signals when the first selected word line is adjacent to a redundancy word line, wherein the first input address is first inputted in a target refresh section.

Owner:SK HYNIX INC

Pressure balancing of electrolytes in redox flow batteries

Methods and apparatuses are disclosed for mitigating electrolyte migration in a redox flow battery system. A first parameter of a first electrolyte in a first flow path of a redox flow battery cell block may be measured. The first flow path may have an inlet to and an outlet from the redox flow battery cell block. A second parameter of a second electrolyte in a second flow path of the redox flow battery cell block may be measured. The second flow path may have an inlet to and an outlet from the redox flow battery cell block. The first parameter may be detected to be greater than the second parameter. A first device coupled to the redox flow battery cell block in the second flow path may be operated to increase the second parameter in the second flow path.

Owner:ENERVAULT CORP

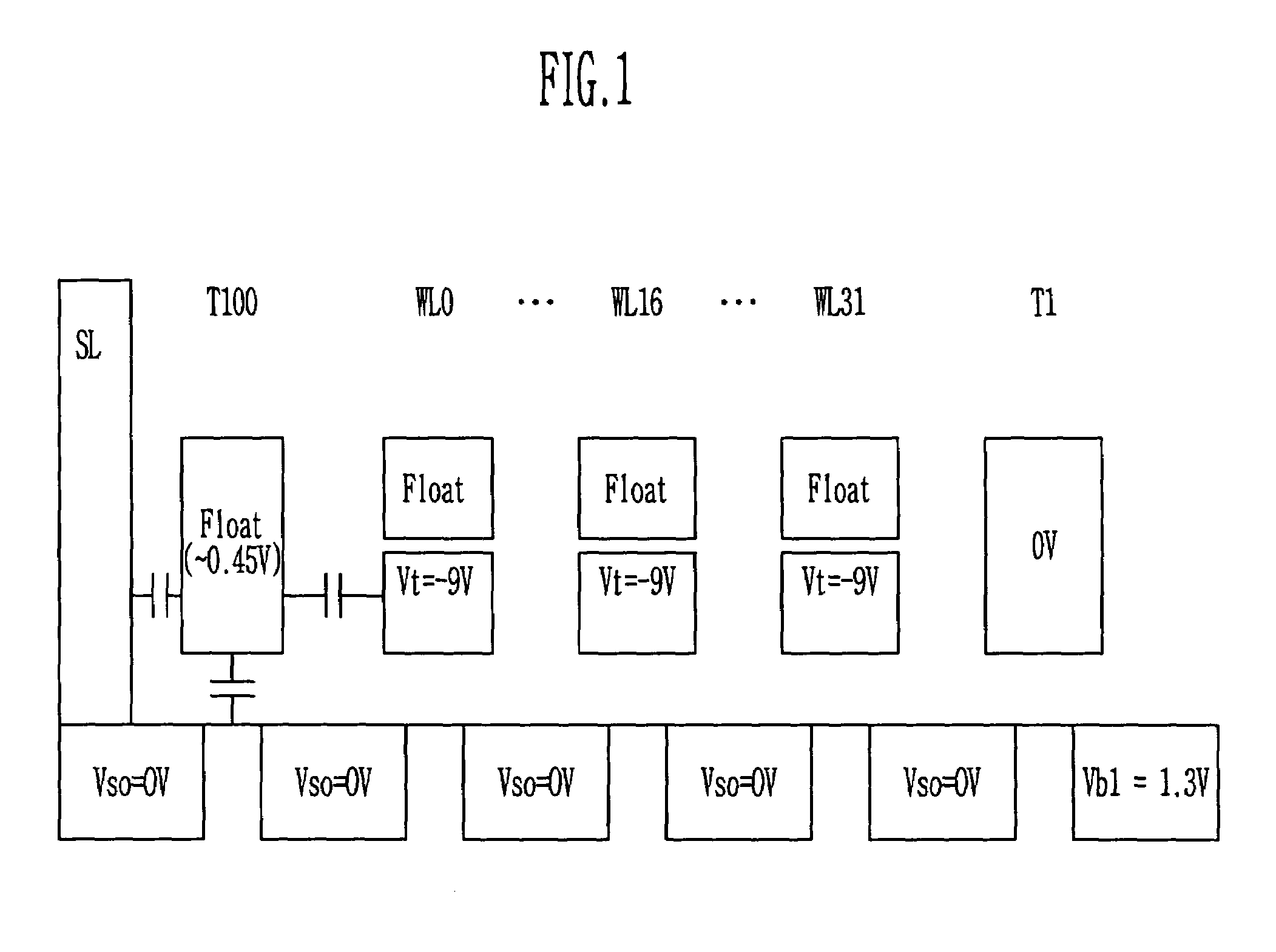

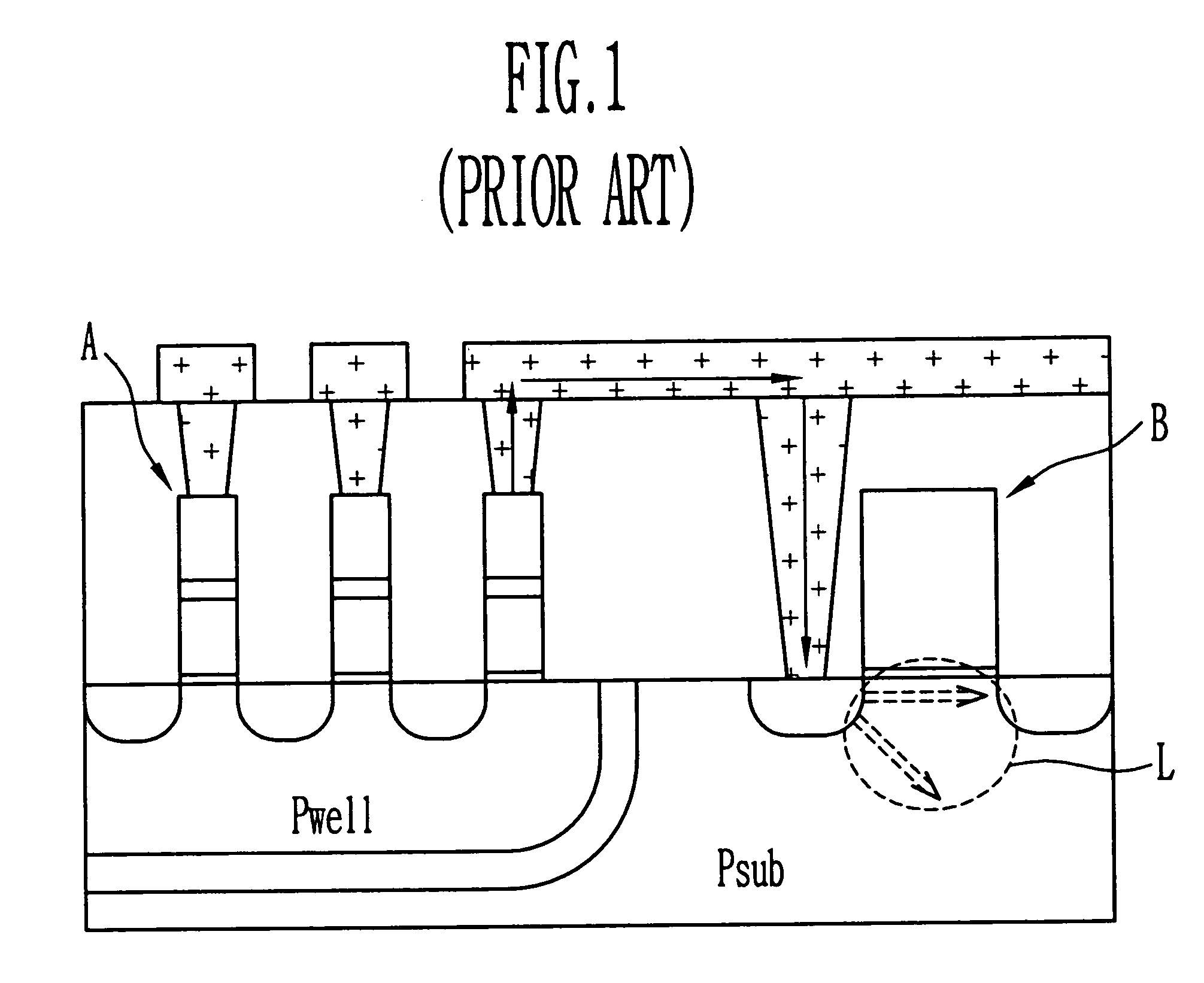

NAND flash memory device and method of reading the same

ActiveUS7035143B2Reduce leakage currentIncreasing source-side resistance of selection transistorsTransistorSolid-state devicesBack biasEngineering

Provided is related to a NAND flash memory device and method of reading the same, in which during a read operation, a ground voltage is applied to string and ground selection transistors of deselected cell blocks so as to increase resistance of a string line to prevent leakage currents due to a back-bias effect. A reduced bitline leakage current increases an ON / OFF current ratio between programmed and erased cells to reduce a sensing time therein, which makes a read trip range so as to prevent variation of threshold voltages due to data retention and reading disturbance. Voltages can be independently applied to source selection lines by electrically isolating source selection transistors between the cell blocks. It is available to reduce the number of source discharge transistors by electrically connecting the source selection transistors between adjacent cell blocks.

Owner:STMICROELECTRONICS SRL +1

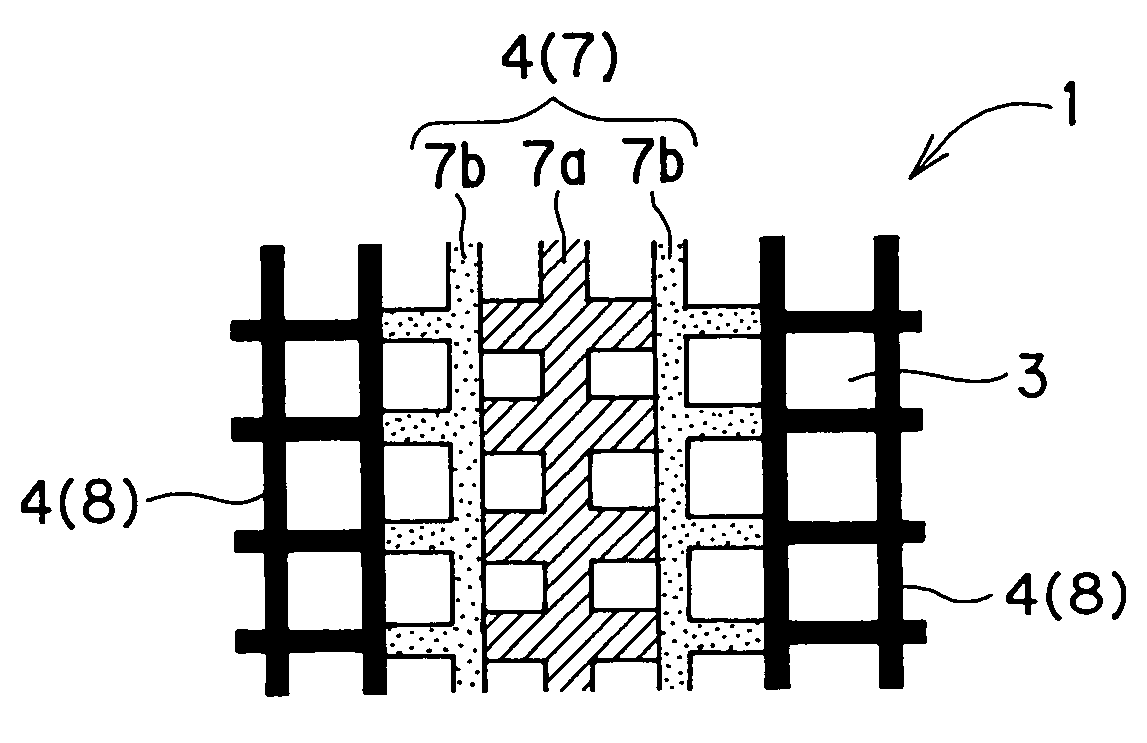

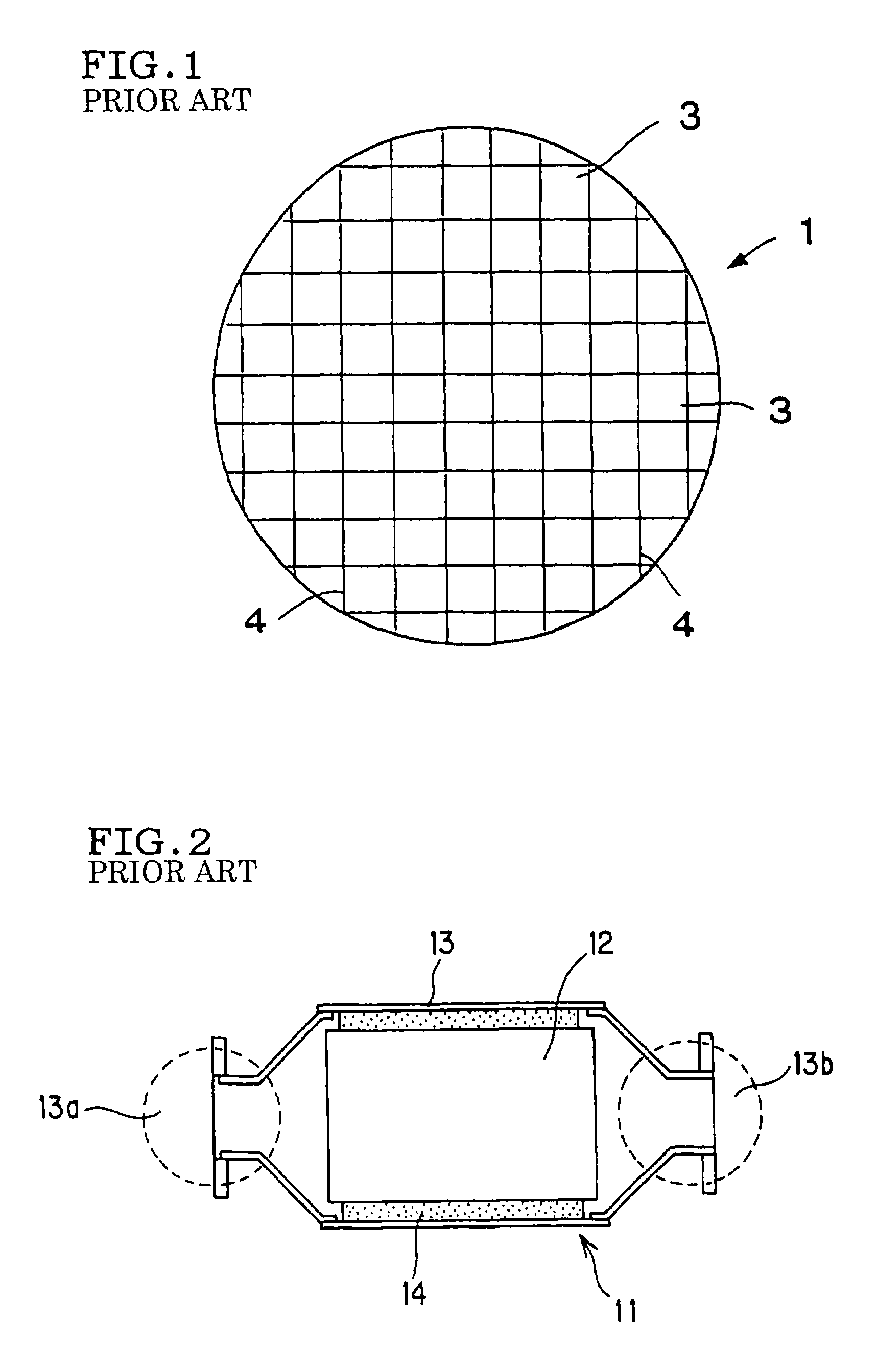

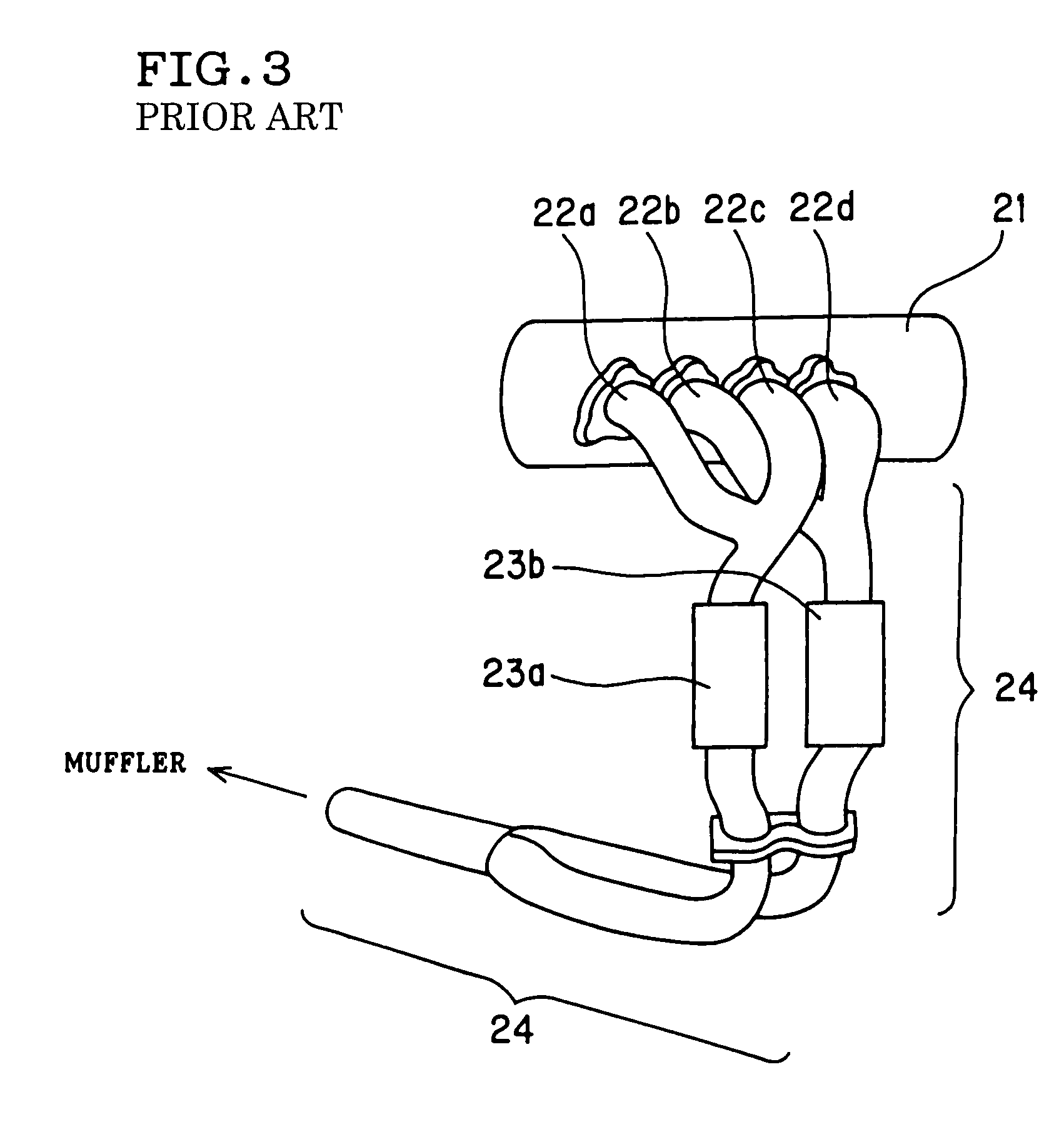

Honeycomb structure and catalytic converter

ActiveUS7438868B2Inhibit outputWeight increaseCombination devicesPhysical/chemical process catalystsIn vehicleProduct gas

A catalytic converter has a honeycomb catalyst body, a housing and a holding material, wherein the honeycomb catalyst body has, as the catalyst carrier, a honeycomb structure having an inner wall(s) which is (are) provided so as to divide the large number of cells into two or more cell blocks and which has (have) a thickness larger than the thickness of the partition walls, and the exhaust gas-incoming section and purified gas-outgoing section of the housing are divided by diaphragms into two or more exhaust gas-incoming passages and two or more purified gas-outgoing passages, and the two or more cell blocks of the honeycomb structure are allowed to communicate with the corresponding two or more exhaust gas-incoming passages and corresponding two or more purified gas-outgoing passages of the housing. This catalytic converter has a compact structure and can effectively prevent the reduction in engine output caused by exhaust gas interference, without adoption of complicated exhaust pipe structure, or increase in vehicle body weight, or increase in cost.

Owner:NGK INSULATORS LTD

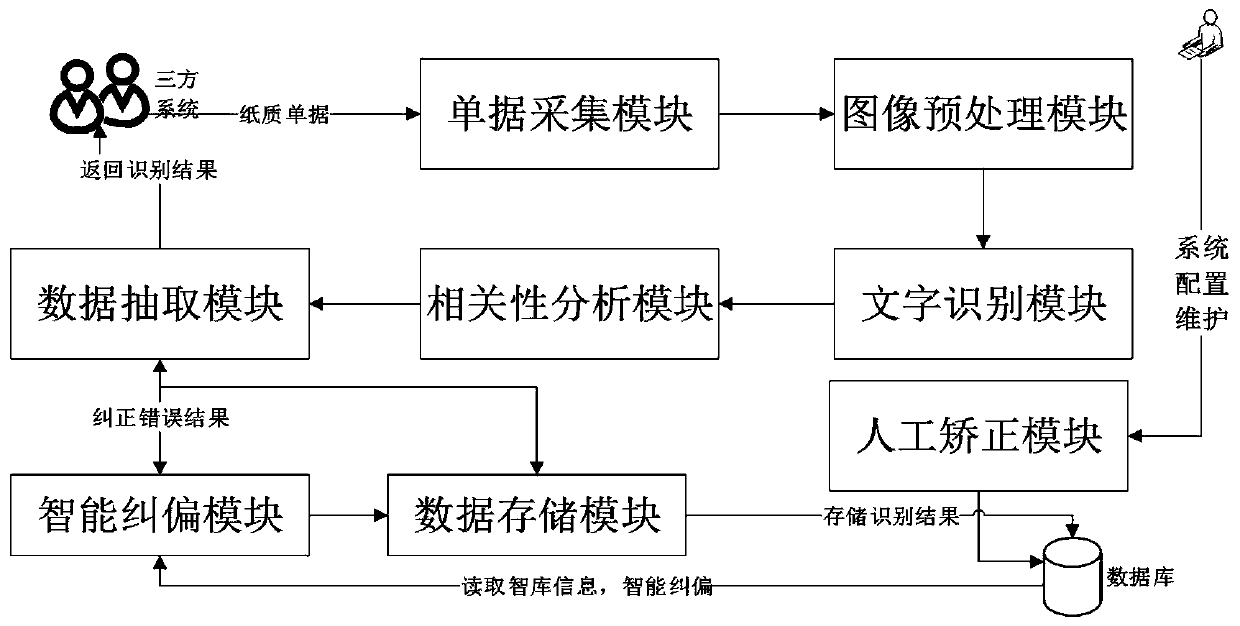

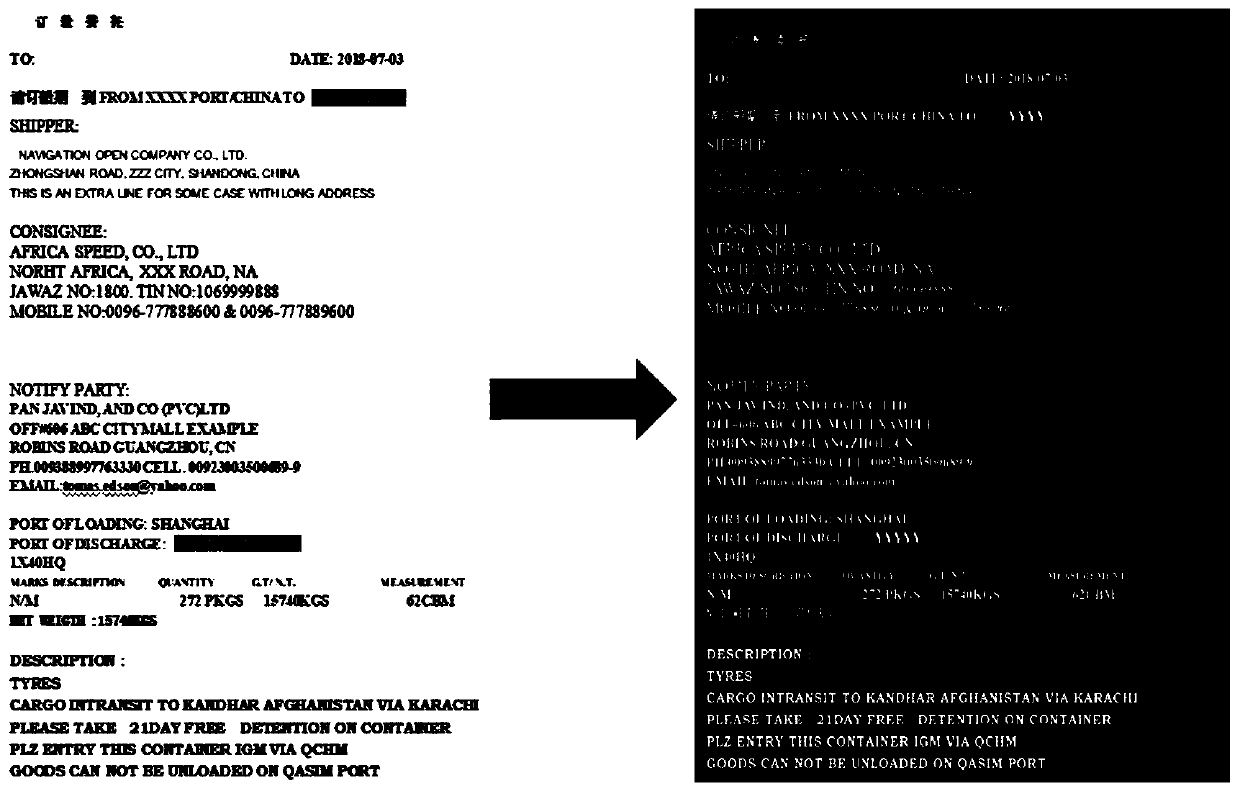

A self-adaptive intelligent document recognition and input device and a use method thereof

ActiveCN109840519AHigh degree of intelligenceImprove recognition accuracyCharacter and pattern recognitionEnergy efficient computingData acquisitionCorrelation analysis

The invention belongs to the field of image recognition processing. The invention relates to a self-adaptive intelligent document recognition and input device and a use method thereof. A data acquisition module acquires a paper text of a client into a picture file through scanning or shooting, the preprocessing module carries out block processing on the text in an image by utilizing a morphological processing algorithm, lattices in each line or table are made into unequal cell blocks, and the character recognition module carries out binary processing on each cell block; Then, the correlation analysis module performs correlation analysis according to a pre-configured keyword and a pre-configured rule; According to the technical scheme, the relation between text blocks is analyzed, a data extraction module is guided to extract needed field content, a deviation rectification module can perform verification and automatic correction on the extracted content according to previous identification and deviation rectification historical data, and finally a result is stored and returned to a calling party. The system is ingenious in design concept, safe and convenient to use, high in intelligent degree, high in recognition accuracy, friendly to application environment and wide in market prospect.

Owner:青岛盈智科技有限公司

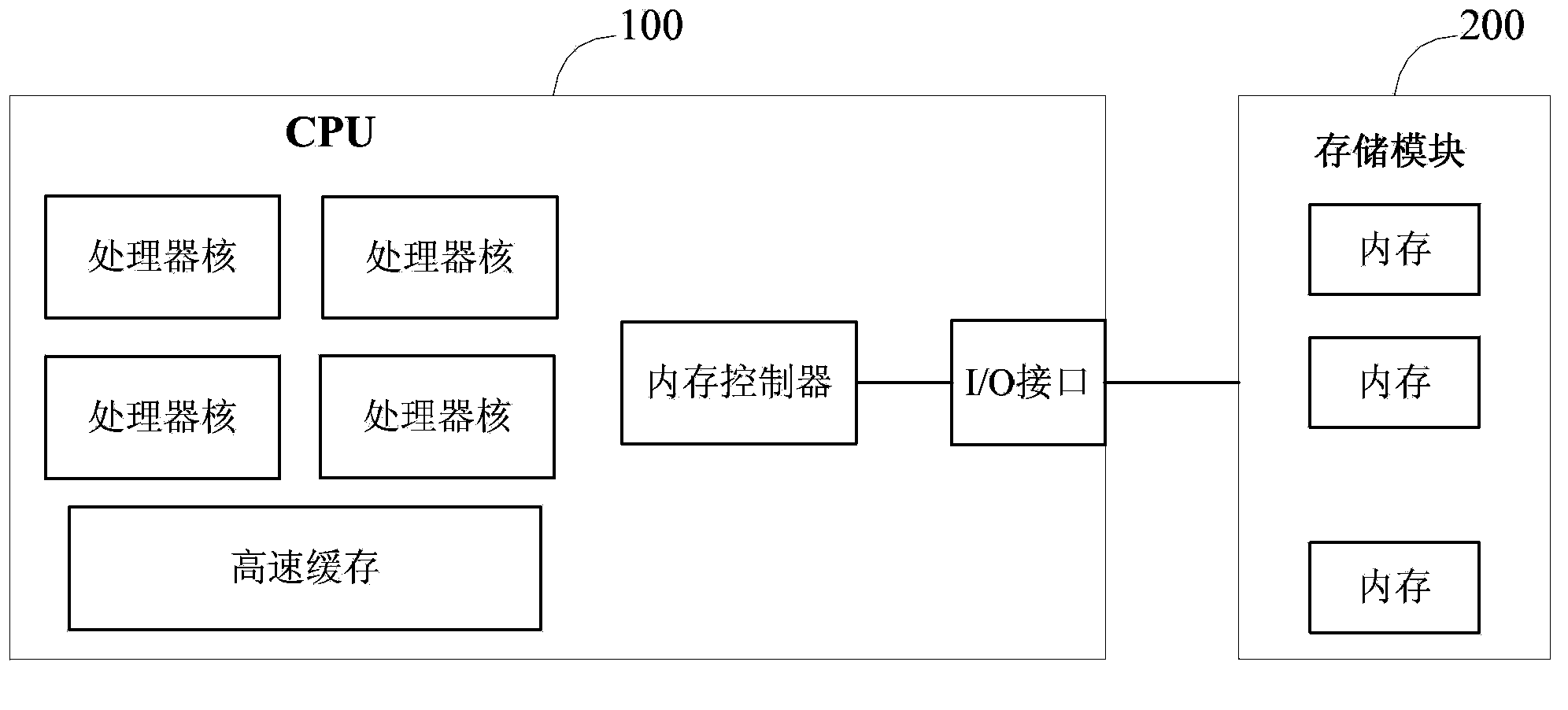

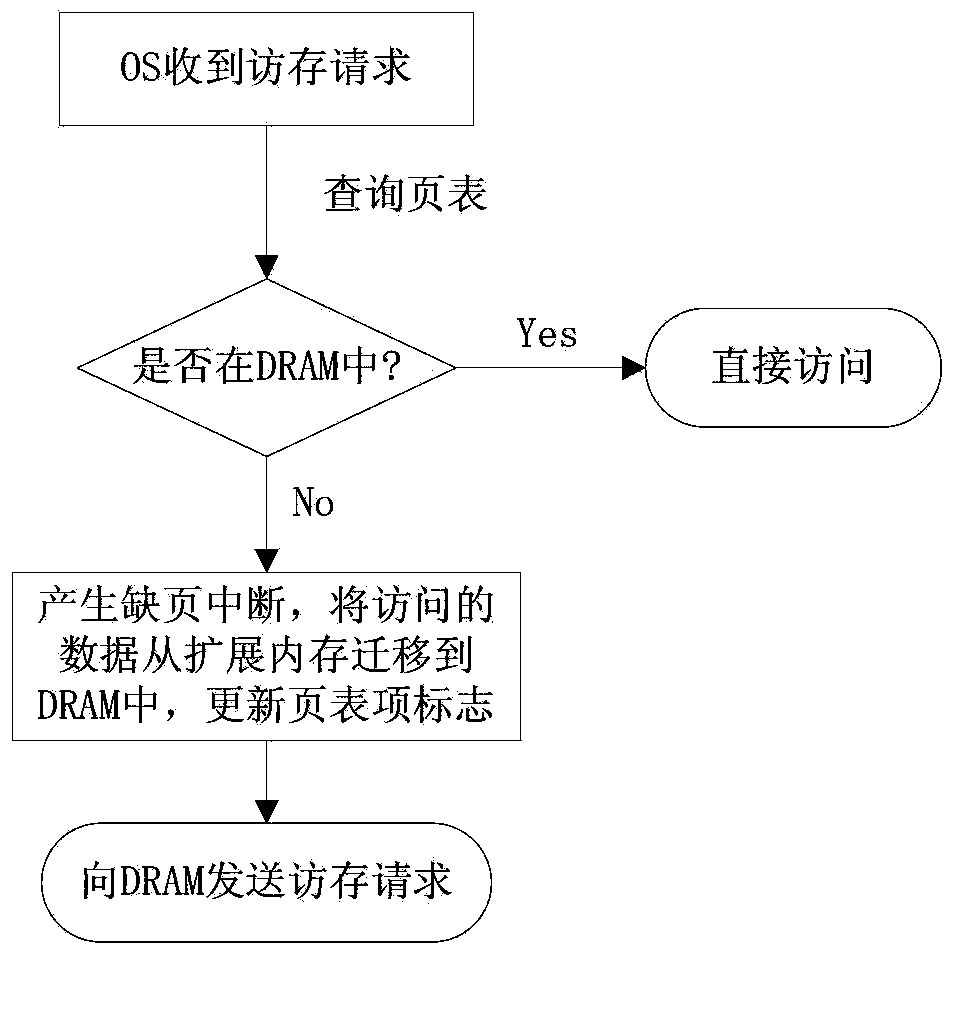

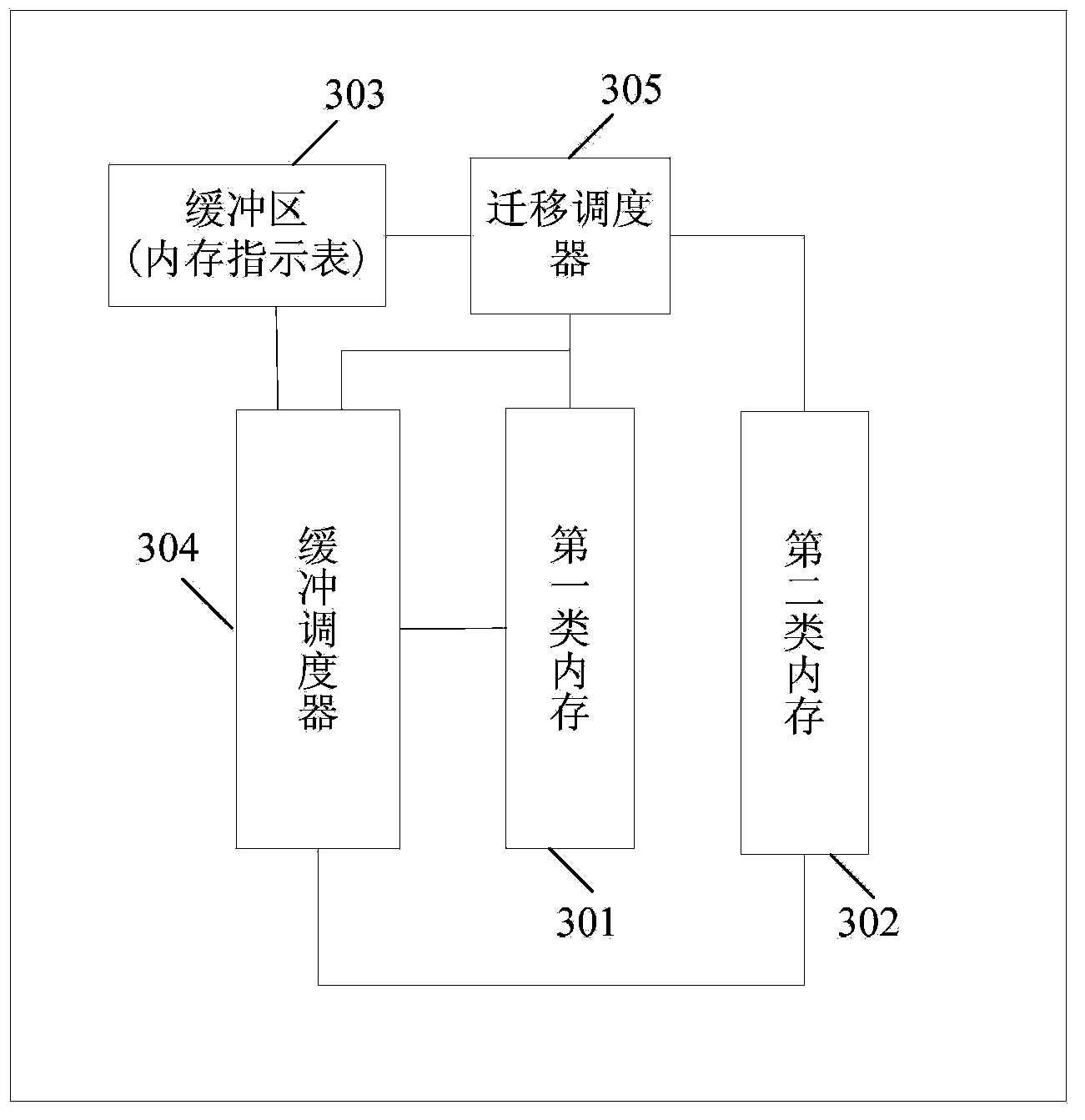

Memory system, memory access request processing method and computer system

InactiveCN104216837AImprove access speedNo interruptMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressComputerized system

Disclosed in an embodiment of the present invention are a memory system, memory access request processing method and computer system, the memory system comprising: a first memory and a second memory of different types respectively used for storing the operating data of a processor; a memory indicator table for storing the access memory addresses of a data cell block located in the first memory; a buffer scheduler for receiving a memory access request from a memory controller; determining whether the data cell block corresponding to an access memory address is stored in the first memory or in the second memory, and completing the access memory operation of the memory access request in the determined memory; a migration scheduler for updating the access information of the data cell block; and according to the access information of the data cell block, determining whether to migrate the data cell block in the second memory into the first memory, and updating the memory indicator table after migration.

Owner:HUAWEI TECH CO LTD +1

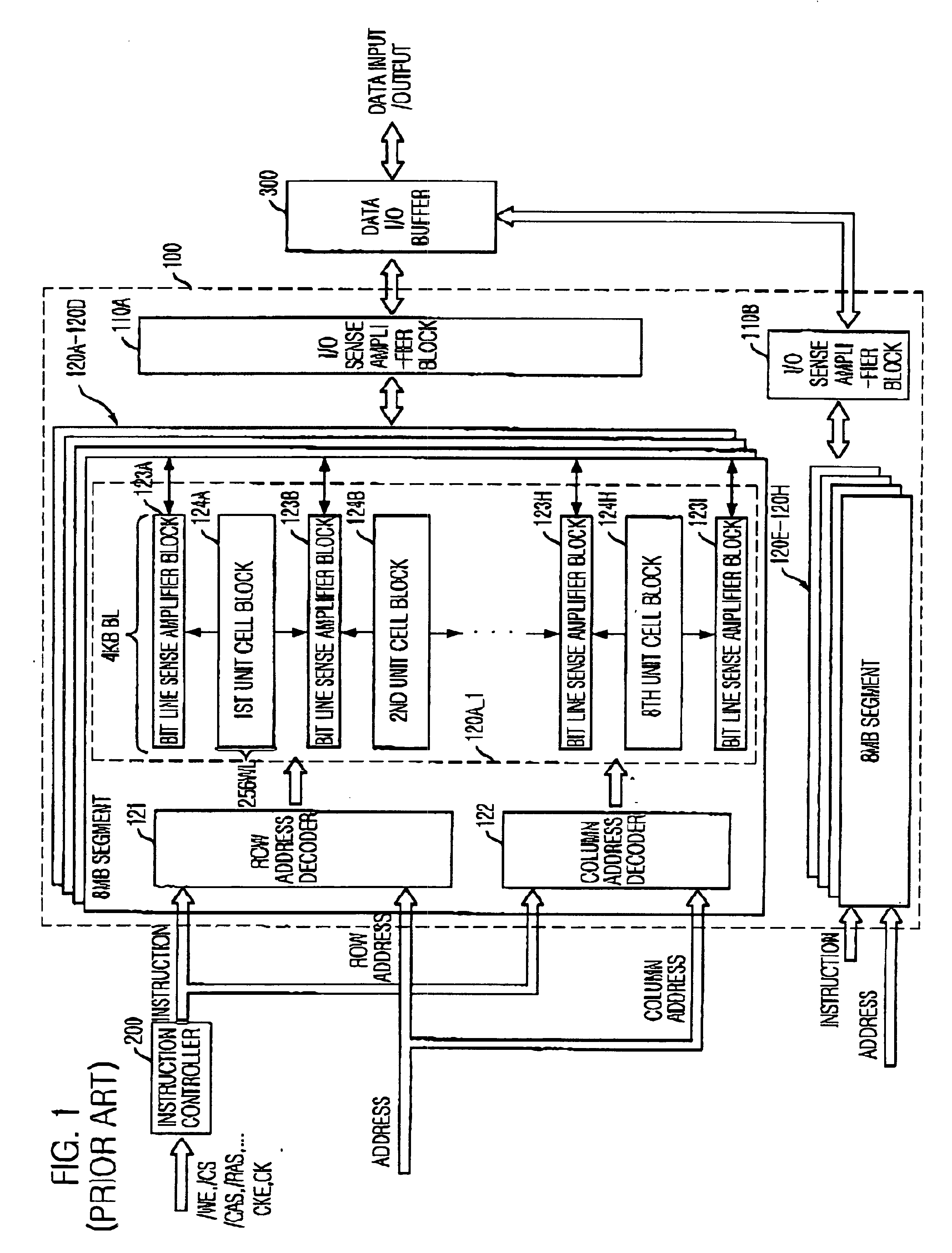

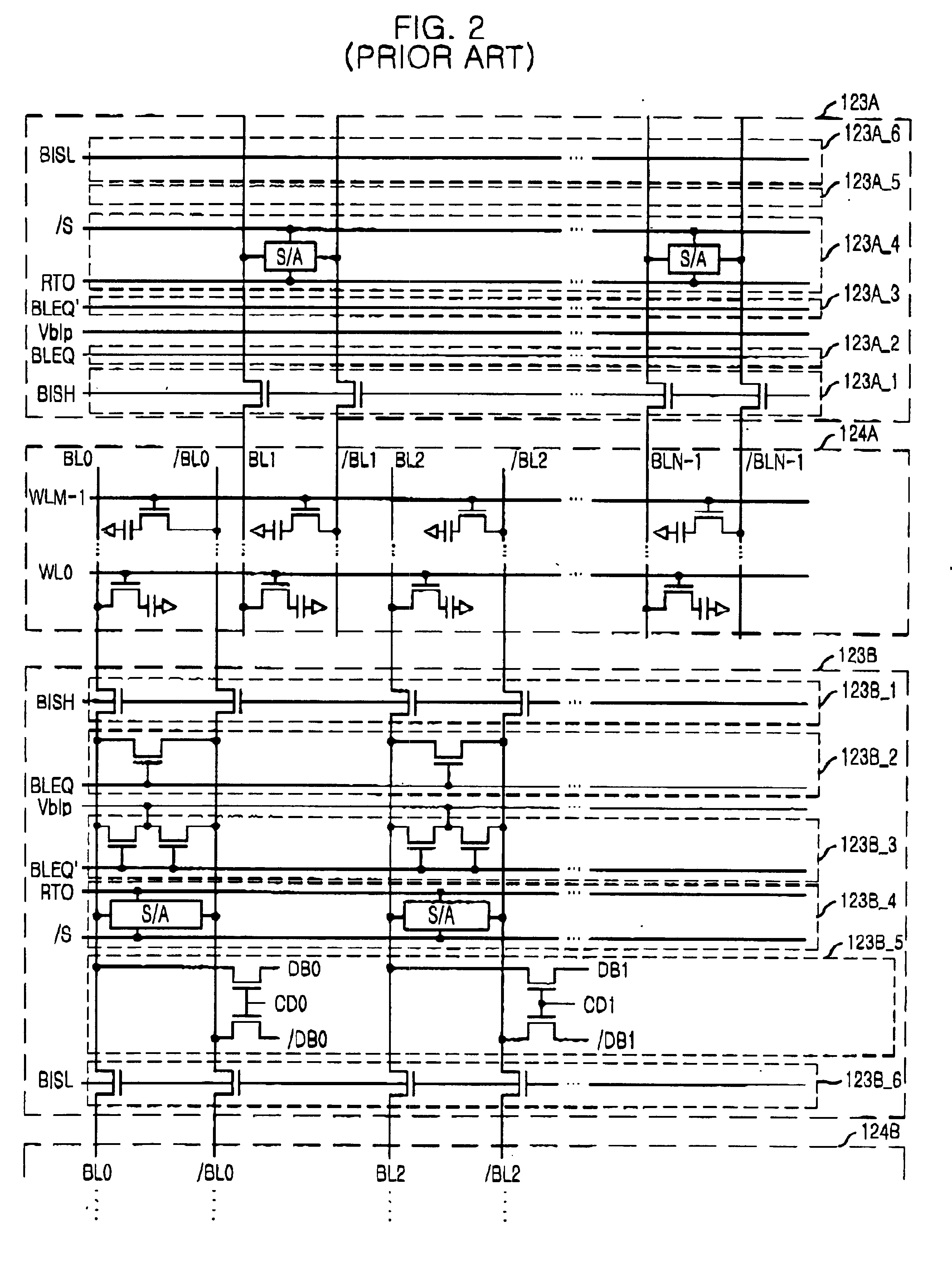

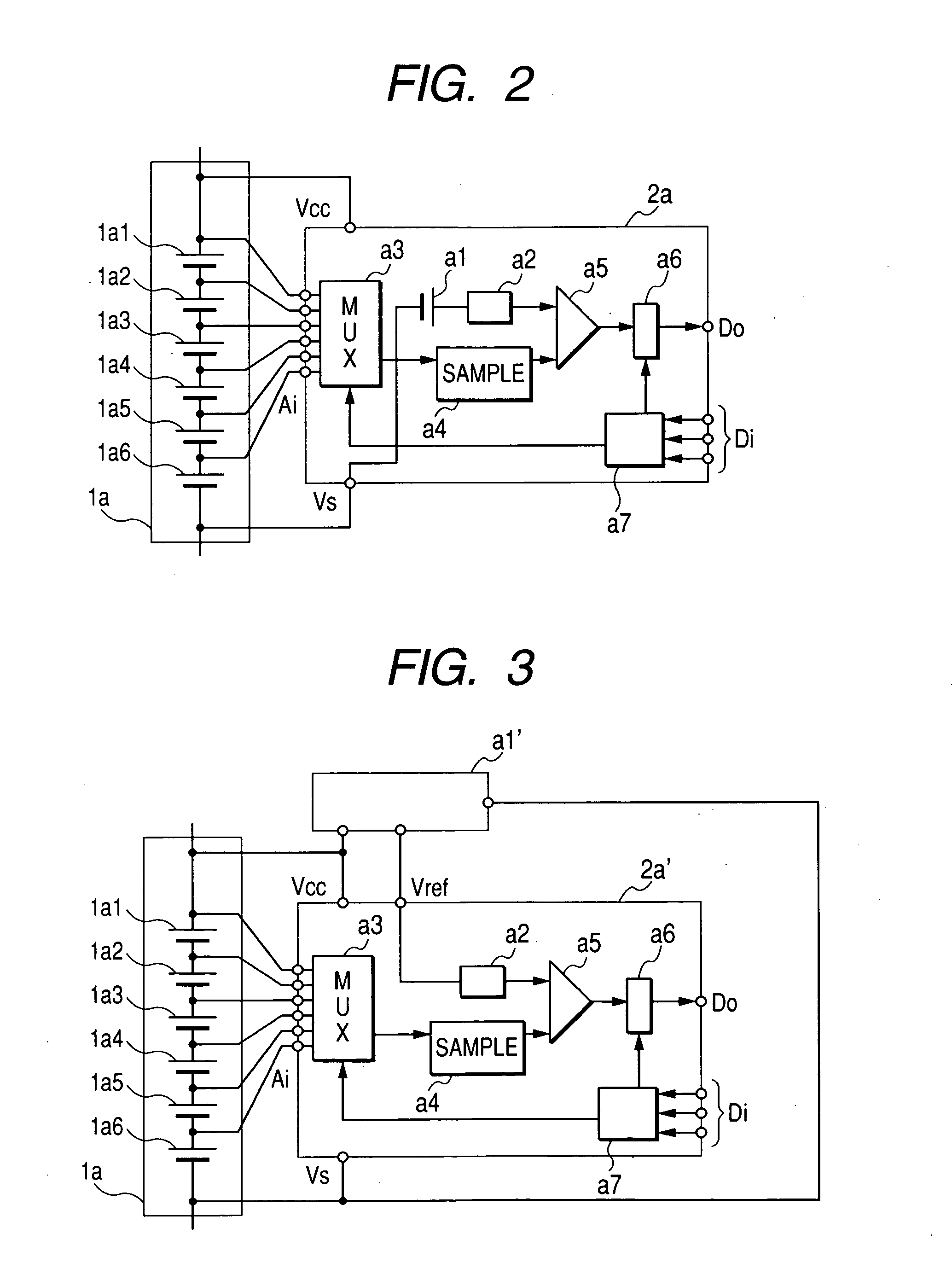

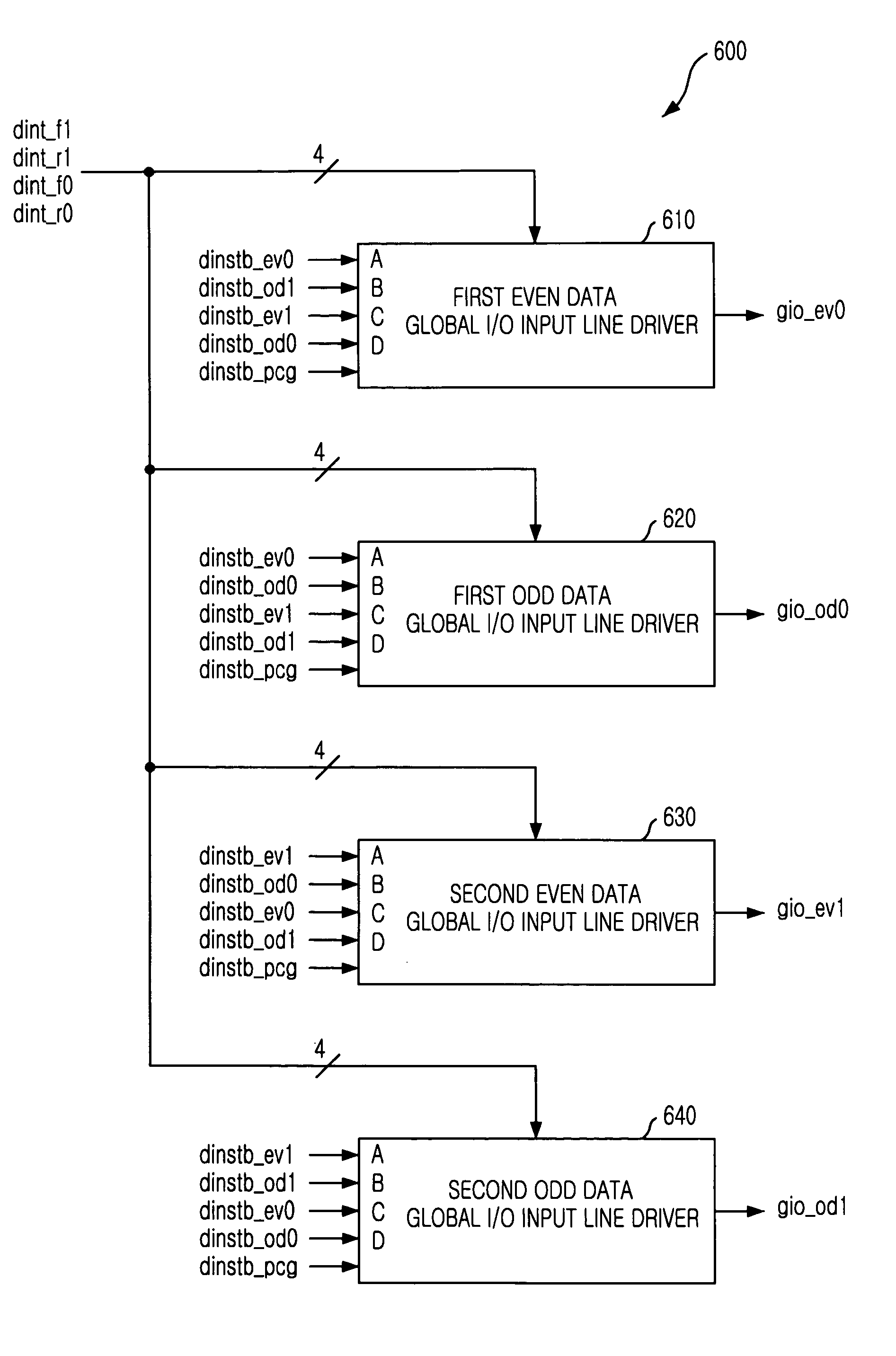

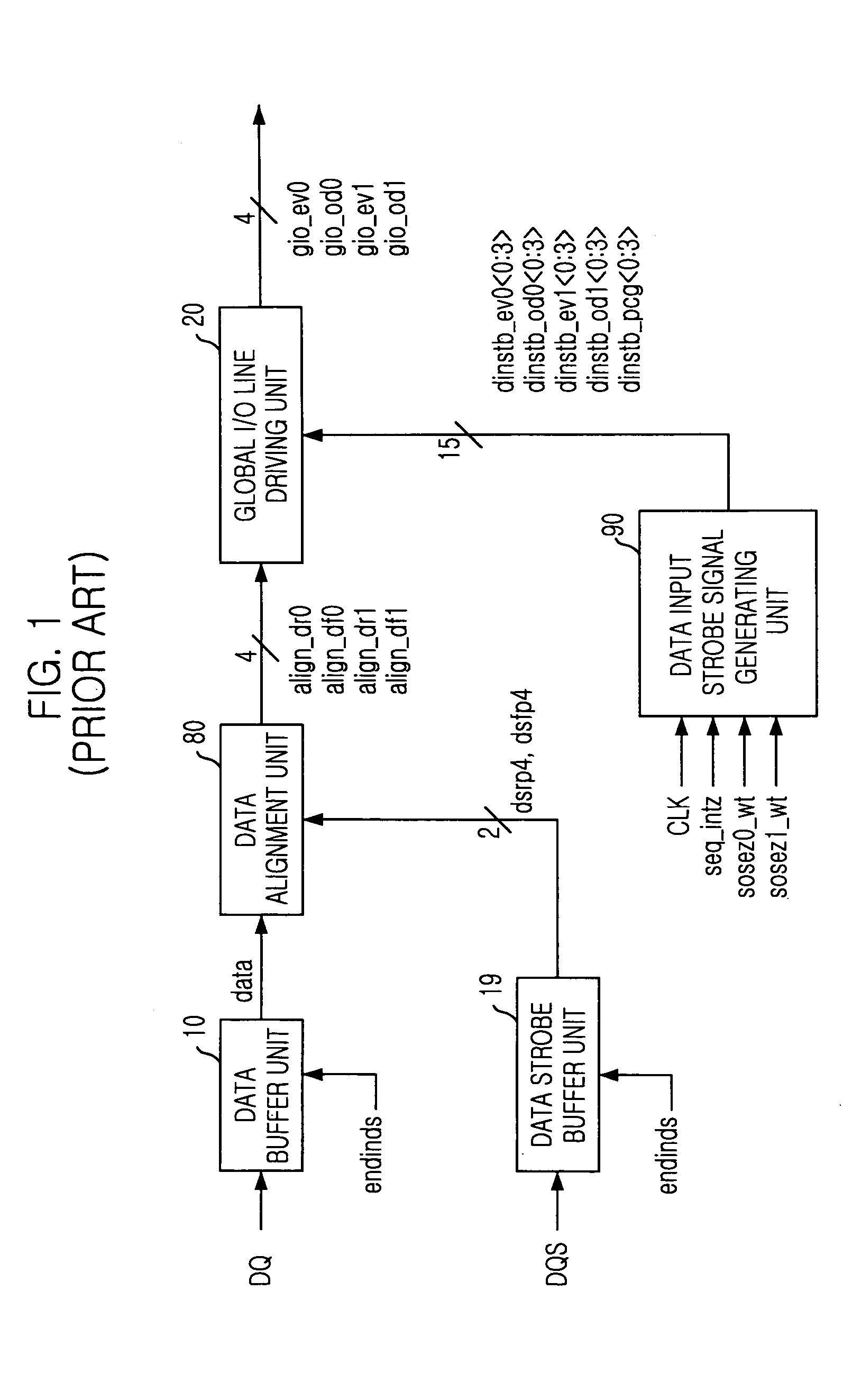

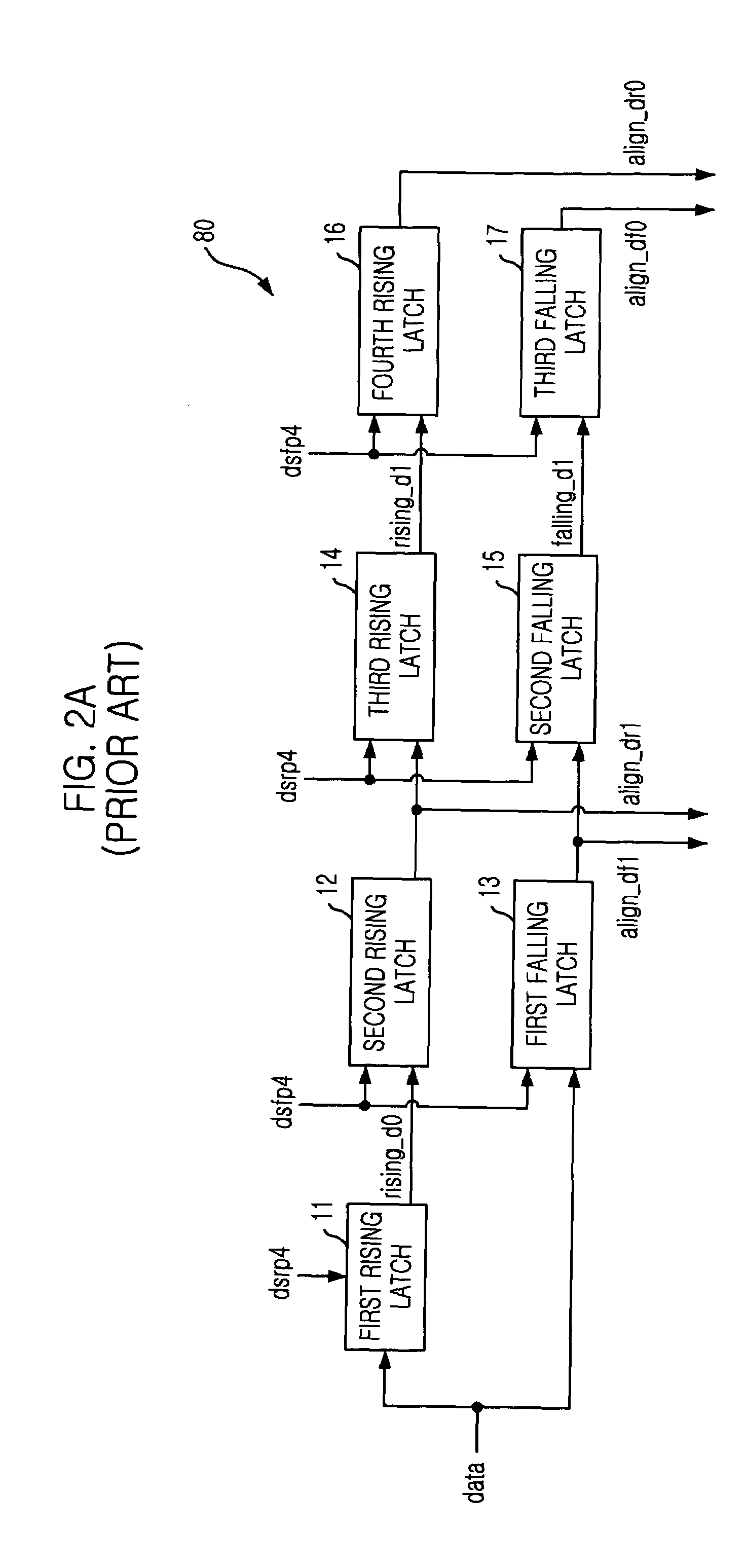

Synchronous semiconductor memory device with input-data controller advantageous to low power and high frequency

ActiveUS6987704B2Simple processHigh frequencyRead-only memoriesDigital storageInternal memoryControl signal

Owner:SK HYNIX INC

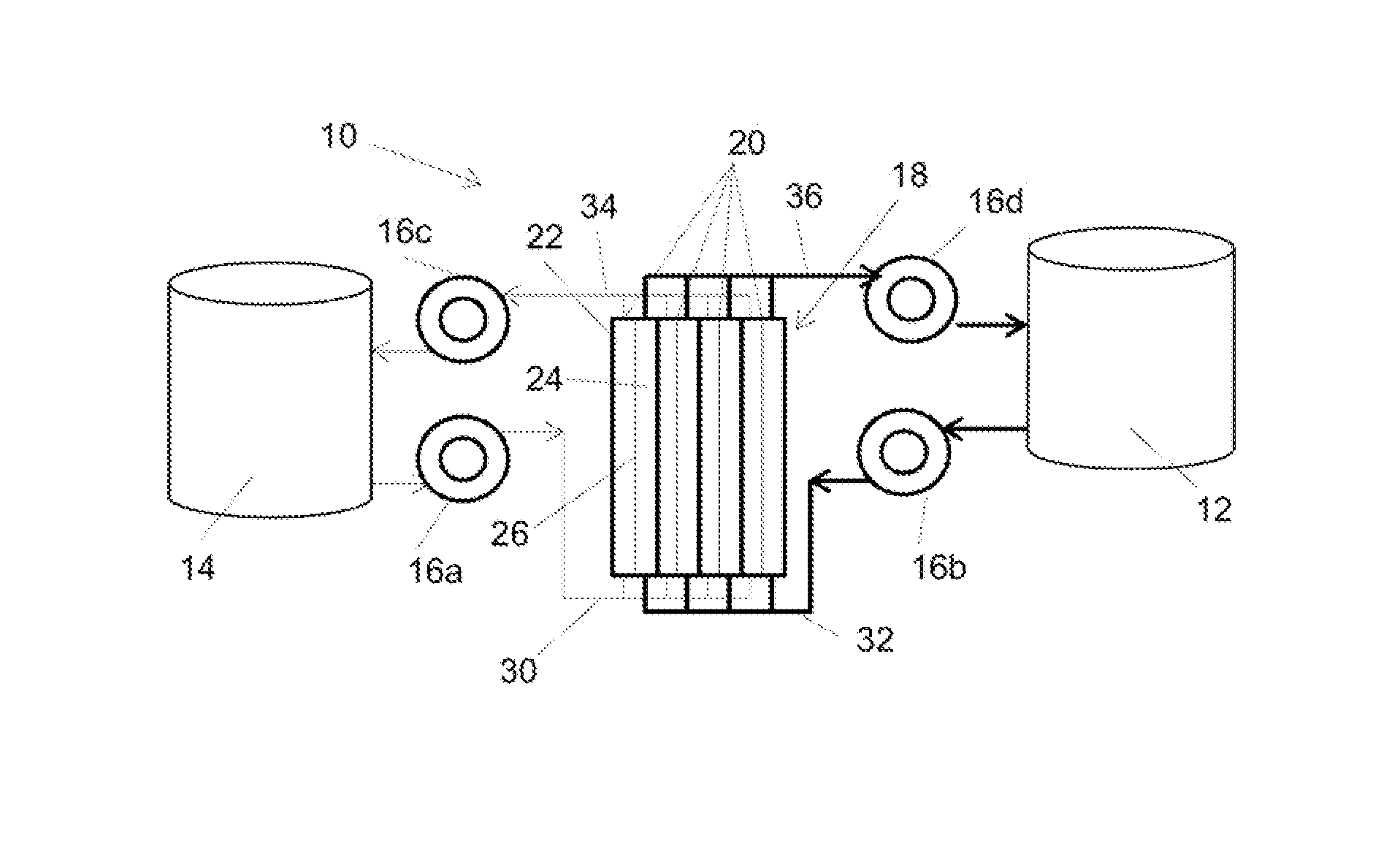

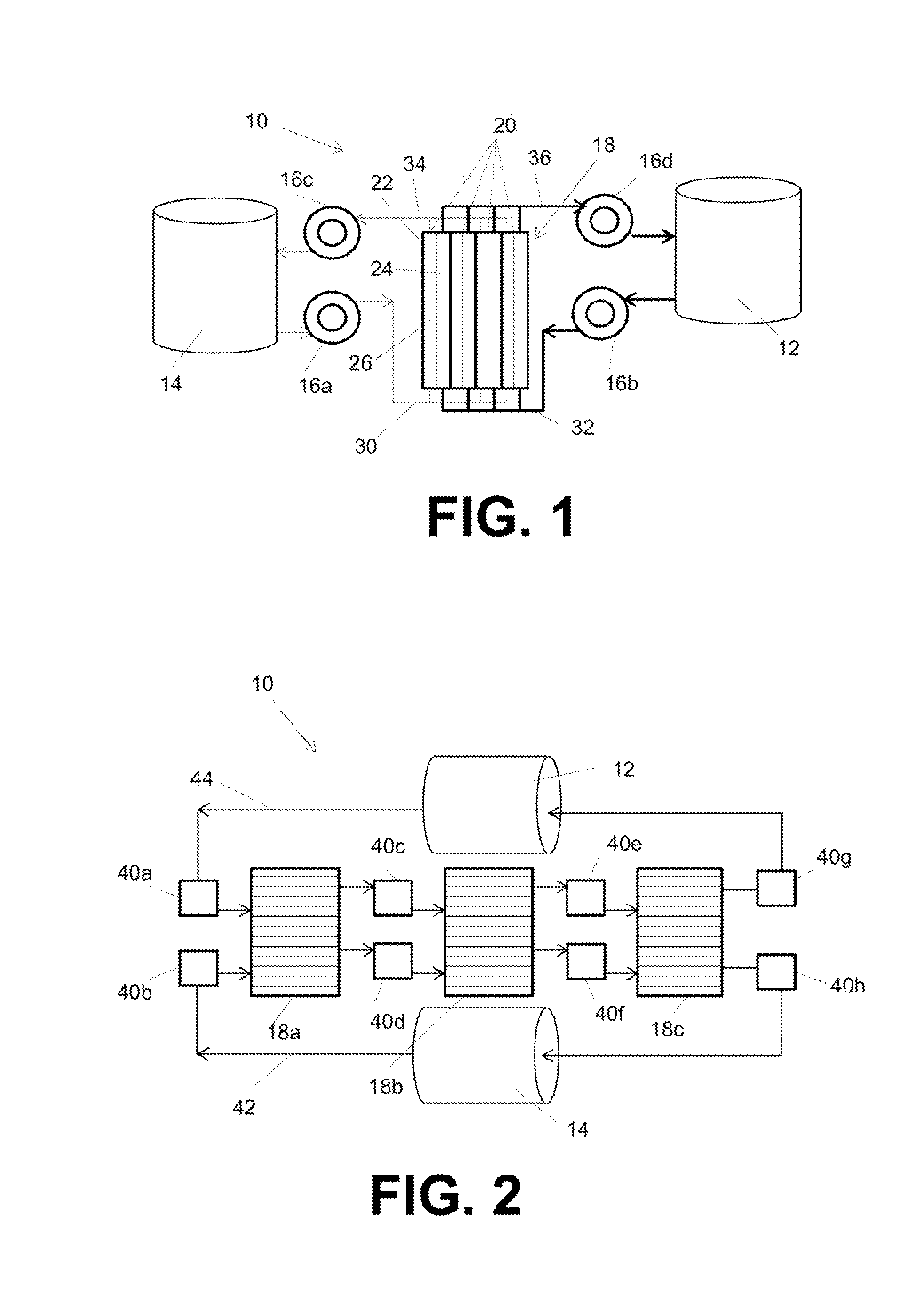

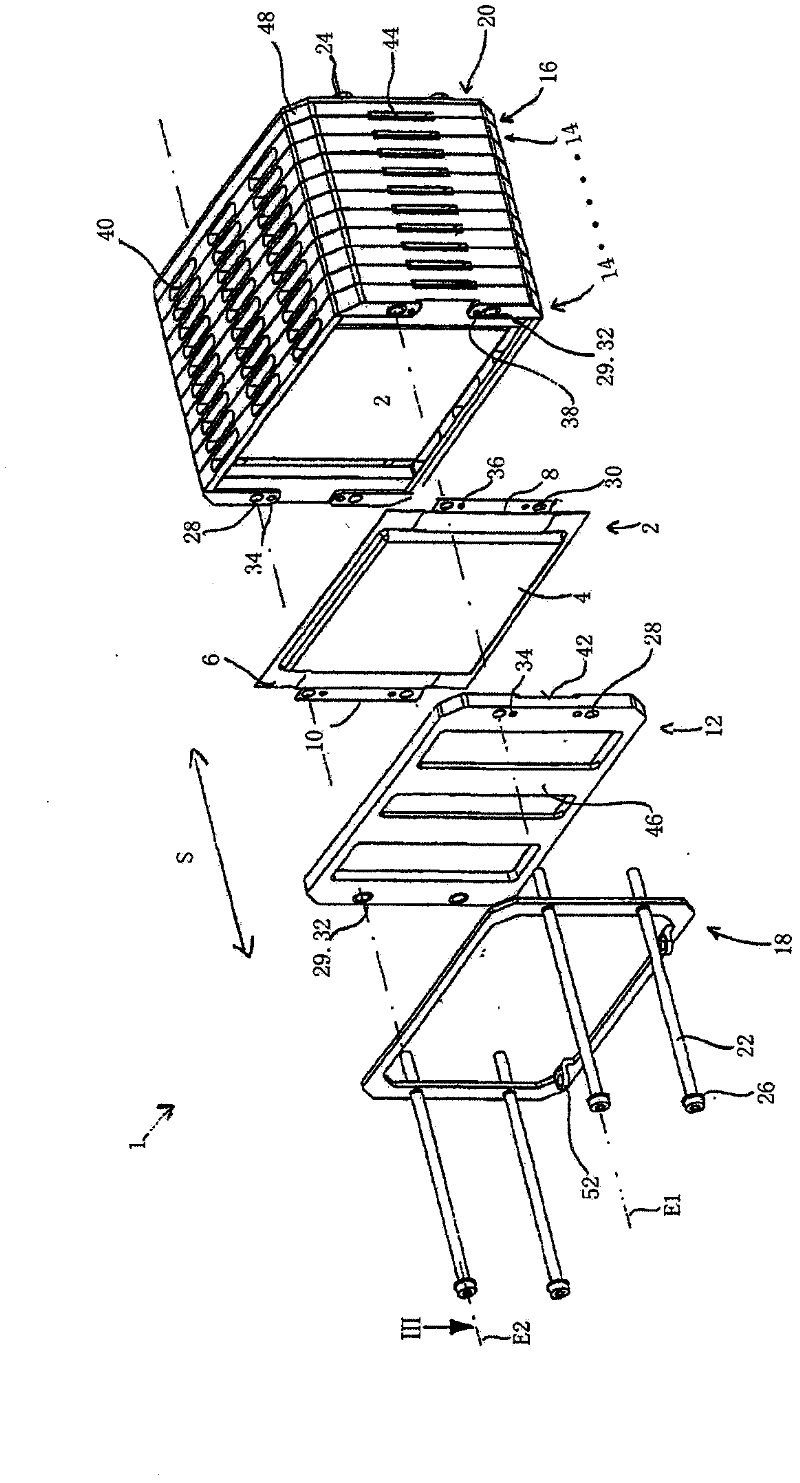

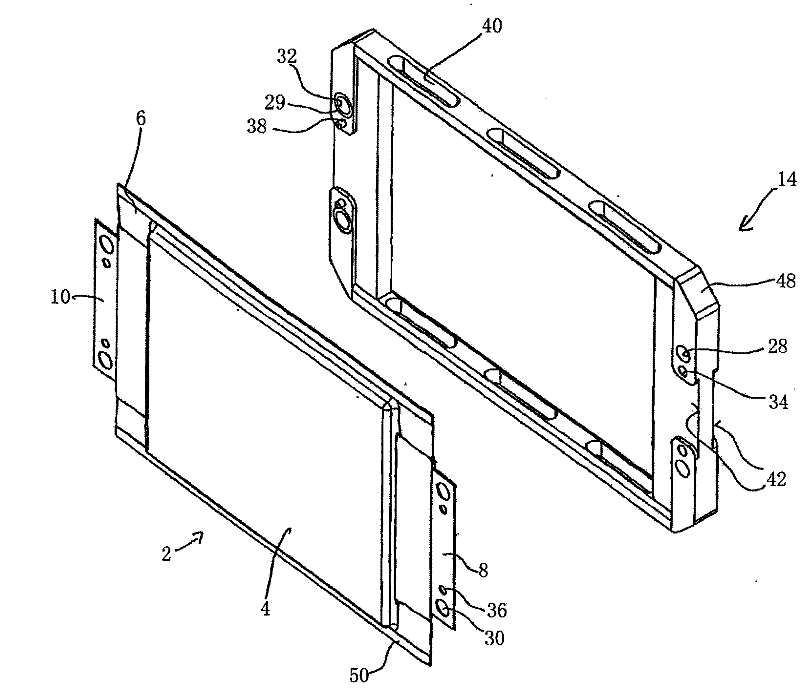

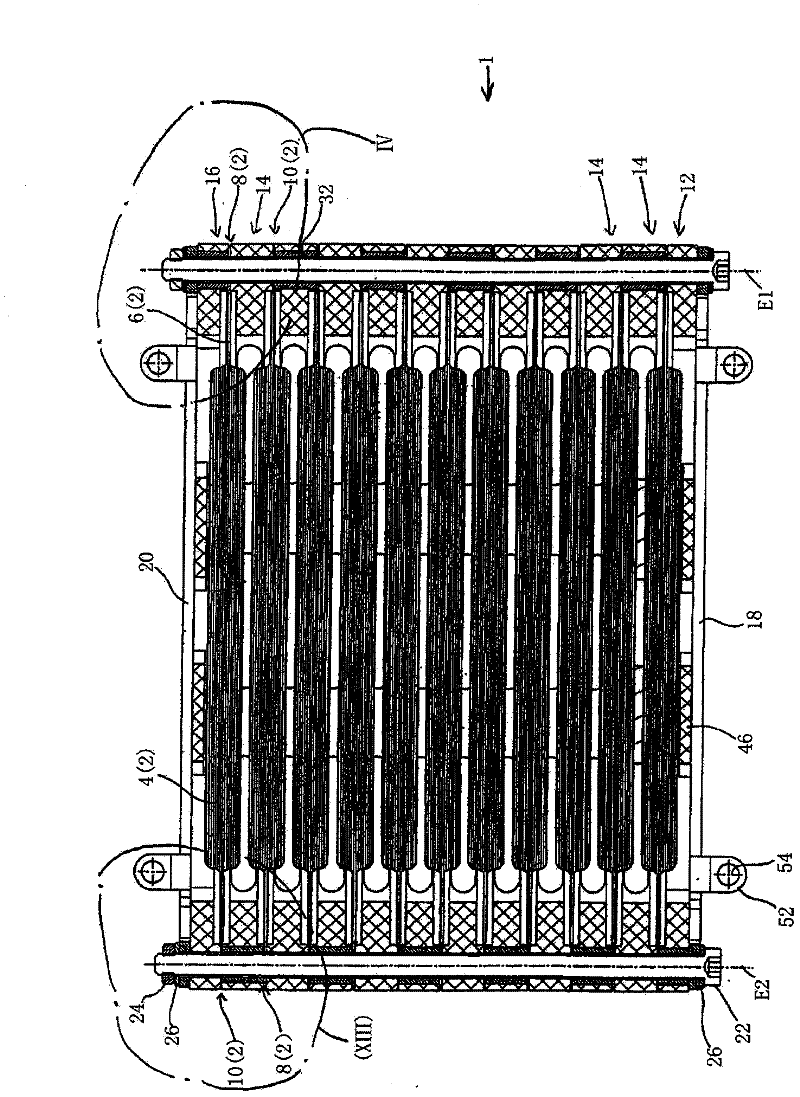

Electrochemical energy storage device

InactiveCN102308412AFinal product manufactureSmall-sized cells cases/jacketsStorage cellElectrochemical energy storage

A storage device for electric energy according to an aspect of the invention comprises a plurality of flat storage cells (2), wherein a plurality of storage cells (2) are stacked in a stacking direction into a cell block (1) and are held together by a tensioning device (22, 24, 26, 222) between two pressure plates (18, 20), and wherein the storage cells (2) are connected to each other within the cell block (1) in parallel and / or in series. Each storage cell (2) is held in the edge region (6) thereof between two frame elements (12, 14, 16). According to another aspect, each storage cell comprises current conductors (8, 10) in the edge region (6) and electric contacting between current conductors (8, 10) of successive storage cells (2) is carried out via the tensioning device (22, 24, 26, 222) by way of a non-positive fit.

Owner:LI TEC BATTERY

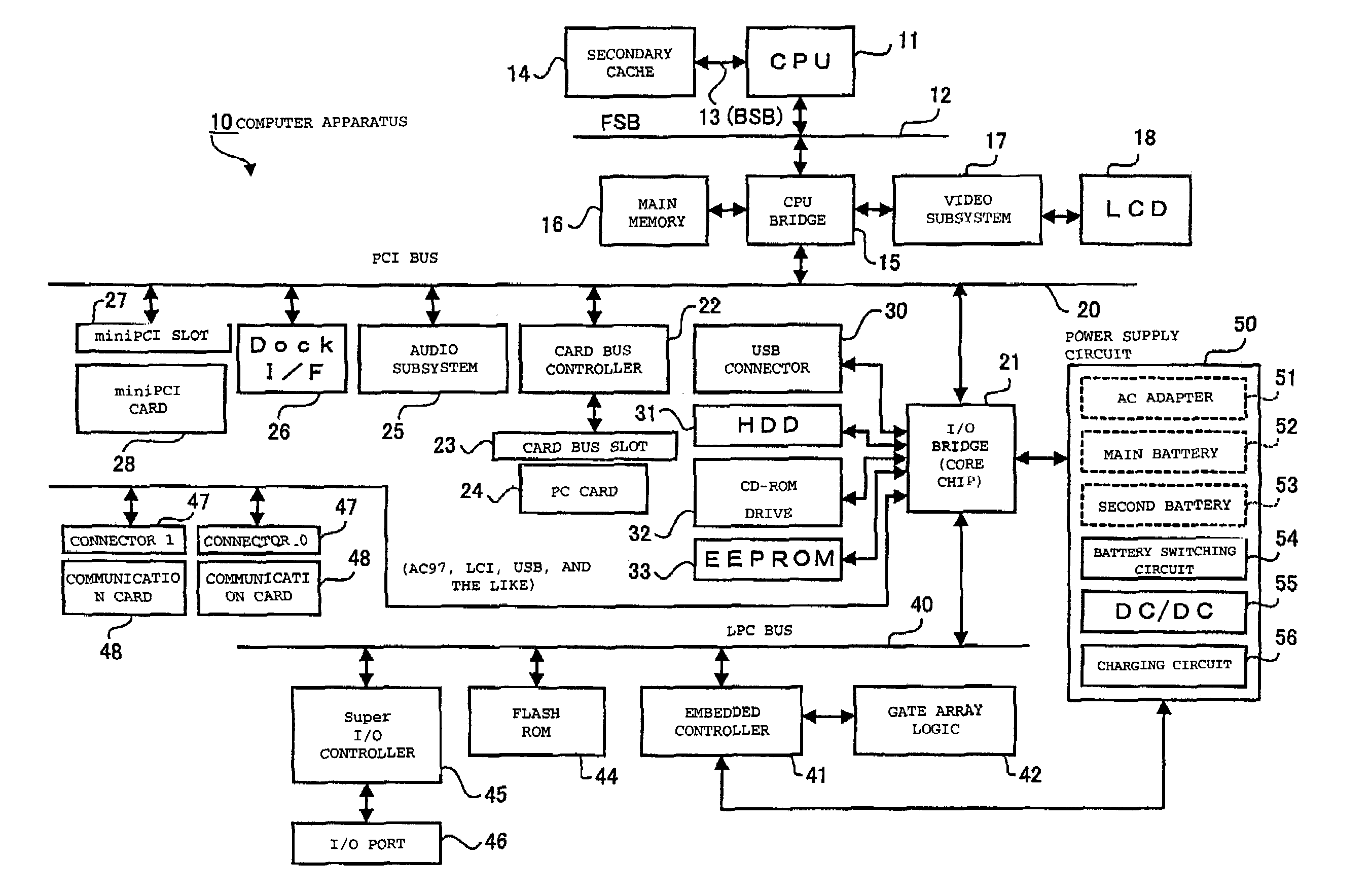

Optimized battery performance

InactiveUS7494729B2Primary cell to battery groupingSequential battery dischargeElectrical batteryEngineering

In an electrical instrument to which a plurality of battery blocks and / or a plurality of batteries are detachably connectable, to prevent a phenomenon that only specific battery and battery block are deteriorated. A hybrid battery connectable to a body of an electrical instrument consuming electrical power includes: a cell block which includes one or more battery cells, and supplies electrical power to the body of the electrical instrument by discharging after being charged; and a cell block which includes one or more battery cells, supplies electrical power to the body of the electrical instrument by discharging after being charged, and becomes active selectively with the former cell block. In the hybrid battery, a CPU selects a cell block becoming active based on the number of charge / discharge cycles of the former cell block and the number of charge / discharge cycles of the latter cell block.

Owner:LENOVO GLOBAL TECH INT LTD

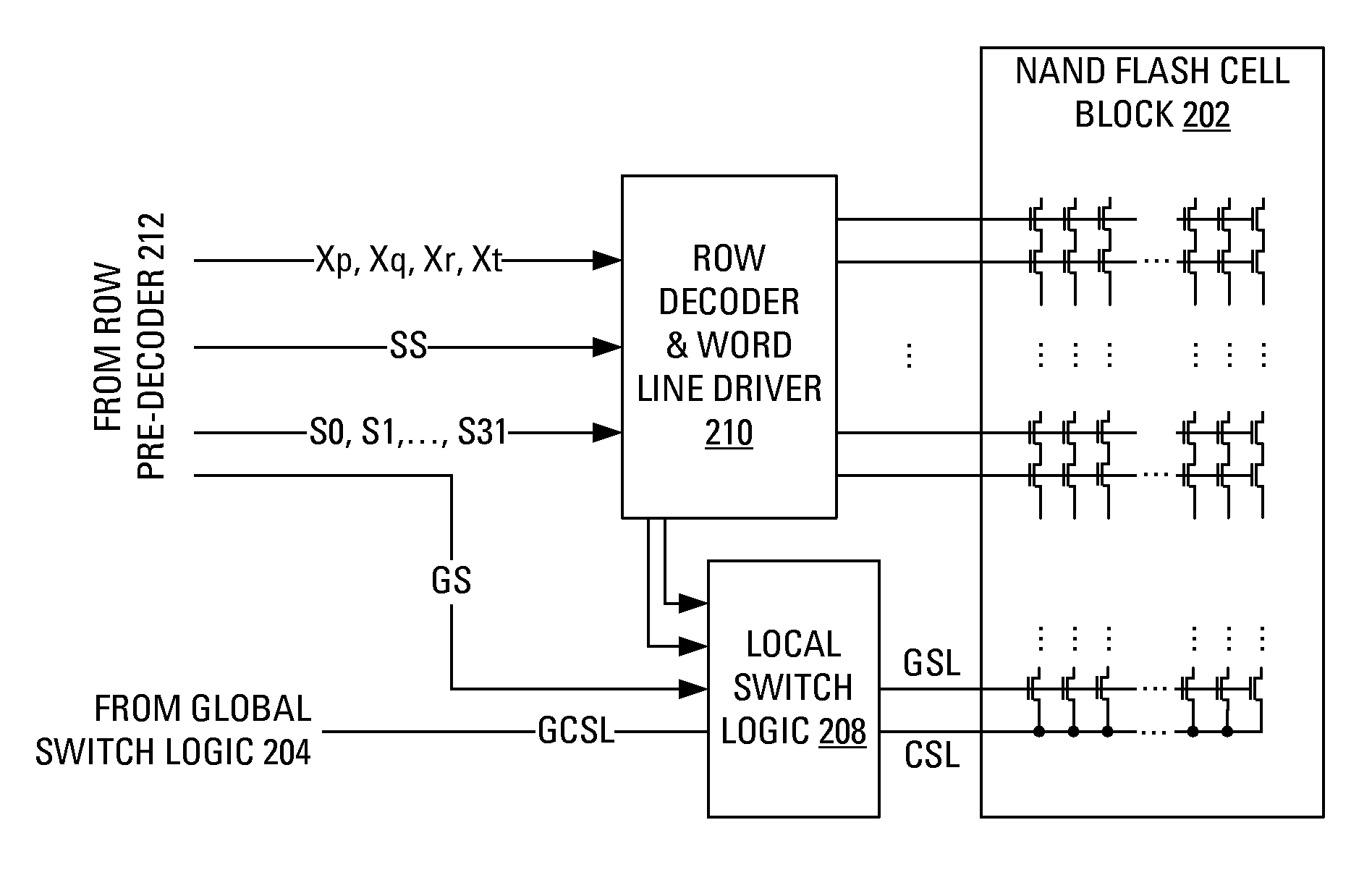

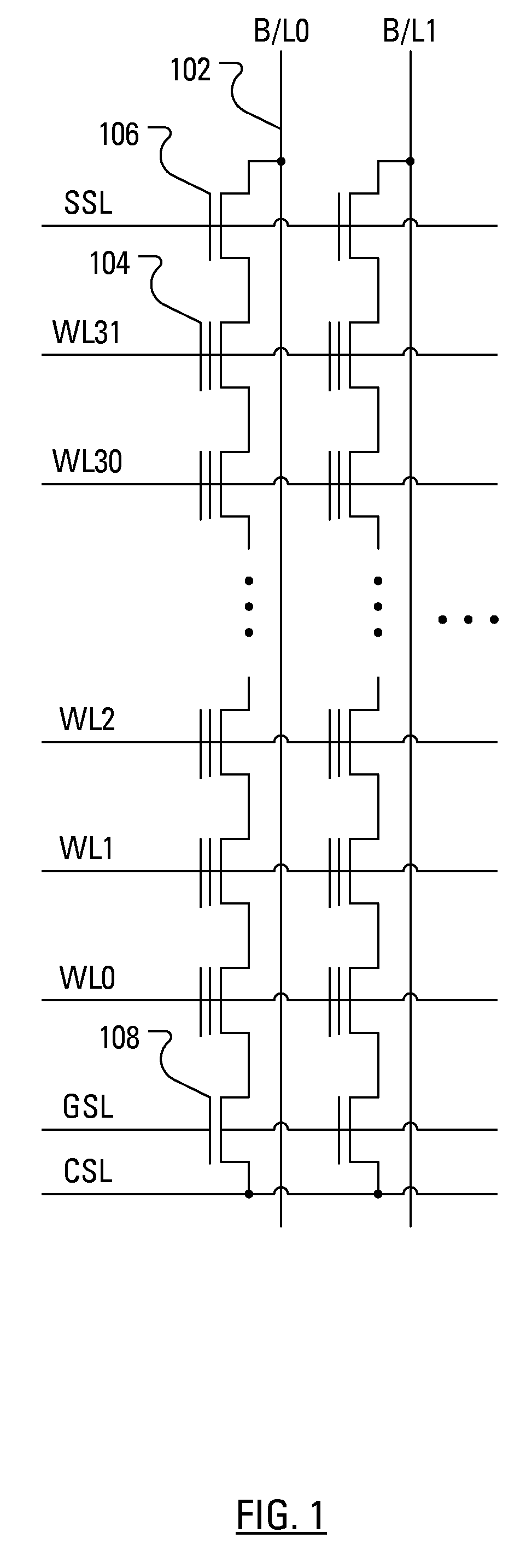

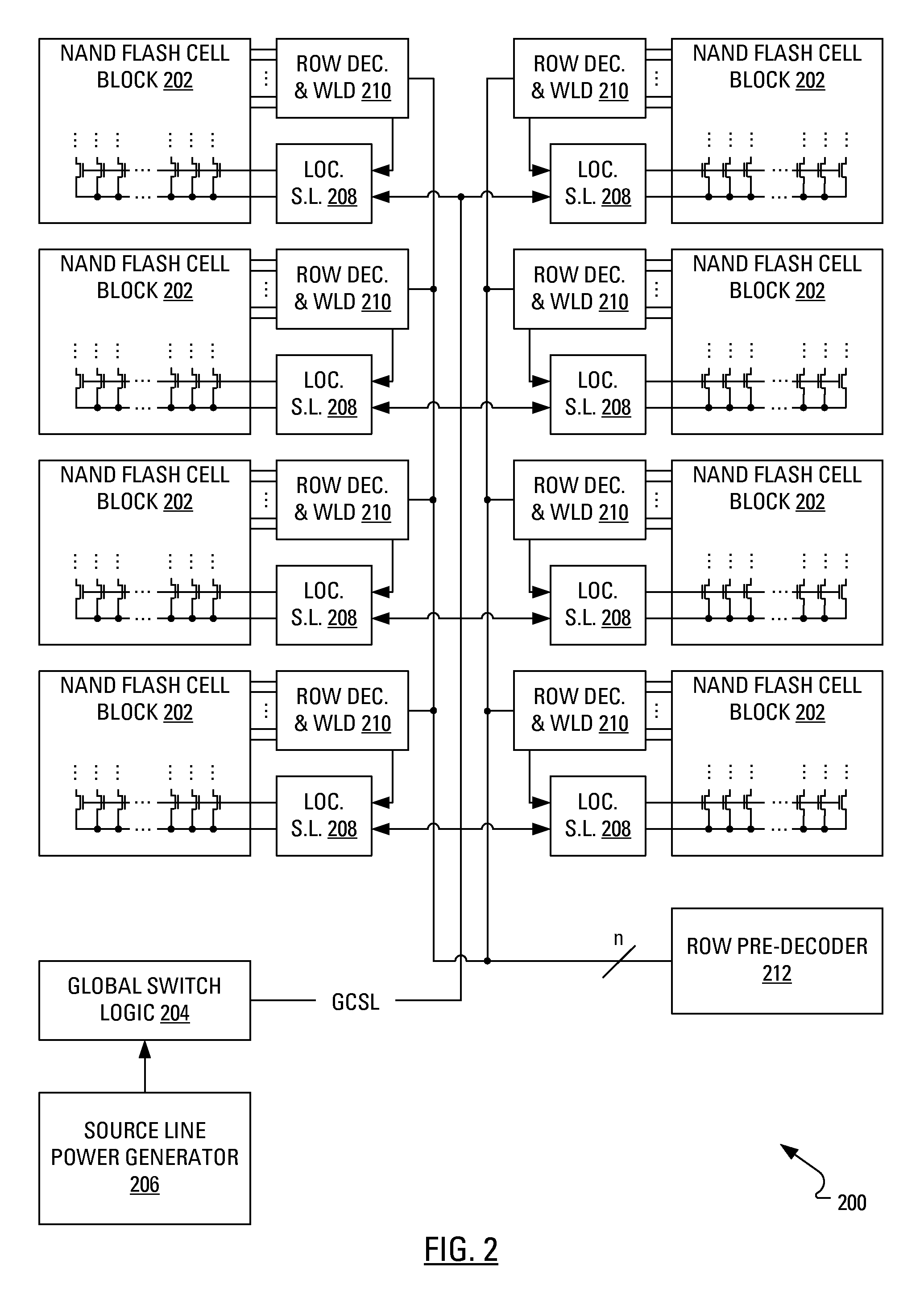

Hierarchical common source line structure in NAND flash memory

Each memory cell string in a generic NAND flash cell block connects to a Common Source Line (CLS). A value for applying to the CSL is centrally generated and distributed to a local switch logic unit corresponding to each NAND flash cell block. For source-line page programming, the distribution line may be called a Global Common Source Line (GCSL). In an array of NAND flash cell blocks, only one NAND flash cell block is selected at a time for programming. To reduce power consumption, only the selected NAND flash cell block receives a value on the CSL that is indicative of the value on the GCSL. Additionally, the CSLs of non-selected NAND flash cell blocks may be disabled through an active connection to ground.

Owner:MOSAID TECH

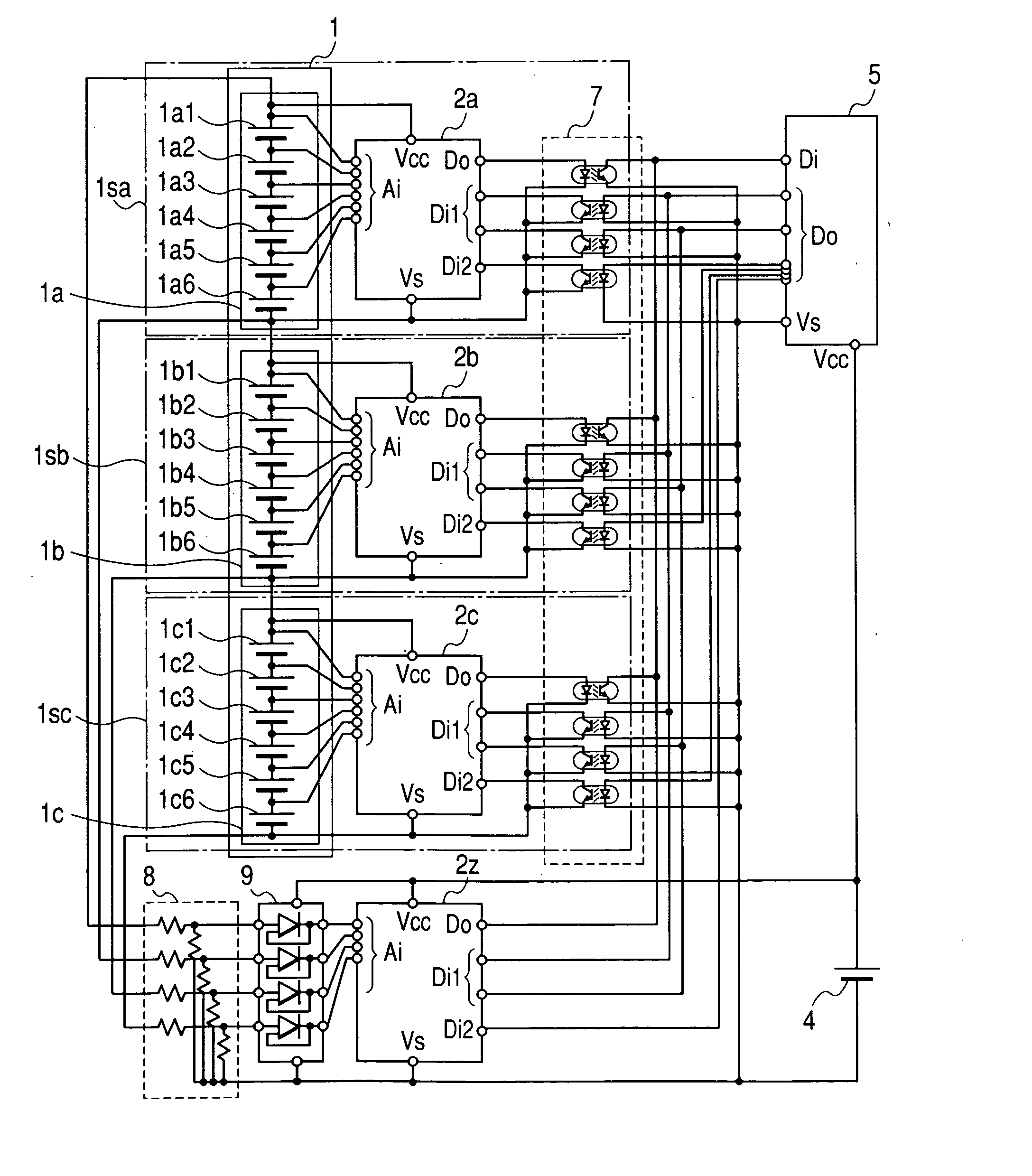

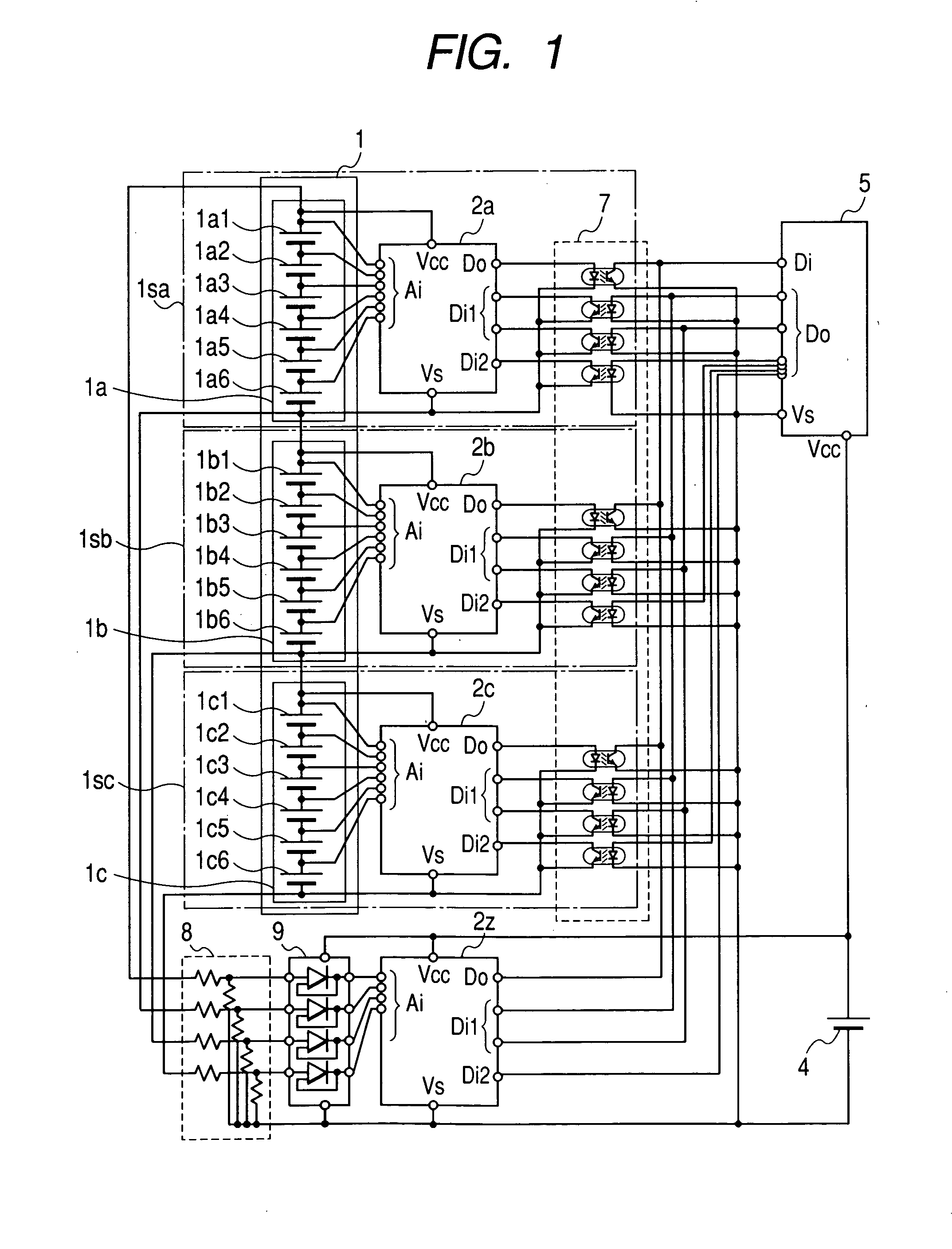

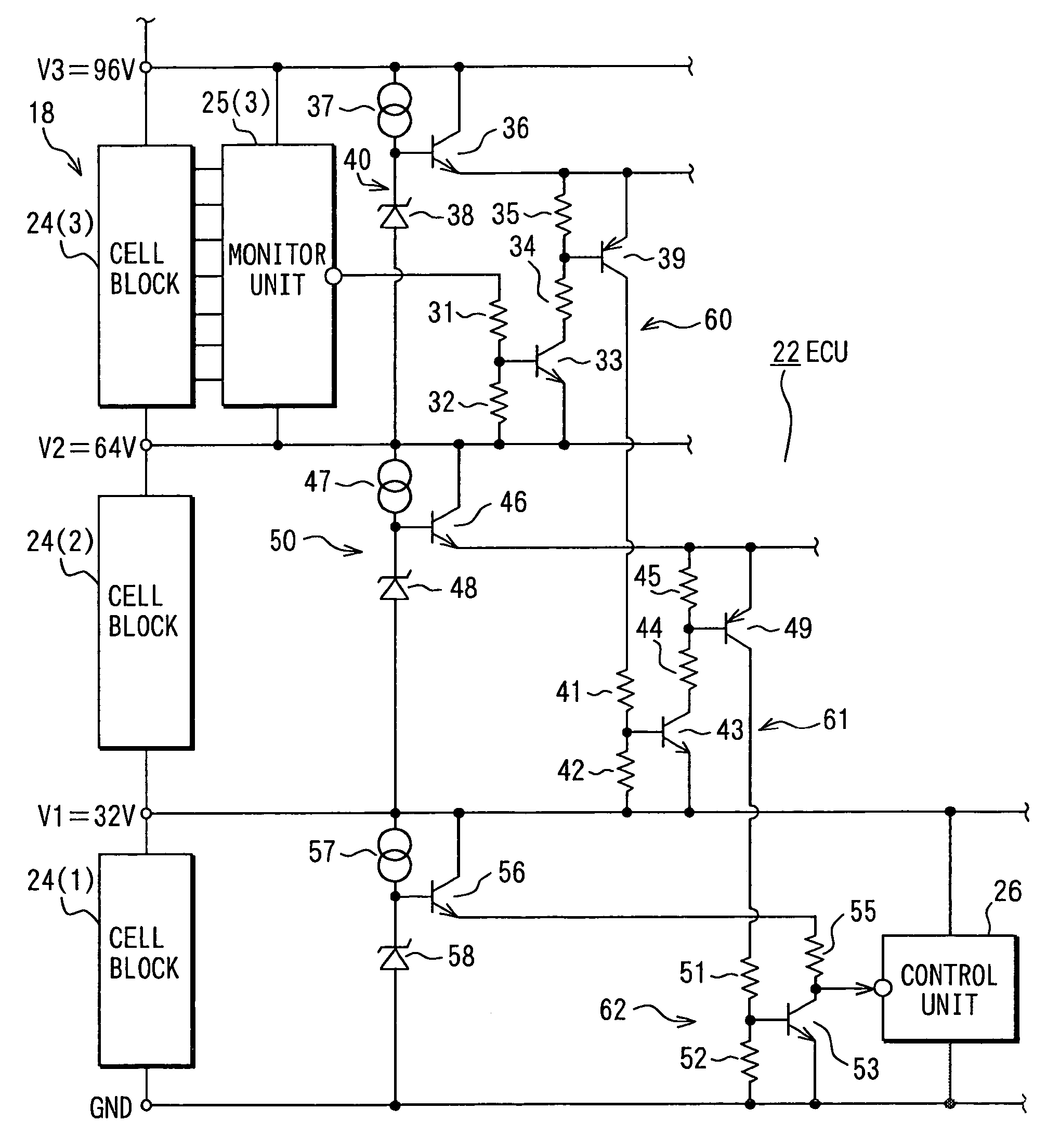

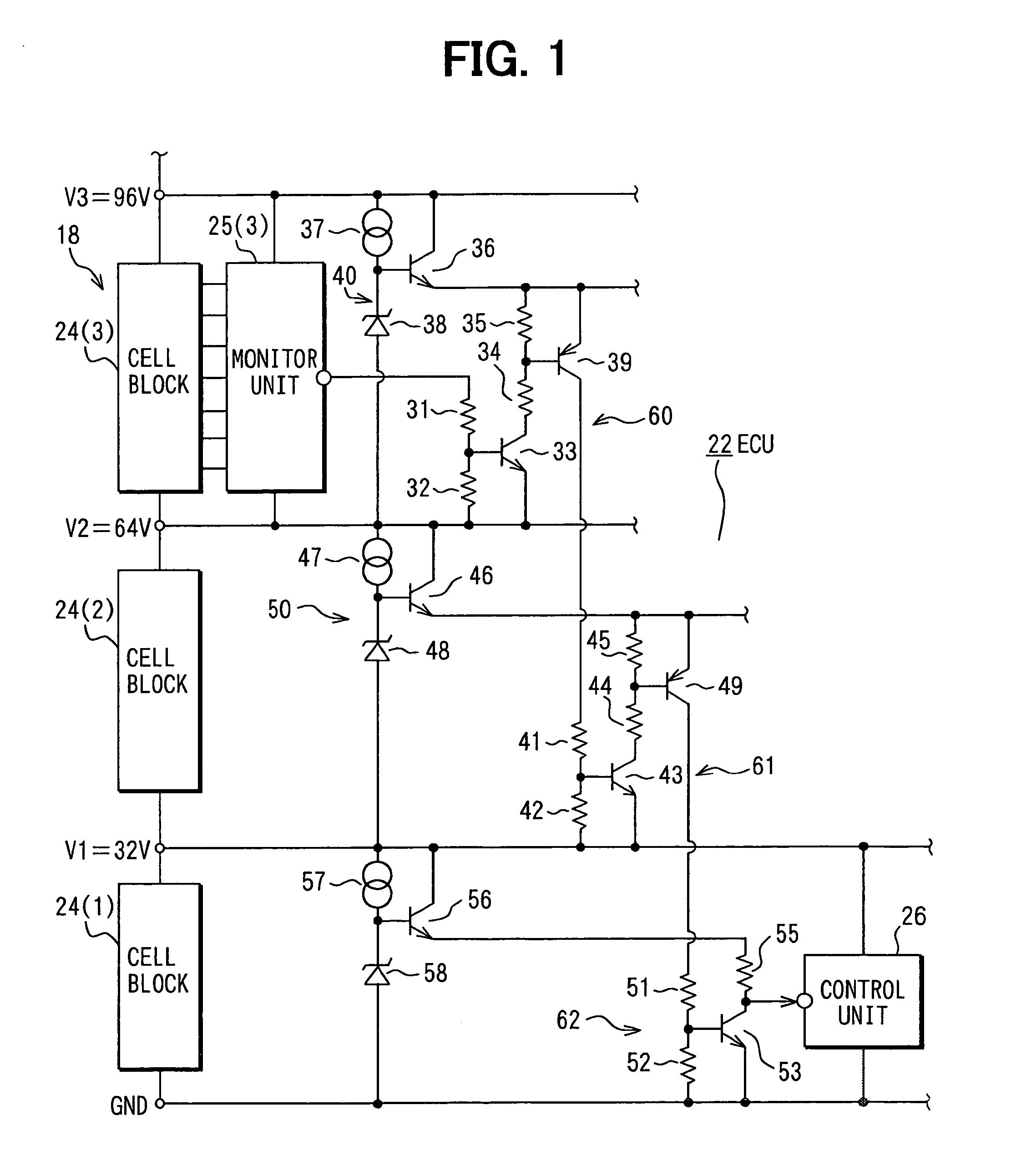

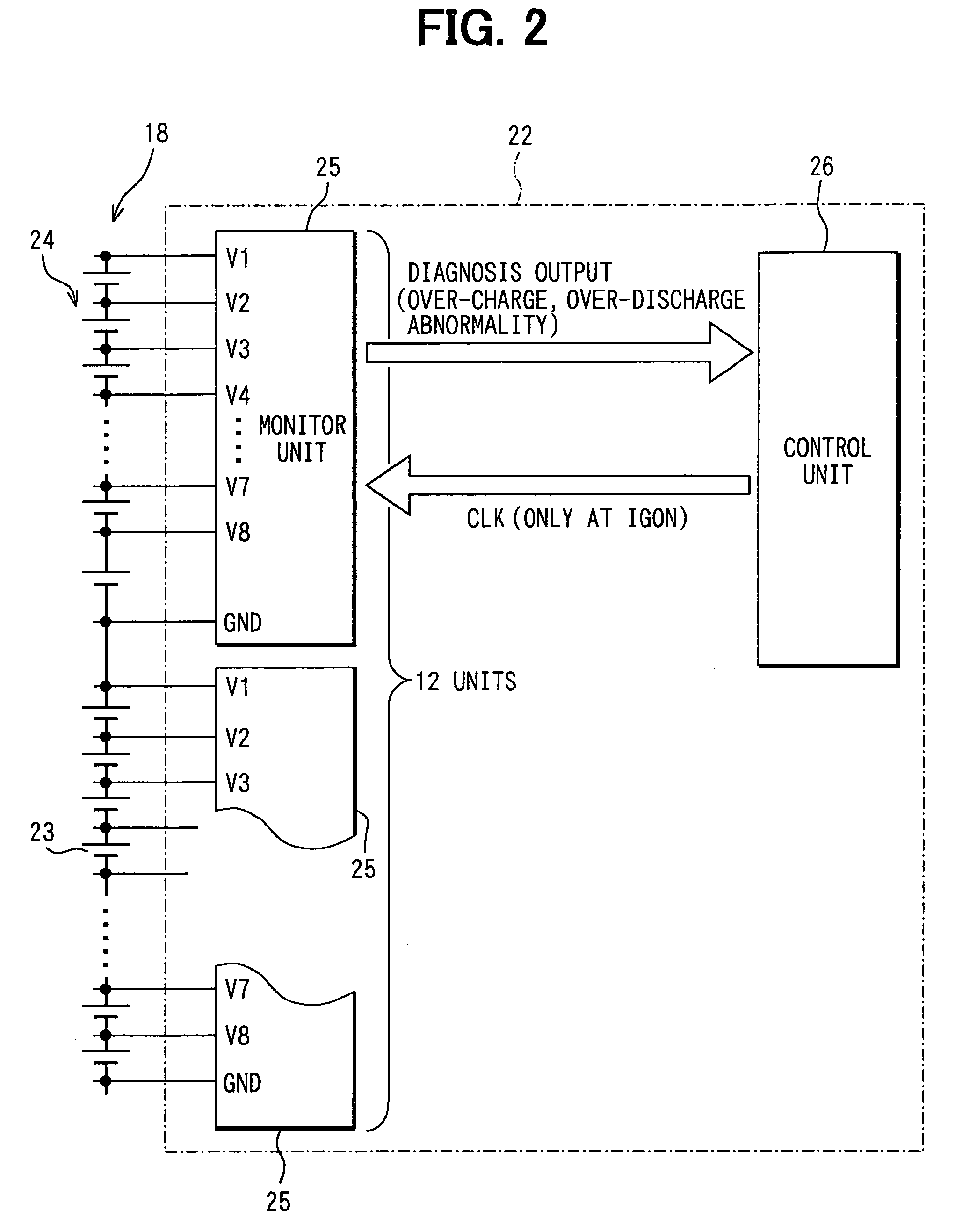

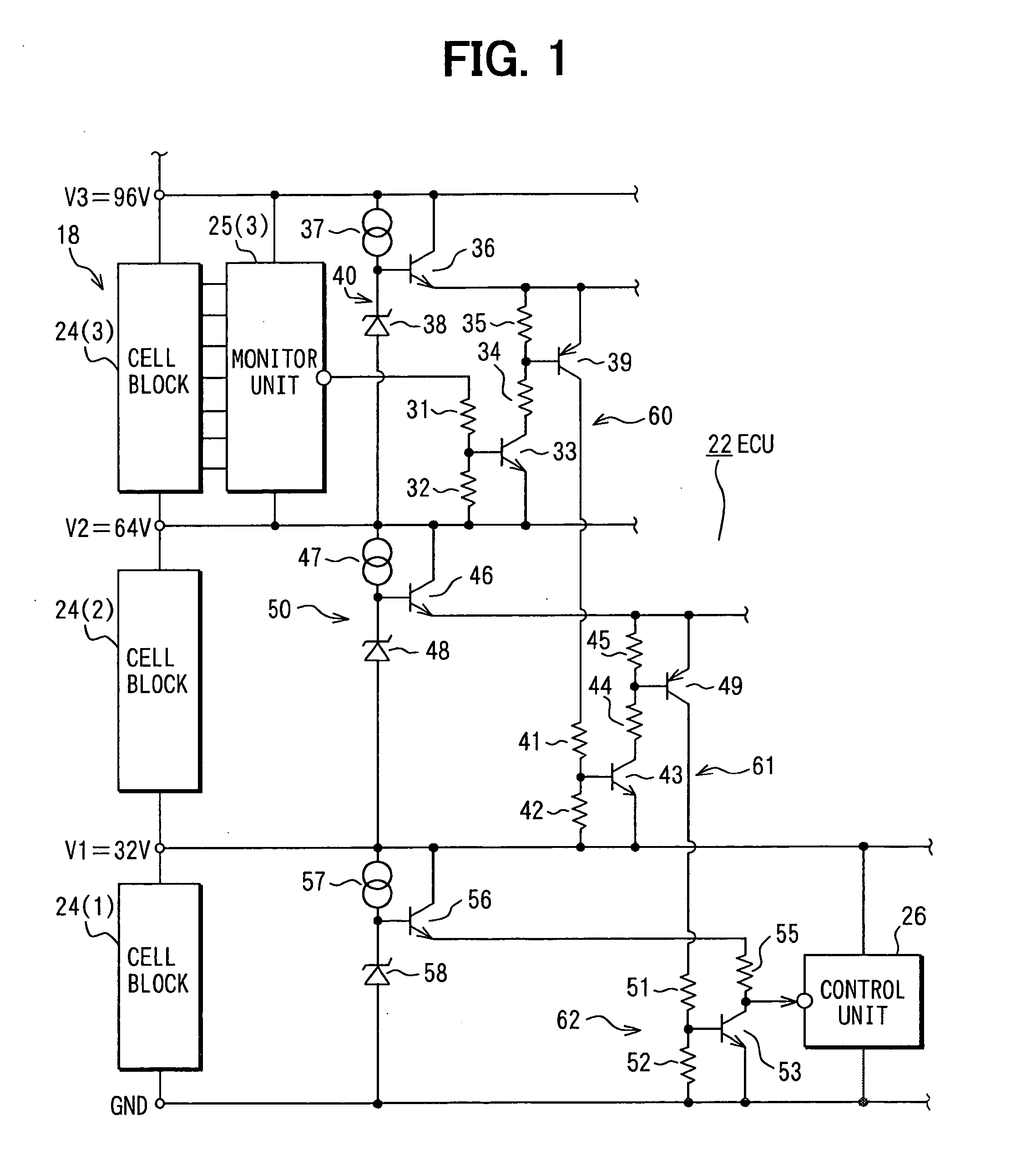

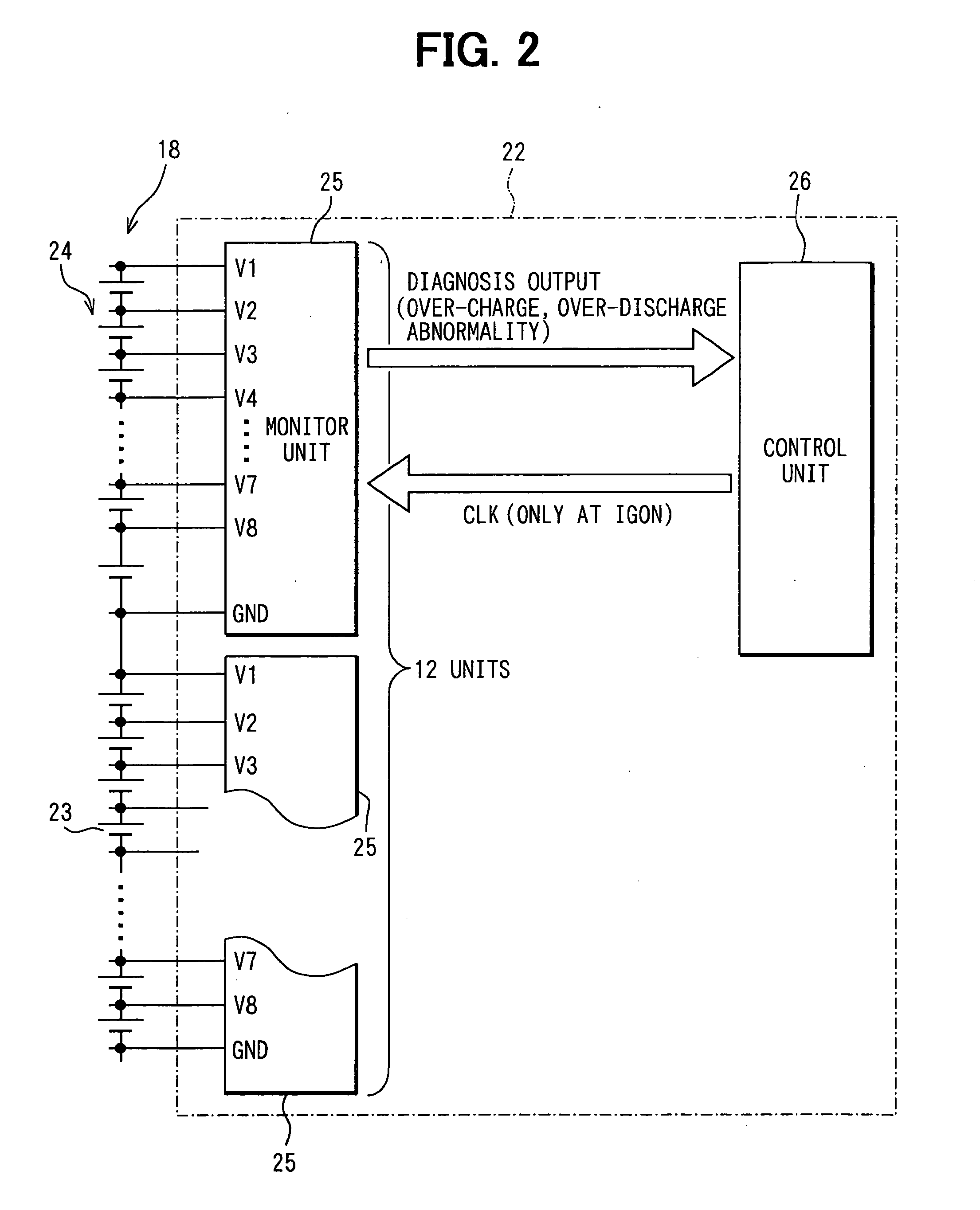

Circuit system for a battery electronic control unit

InactiveUS7471064B2Address rising pricesSmall sizeCharge equalisation circuitSolid-state devicesLow voltageEngineering

A battery ECU controls a main battery composed of a plurality of battery cells connected to each other in series. The battery cells are grouped into cell blocks each having a cell-block monitor circuit. A control unit controls charging / discharging processes on the basis of signals output by the cell-block monitor circuit. A signal output by a cell-block monitor circuit on a high-voltage side turns on a transistor for propagating a signal to a cell-block monitor circuit on a middle-voltage side. In the cell-block monitor circuit on a middle-voltage side, the propagated signal turns on another transistor for further propagating a signal to a cell-block monitor circuit on a low-voltage side. In the cell-block monitor circuit on a low-voltage side, the propagated signal turns on a further transistor for outputting a signal to a control unit.

Owner:DENSO CORP

Method of erasing NAND flash memory device

Provided is concerned with a method of erasing a NAND flash memory device, capable of restraining an erasing disturbance fail arising from a deselected cell block and improving a product yield of the device by applying a negative voltage to a well of a high voltage transistor forming an X-decoder during an erasing operation in the NAND flash memory device.

Owner:STMICROELECTRONICS SRL +1

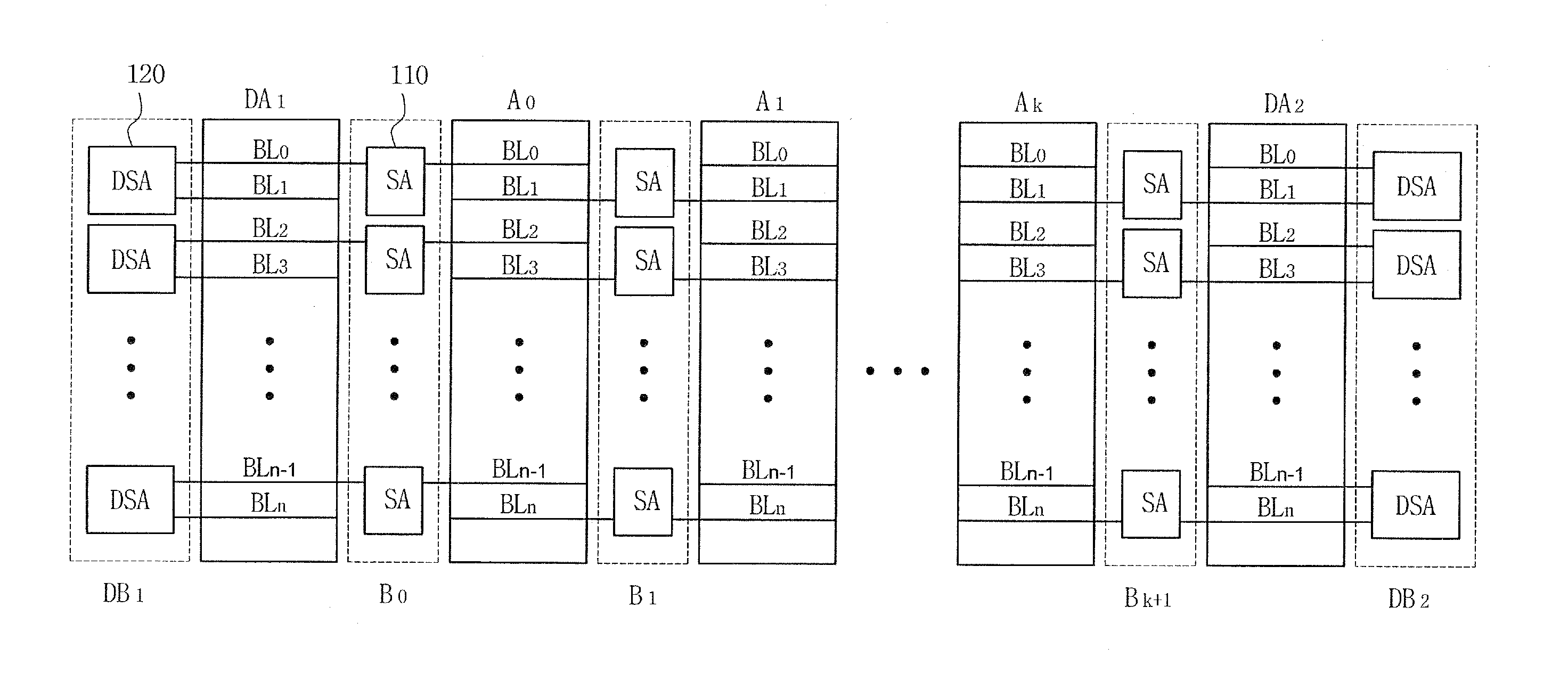

Semiconductor memory device having dummy sense amplifiers and methods of utilizing the same

InactiveUS20070041260A1Data augmentationIncrease the refresh marginDigital storageBit lineAudio power amplifier

A semiconductor memory device having dummy sense amplifiers and a method of utilizing the same are provided. Embodiments of the semiconductor memory device may include at least one dummy cell block including dummy cells and memory cells. Normal bit lines connecting the memory cells in the dummy cell block in a first direction and dummy bit lines connecting the dummy cells in the first direction. A dummy sense amplifier is also included for connecting any two of the normal bit lines and the dummy bit lines. Some of the embodiments may improve the sensing margin and refresh margin in sensing memory cells in the dummy cell, as well as increasing the redundancy efficiency and utilization of the dummy cells.

Owner:SAMSUNG ELECTRONICS CO LTD

Circuit system for a battery electronic control unit

InactiveUS20050194931A1Address rising pricesSmall sizeCharge equalisation circuitSolid-state devicesLow voltageHigh pressure

A battery ECU controls a main battery composed of a plurality of battery cells connected to each other in series. The battery cells are grouped into cell blocks each having a cell-block monitor circuit. A control unit controls charging / discharging processes on the basis of signals output by the cell-block monitor circuit. A signal output by a cell-block monitor circuit on a high-voltage side turns on a transistor for propagating a signal to a cell-block monitor circuit on a middle-voltage side. In the cell-block monitor circuit on a middle-voltage side, the propagated signal turns on another transistor for further propagating a signal to a cell-block monitor circuit on a low-voltage side. In the cell-block monitor circuit on a low-voltage side, the propagated signal turns on a further transistor for outputting a signal to a control unit.

Owner:DENSO CORP