Semiconductor wafer examination method and semiconductor chip manufacturing method

a semiconductor and wafer technology, applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of failure of some semiconductor devices and semiconductor chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

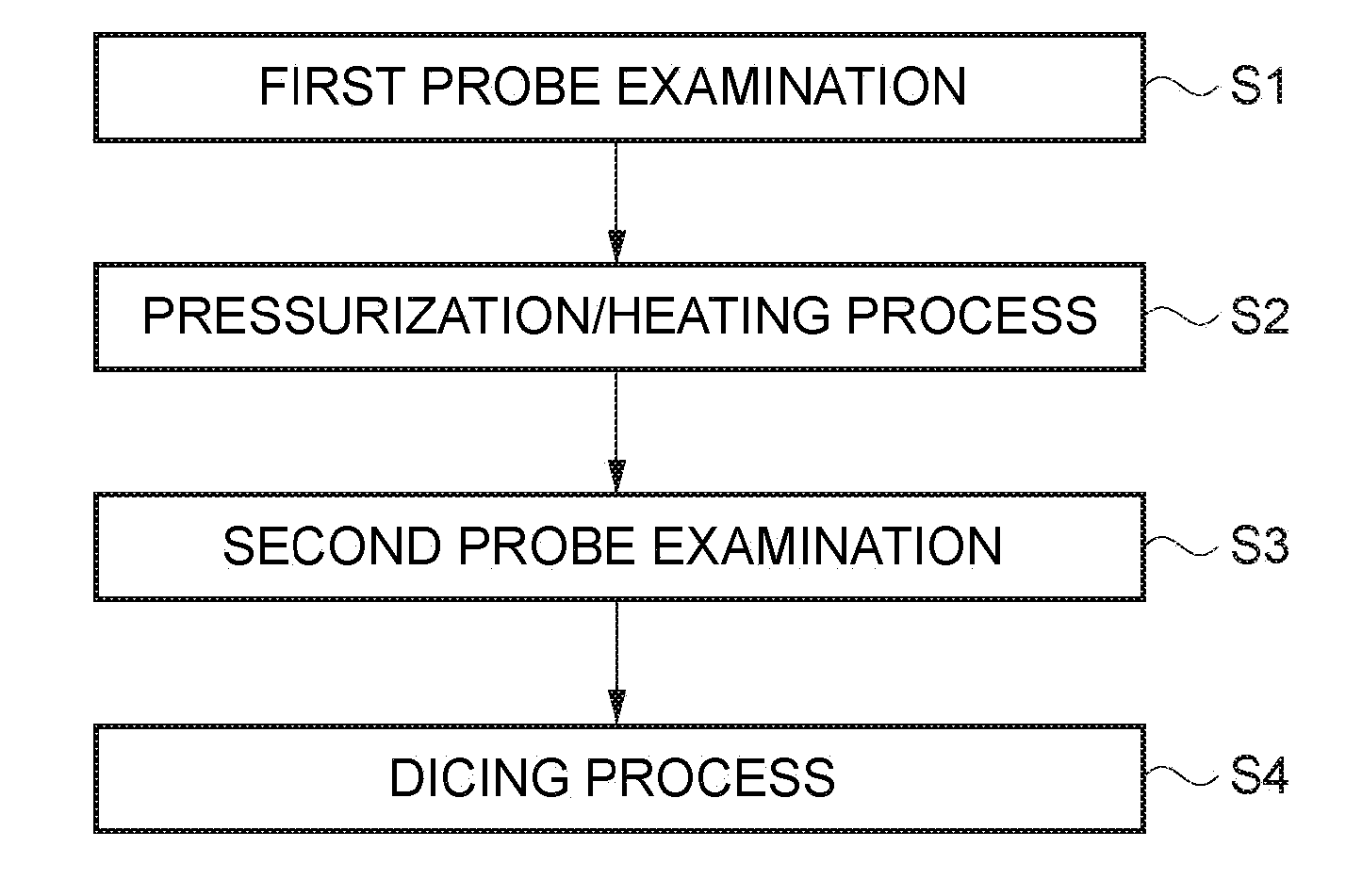

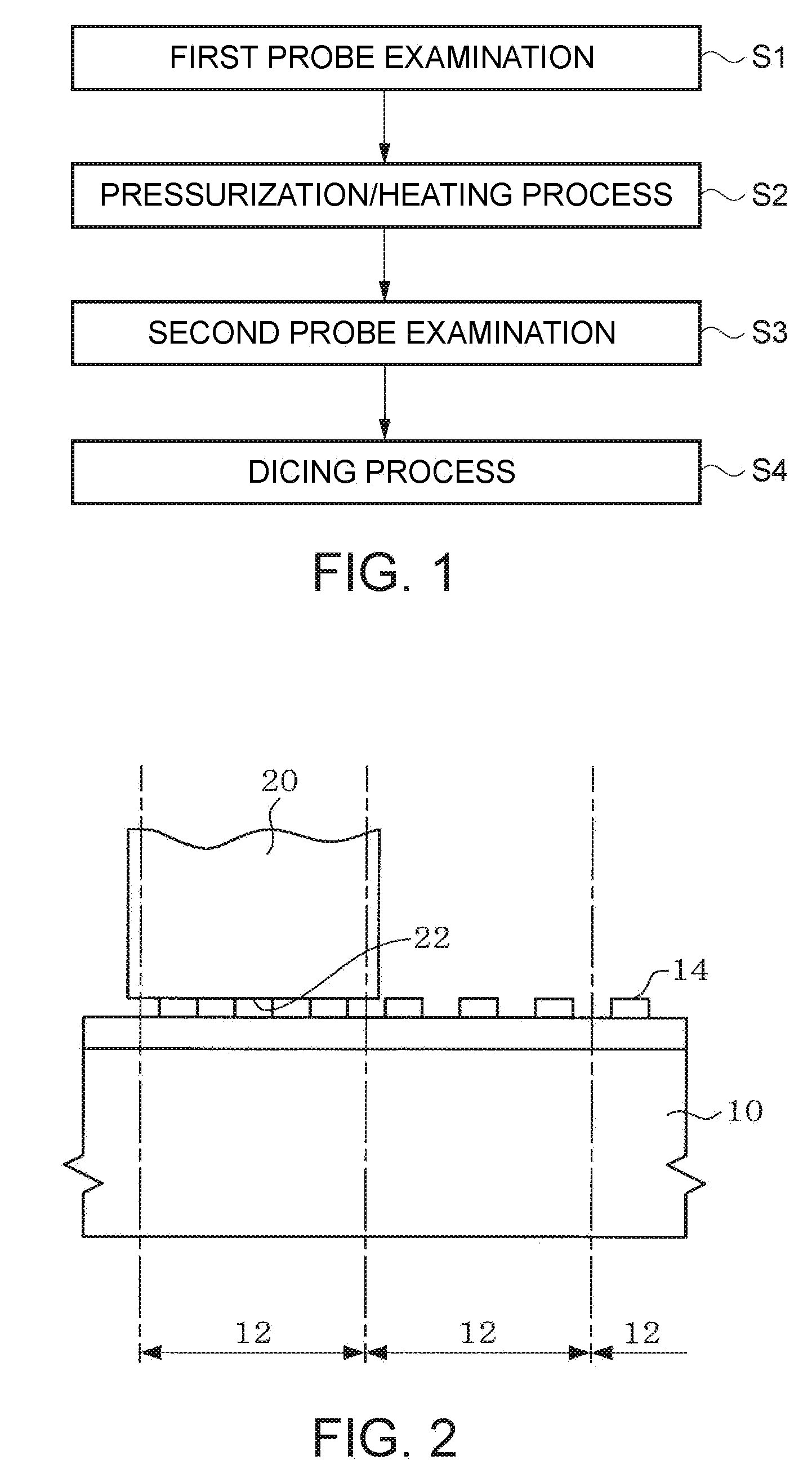

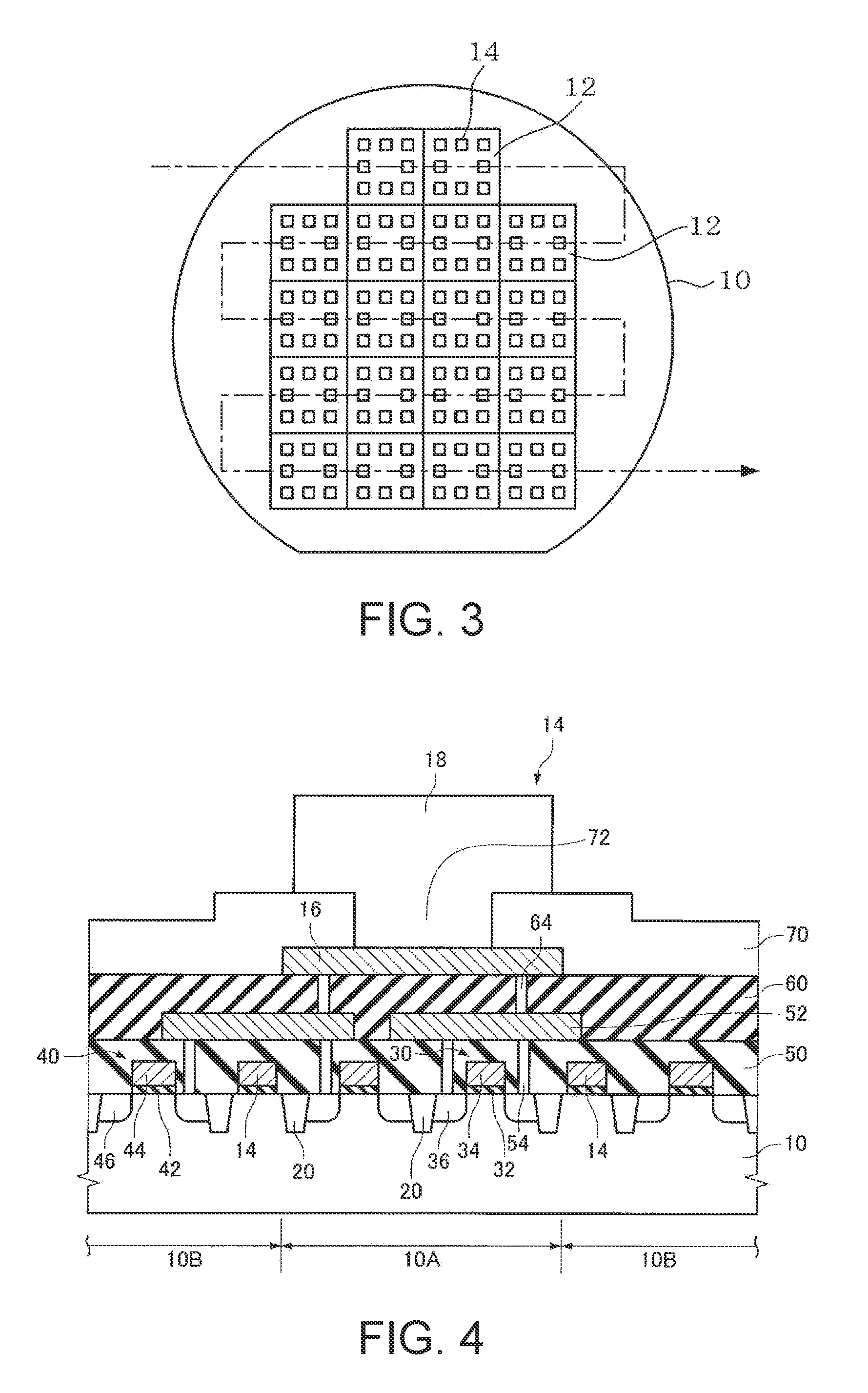

[0021] In the below, an exemplary embodiment of the invention is described by referring to the accompanying drawings. FIG. 1 is a diagram for illustrating a semiconductor wafer examination method of the embodiment. FIG. 2 is a cross sectional diagram schematically showing a process of the semiconductor wafer examination method. FIG. 3 is a schematic plan view of a wafer being an examination object. FIG. 4 is a schematic cross sectional view of a part of a chip area.

[0022] In the embodiment, a wafer is prepared for examination use. As shown in FIGS. 2 and 3, this wafer is configured by a semiconductor substrate 10 formed with a plurality of chip areas 12, which serve as semiconductor chips after wafer dicing. The chip areas 12 are provided with an integrated circuit that is not shown. The integrated circuit is not specifically defined by configuration, and may include an active element such as transistor or a passive element such as resistor, coil, or capacitor.

[0023] The chip area...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More