Packaging structure

a packaging structure and packaging technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problem of improper filling of underfill, and achieve the effect of reliable bonding effect and improved process yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

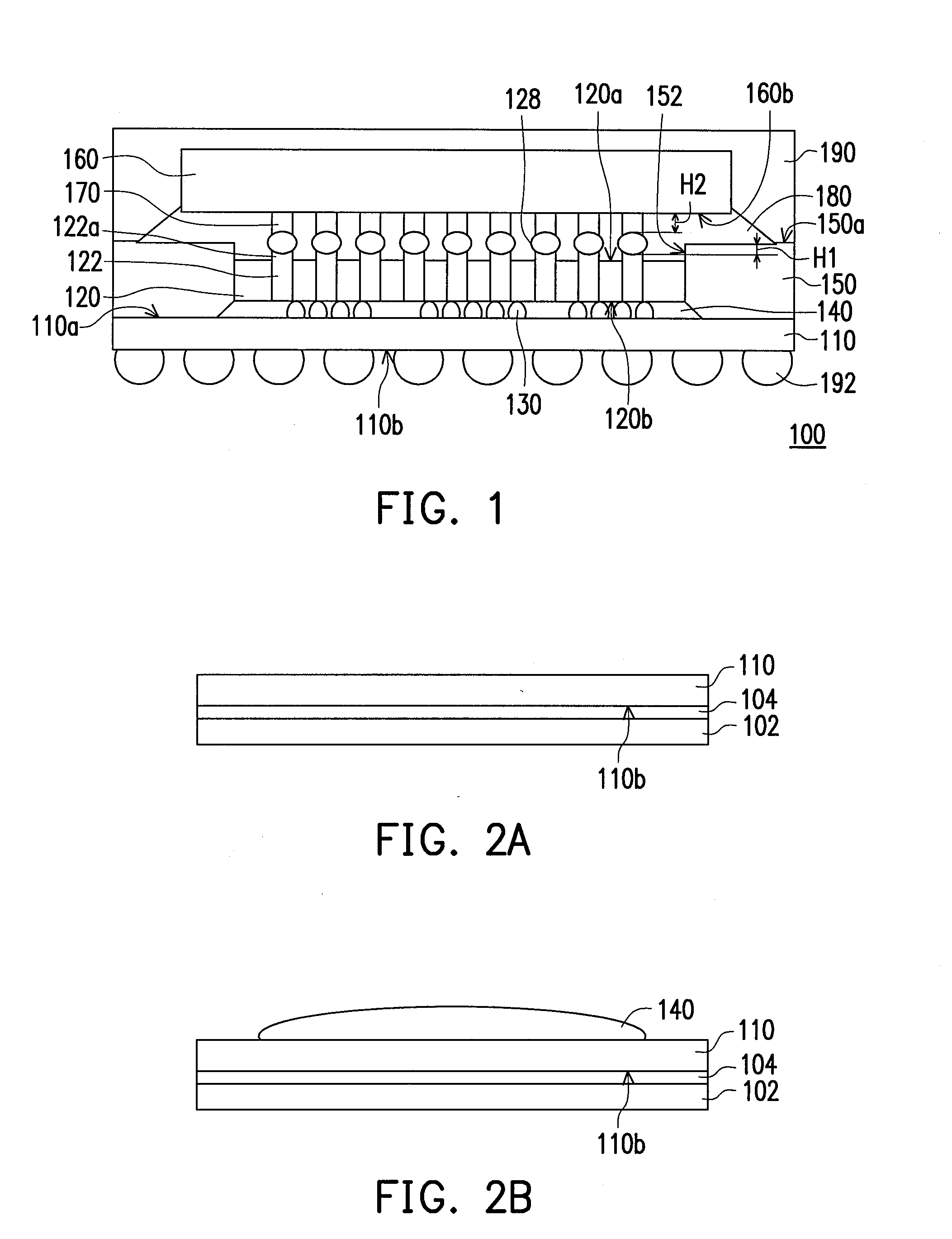

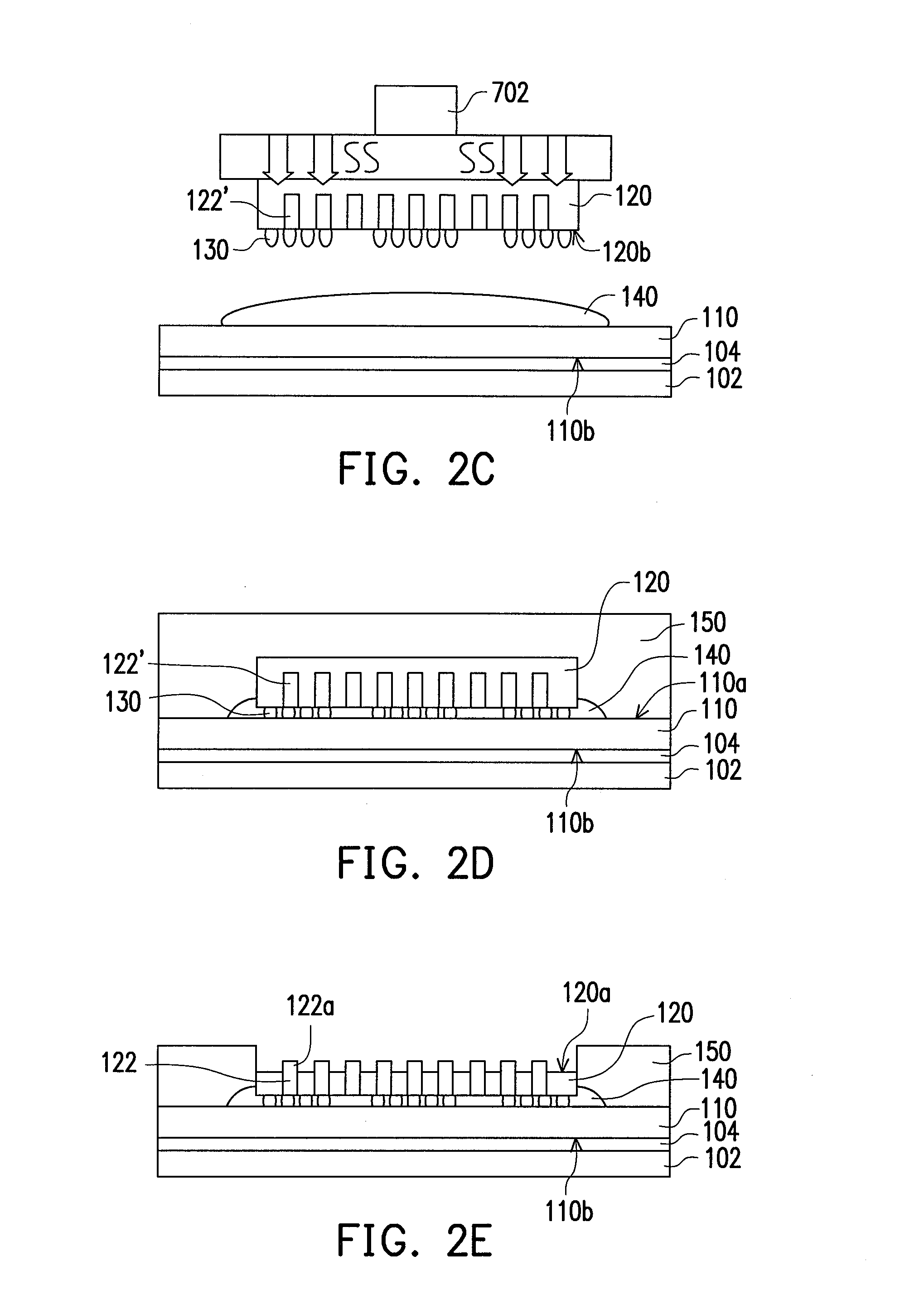

[0042]The present invention uses pillar bumps to connect an upper second chip and a lower first chip so as to control a gap between the first chip and the second chip and overcome a height difference between the first chip and a molding compound surrounding the first chip caused by forming through silicon vias. The aforementioned concept can be applied to various stacked semiconductor device packages, and some package structures and package processes of stacked semiconductor device package are illustrated in the following embodiments.

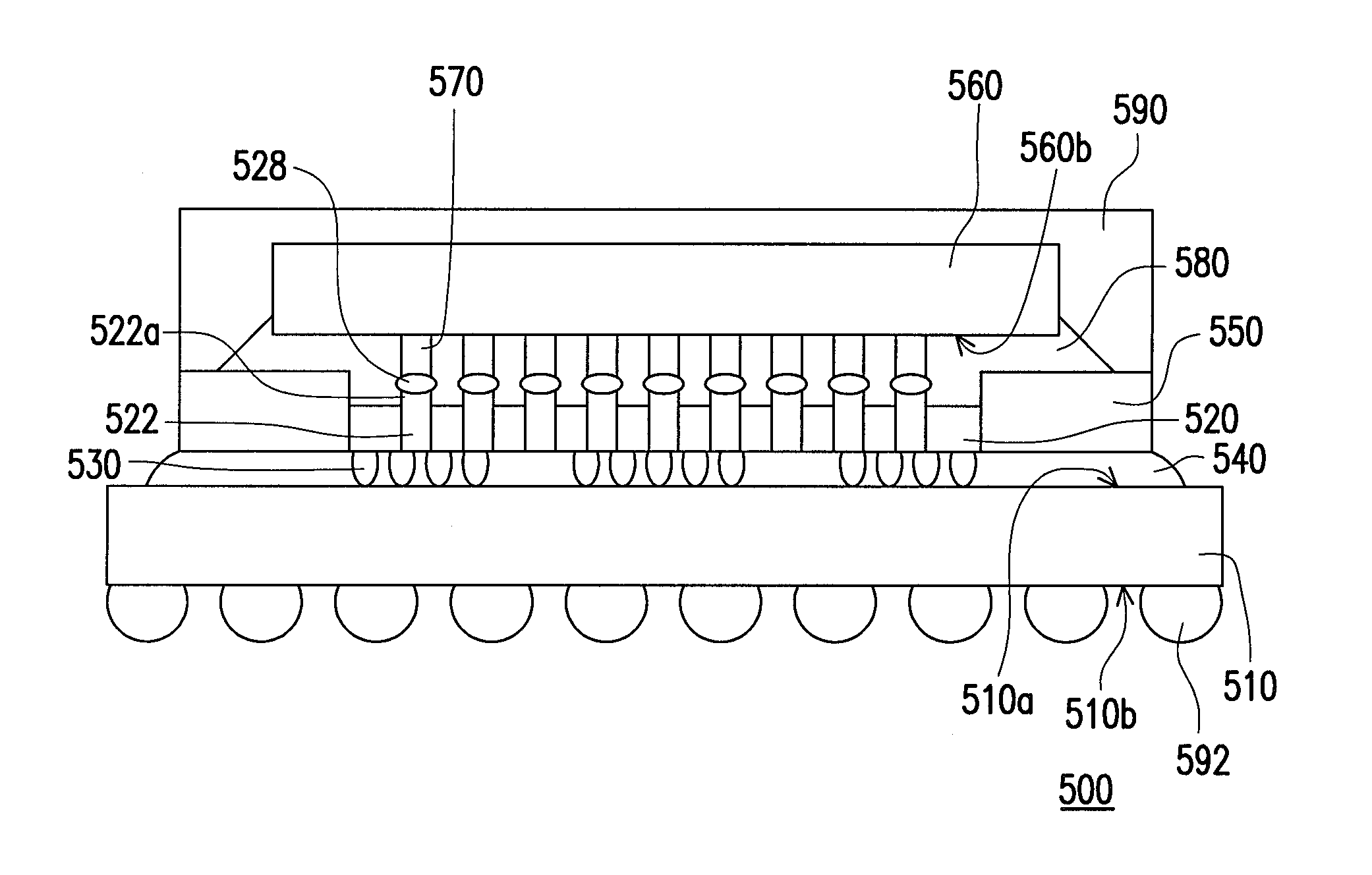

[0043]FIG. 1 illustrates a package structure according to an embodiment of the present invention. As shown in FIG. 1, the package structure 100 of the present embodiment comprises a circuit substrate 110, a first chip 120, a plurality of first bumps 130, a first underfill 140, a first molding compound 150, a second chip 160, a plurality of pillar bumps 170 and a second underfill 180. The circuit substrate 110 has a top surface 110a and a bottom surface ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More