Digital-To-Analog Converter Using Nonlinear Capacitance Compensation

a digital-to-analog converter and nonlinear capacitance compensation technology, applied in the direction of digital-analog convertors, electronic switching, pulse techniques, etc., can solve the problems of parasitic capacitance, unwanted capacitance, affecting the linearity of electronic devices,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018]Overview

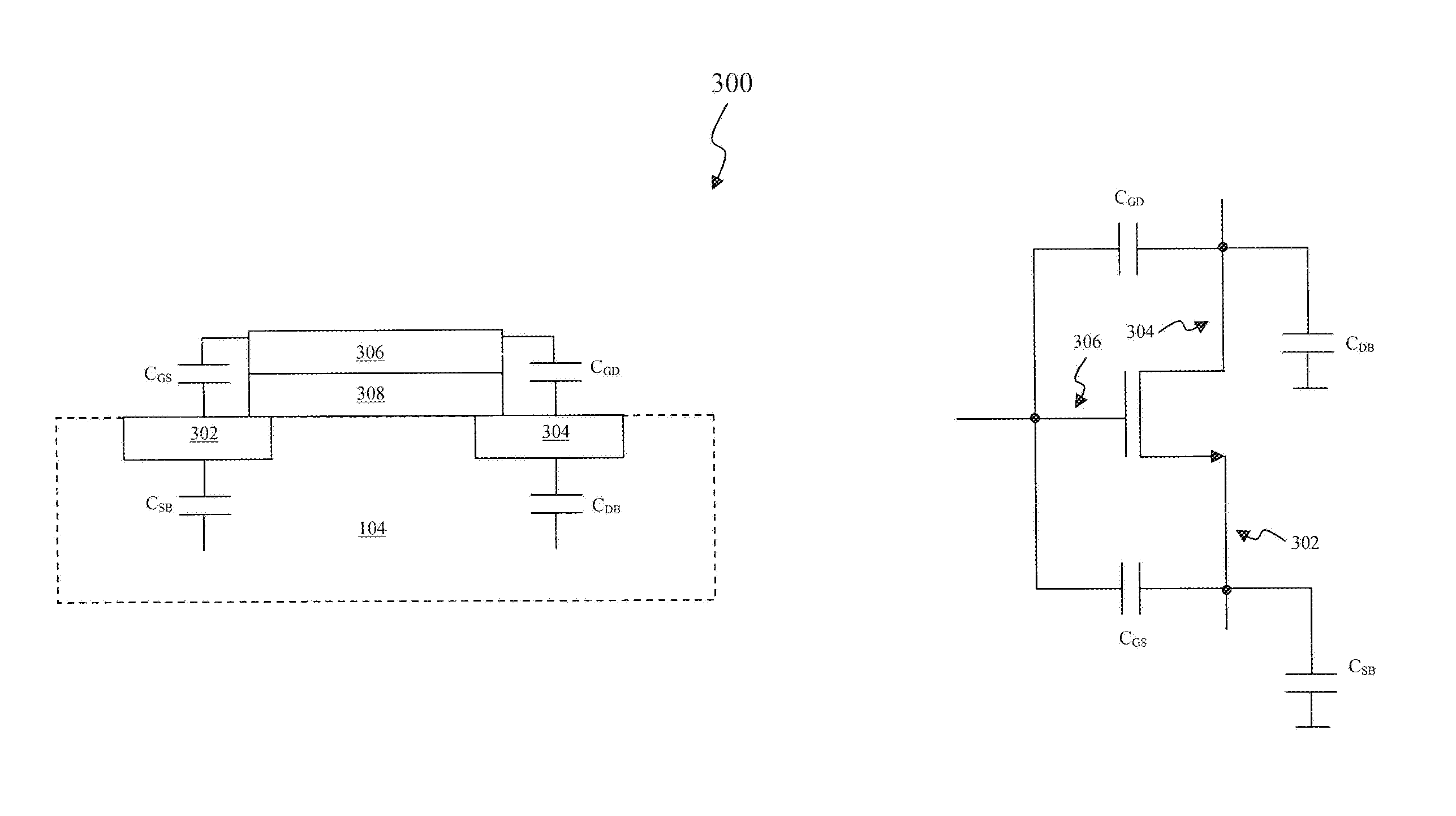

[0019]A semiconductor device fabrication operation is commonly used to manufacture one or more integrated circuits onto a semiconductor substrate. The semiconductor device fabrication operation forms one or more transistors onto an arrangement of fabrication layers to form the one or more integrated circuits which introduces unwanted capacitances, often referred to as parasitic capacitances, into the one or more transistors. The various systems and methods disclosed herein include one or more compensation modules that, when combined with the parasitic capacitances of the one or more transistors, ideally linearizes the non-linearity caused by the parasitic capacitances of the one or more transistors. For example, the compensation module of the present disclosure incorporates a non-linear or a piecewise linear transfer function that is inversely related to the parasitic capacitances of the one or more transistors.

[0020]Integrated Circuit

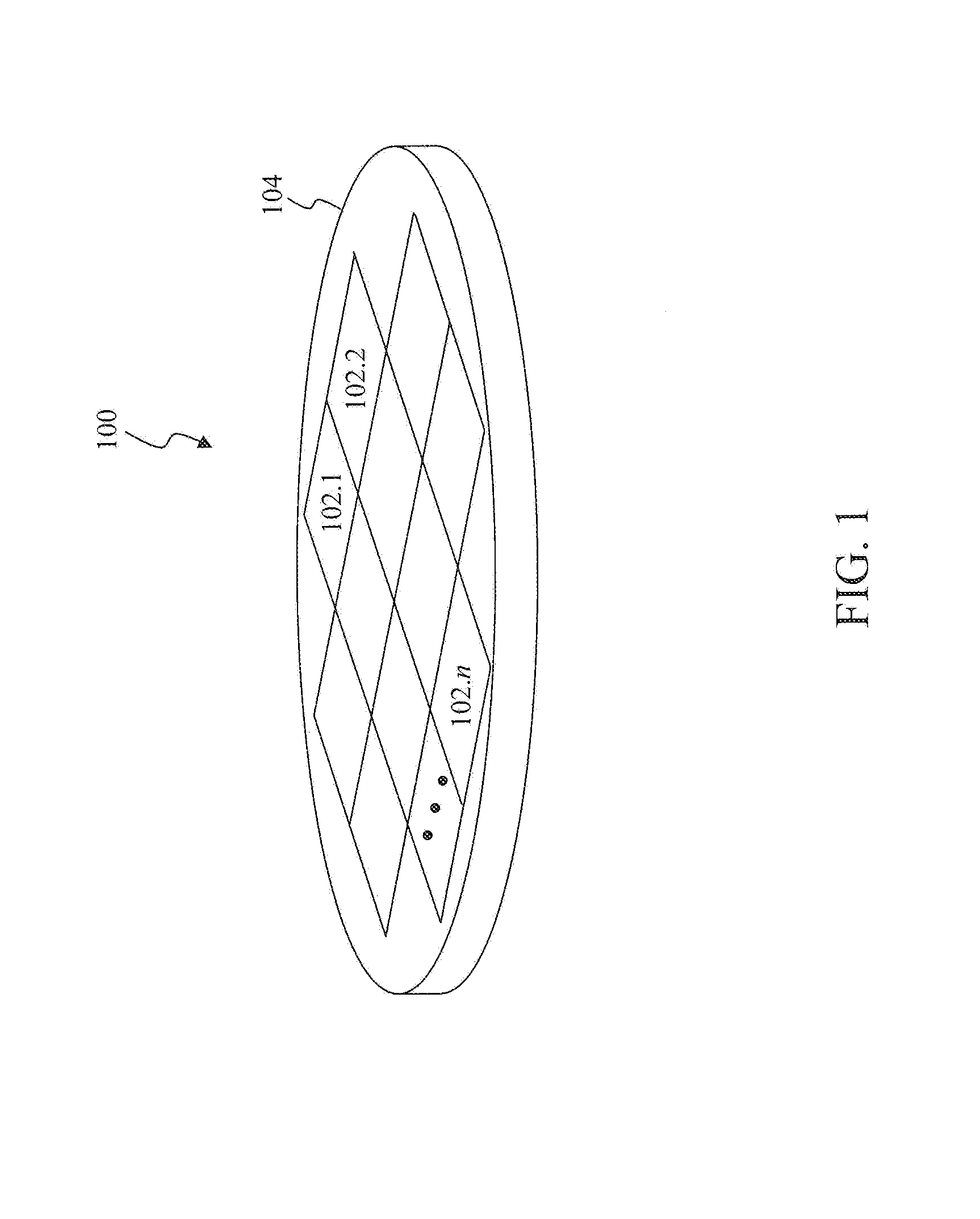

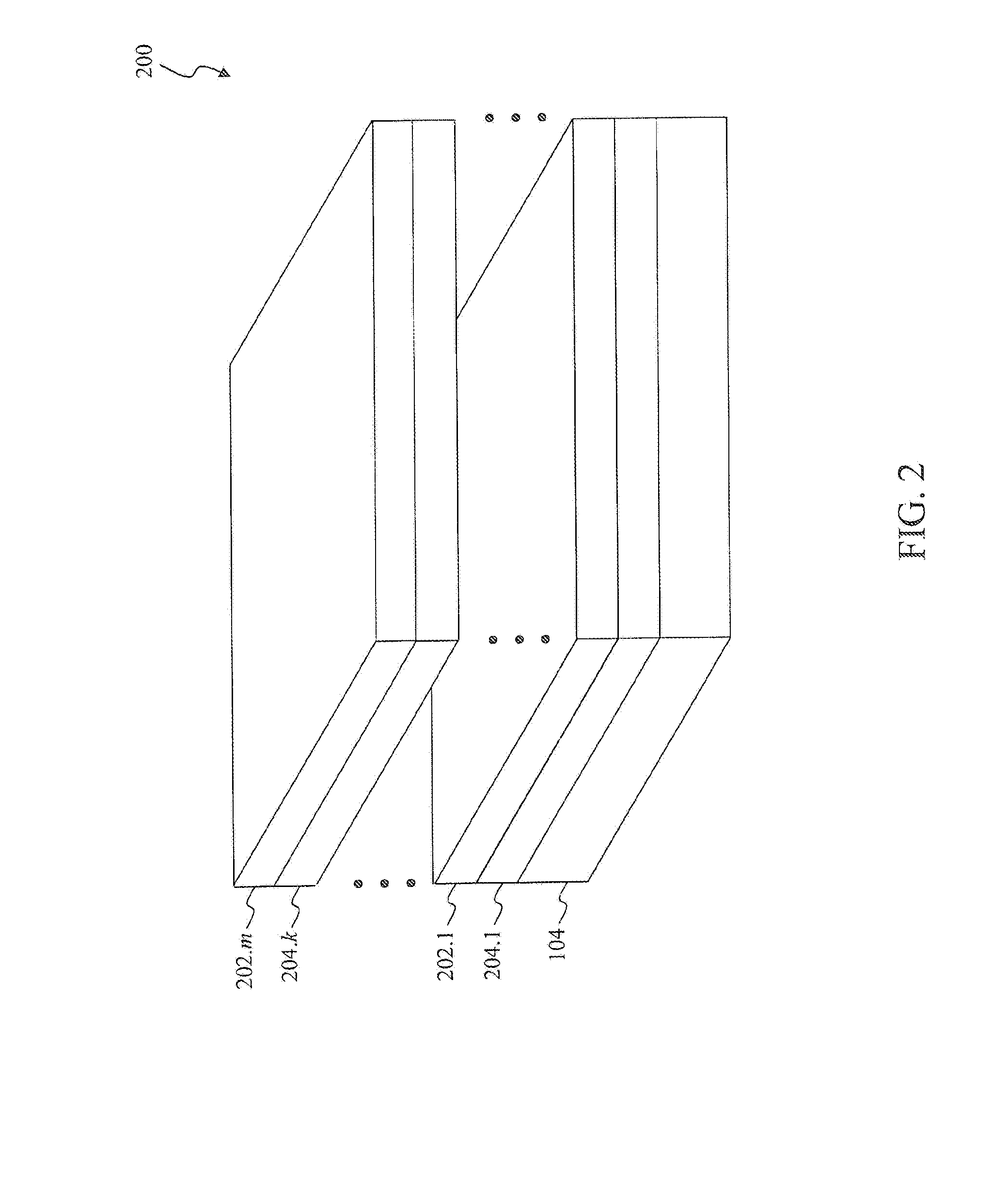

[0021]FIG. 1 illustrates a schemat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More