Computer bridge interfaces for accelerated graphics port and peripheral component interconnect devices

a technology of peripheral components and bridge interfaces, which is applied in the field of computer bridge interfaces for accelerated graphics ports and peripheral component interconnect devices, can solve the problems of increasing complexity of 3-d graphics and and achieves the effect of increasing the amount of graphics data stored in memory and increasing the speed of access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

The following patents or patent applications are hereby incorporated by reference:

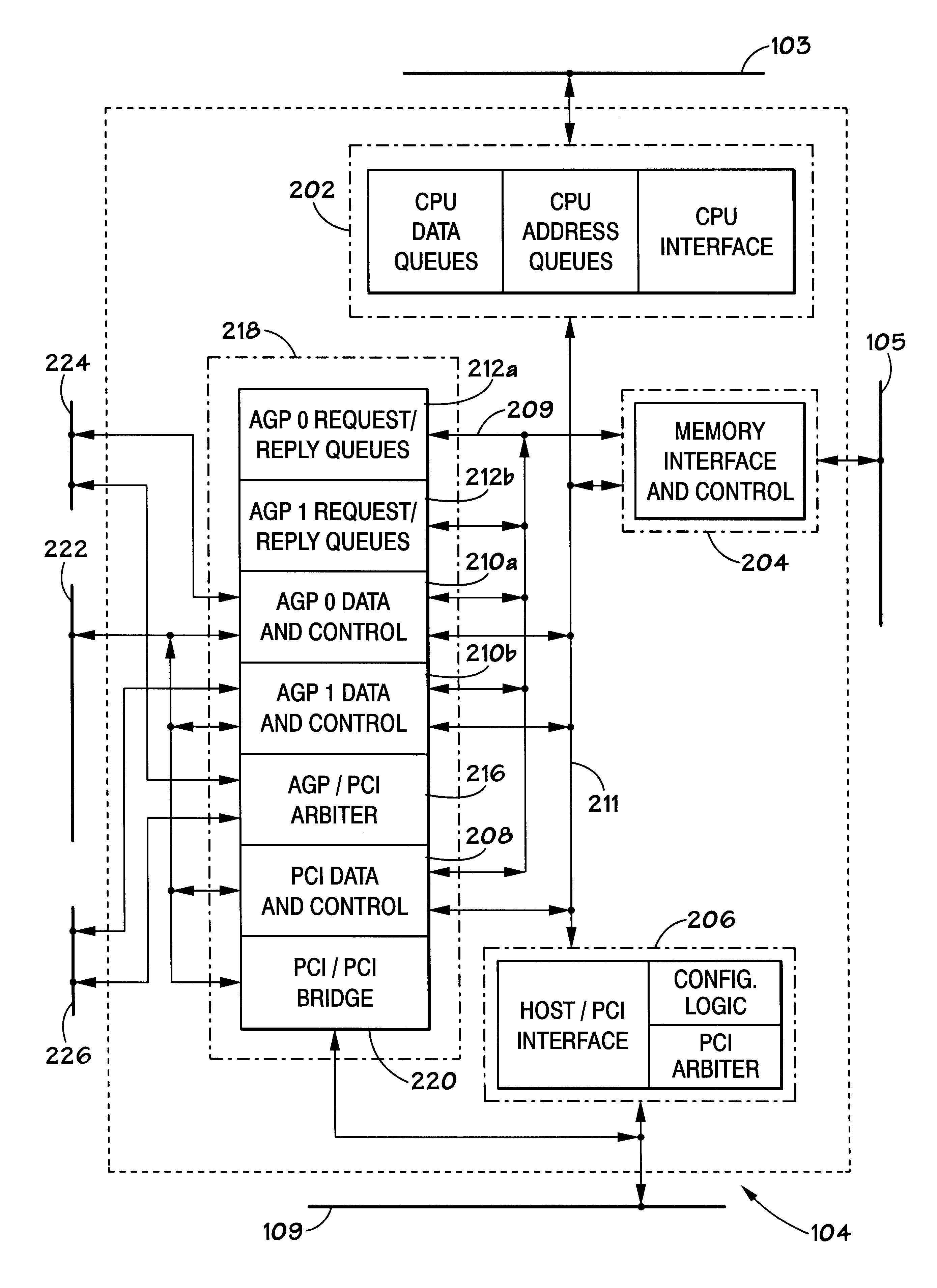

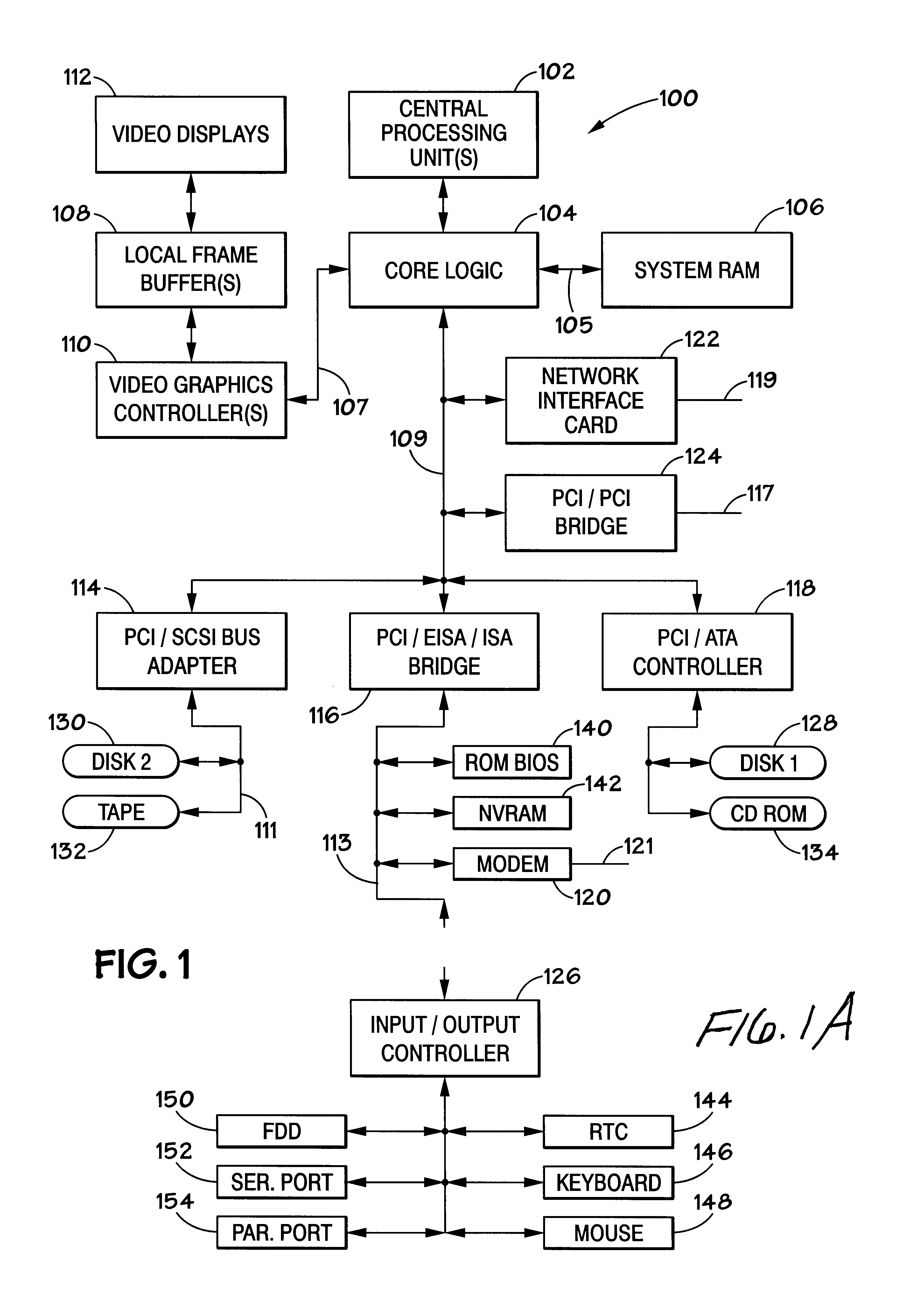

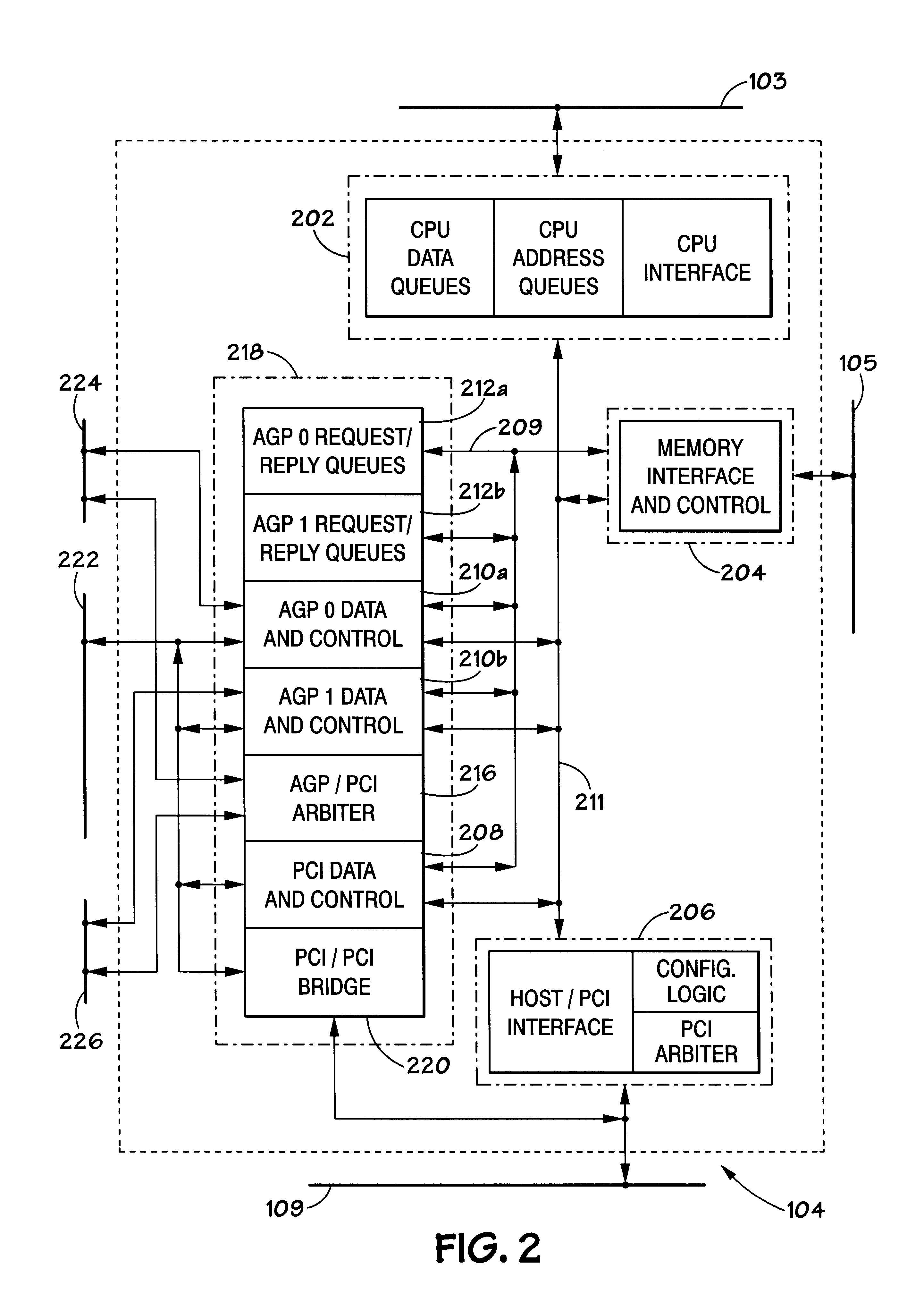

U.S. Pat. No. 5,889,970, issued on Mar. 30, 1999, entitled "Dual Purpose Apparatus, Method and System for Accelerated Graphics Port and Peripheral Component Interconnect" by Ronald T. Horan and Sompong P. Olarig.

U.S. Pat. No. 5,892,964, issued on Apr. 6, 1999, entitled "Computer Bridge Interfaces for Accelerated Graphics Port and Peripheral Component Interconnect Devices" by Ronald T. Horan, Gary W. Thome and Sompong P. Olarig.

One or more specific embodiments of the present invention will be described below. In an effort to provide a concise description of these embodiments, not all features of an actual implementation are described in the specification. It should be appreciated that in the development of any such actual implementation, as in any engineering or design project, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with syst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More