Integrated metal-insulator-metal capacitor and metal gate transistor

a metal-insulator, metal-gate transistor technology, applied in the direction of diodes, semiconductor devices, electrical apparatus, etc., can solve the problems of increasing process cost and difficult reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

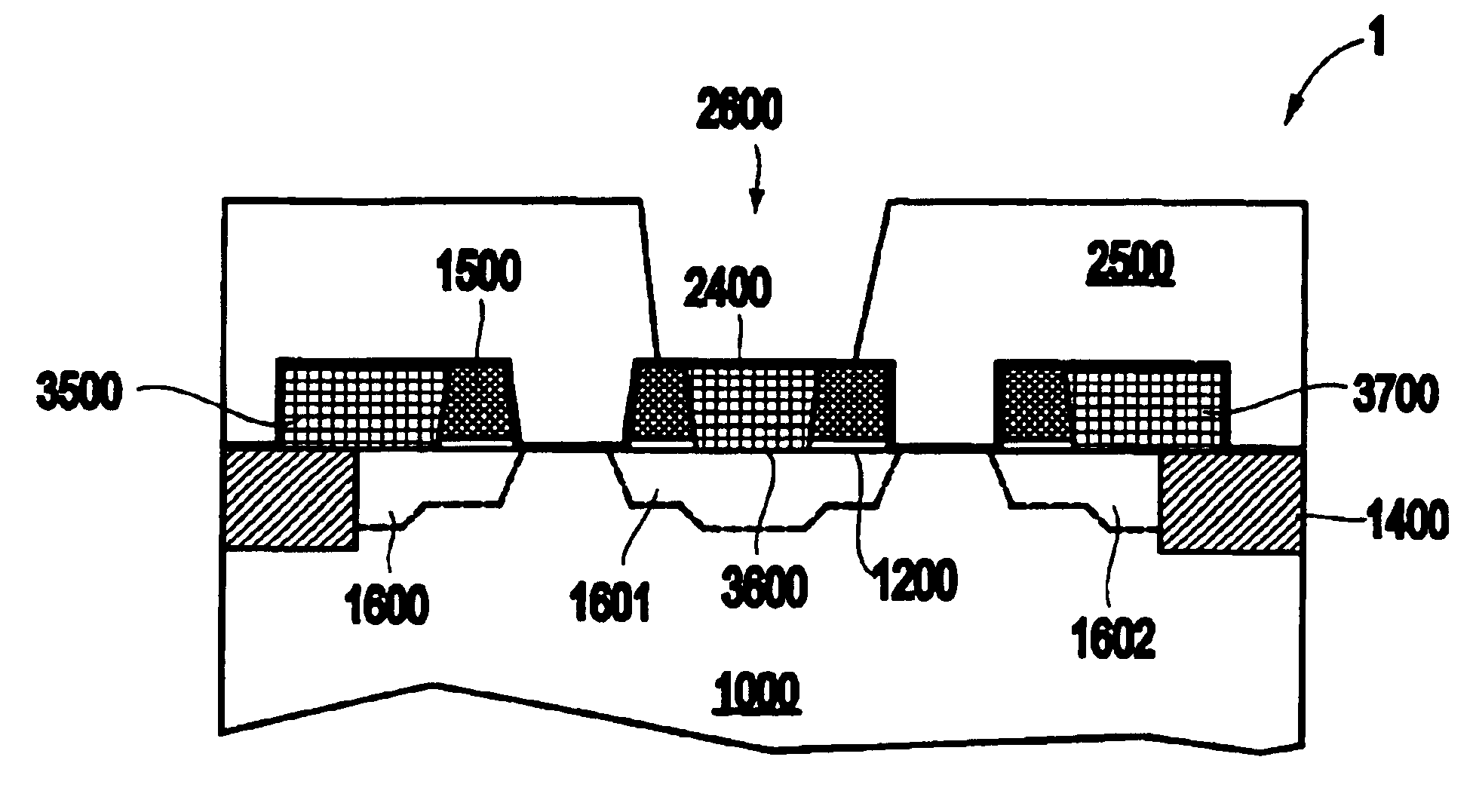

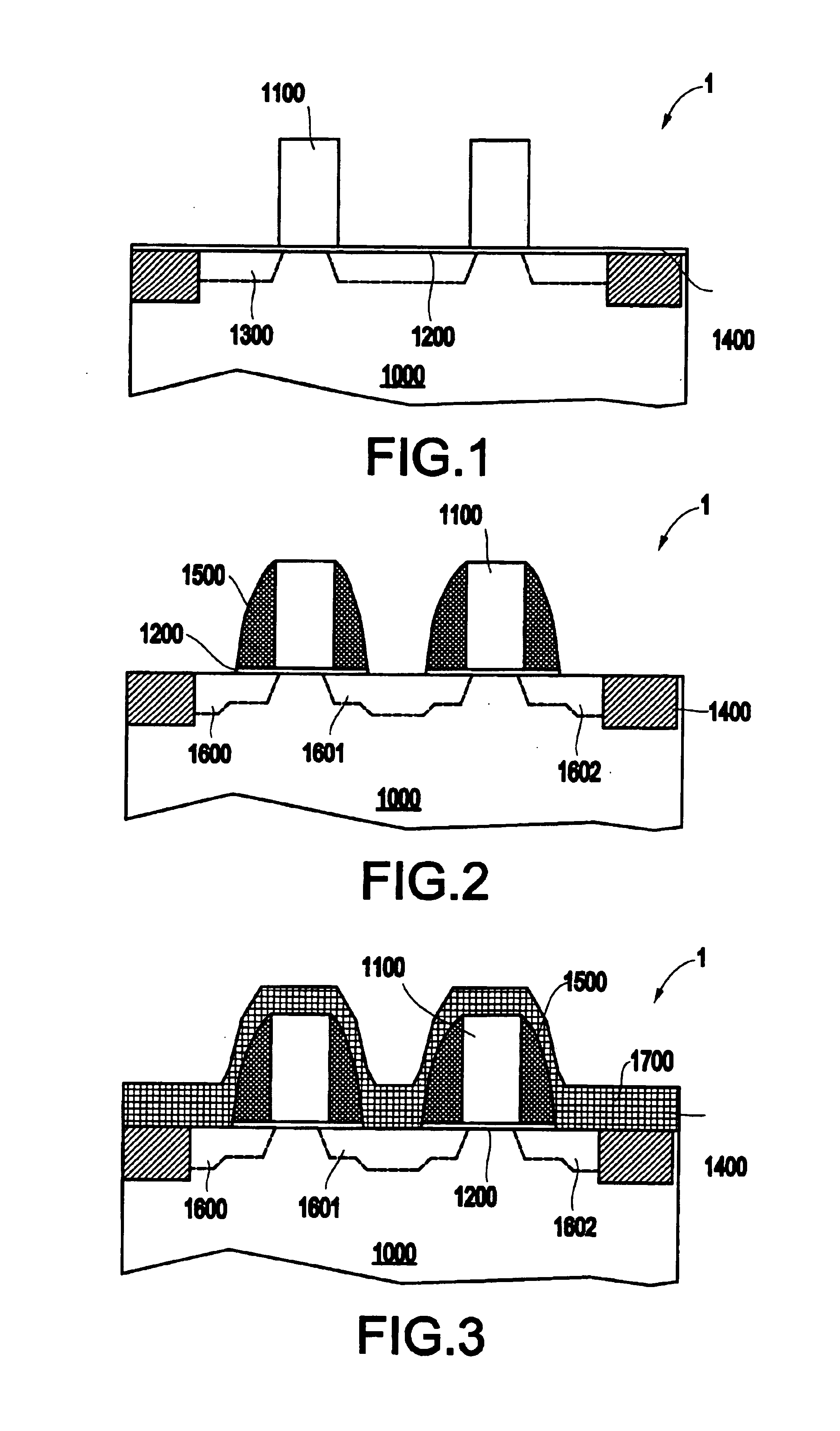

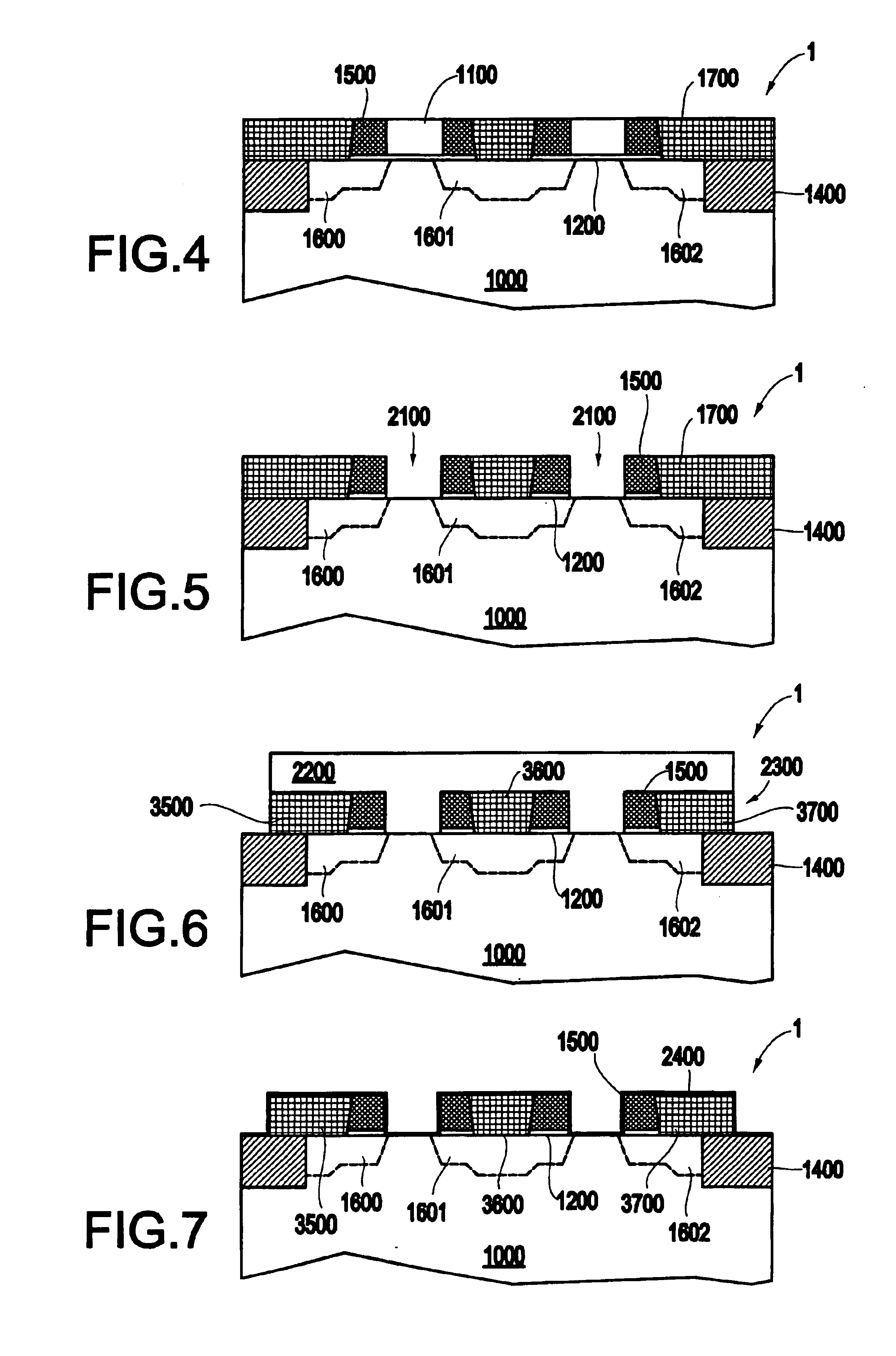

For eDRAM, not only must the performance of DRAM be improved, but the performance of the other logic circuits, such as the CPU, must also be improved for overall system performance to improve. The current trend of using a metal gate for both the DRAM and support circuits for embedded applications is well known. Using a metal capacitor (such as a MIM) for the DRAM and support circuits saves chip size, especially when a high-k dielectric material is incorporated. High-k (dielectric constant) materials such as aluminum oxide, tantalum pentoxide, titanium dioxides, barium strontium titanate, or other ferroelectric materials are compatible with metal plates. The following describes a process to form a metal gate and metal contact capacitor side-by-side in a DRAM cell configuration. However, the embodiment shown below is merely exemplary and, as would be known by one ordinarily skilled in the art, the invention is equally applicable to other structures such as support circuits where a cap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com