Patents

Literature

272 results about "Metal insulator metal capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

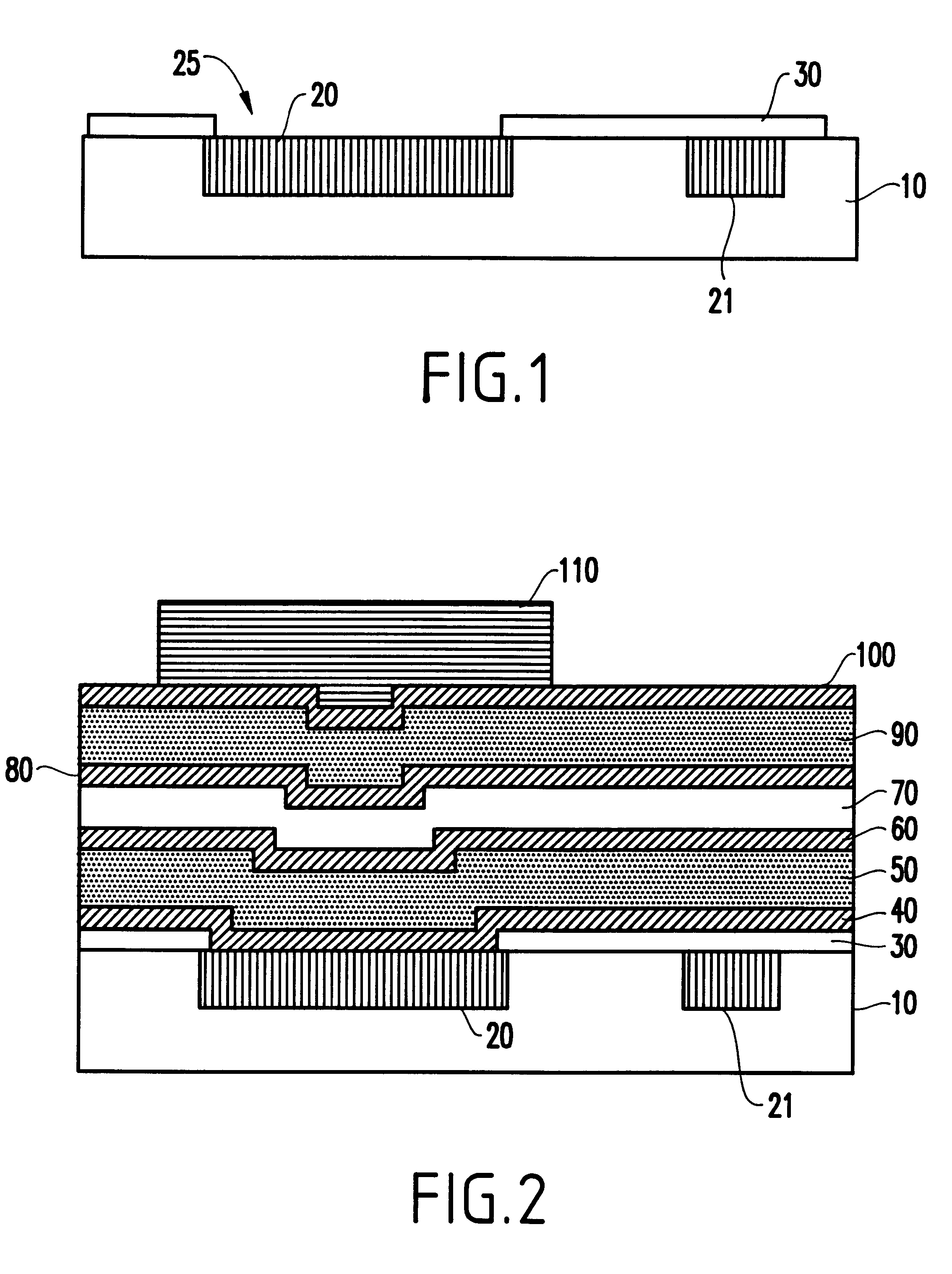

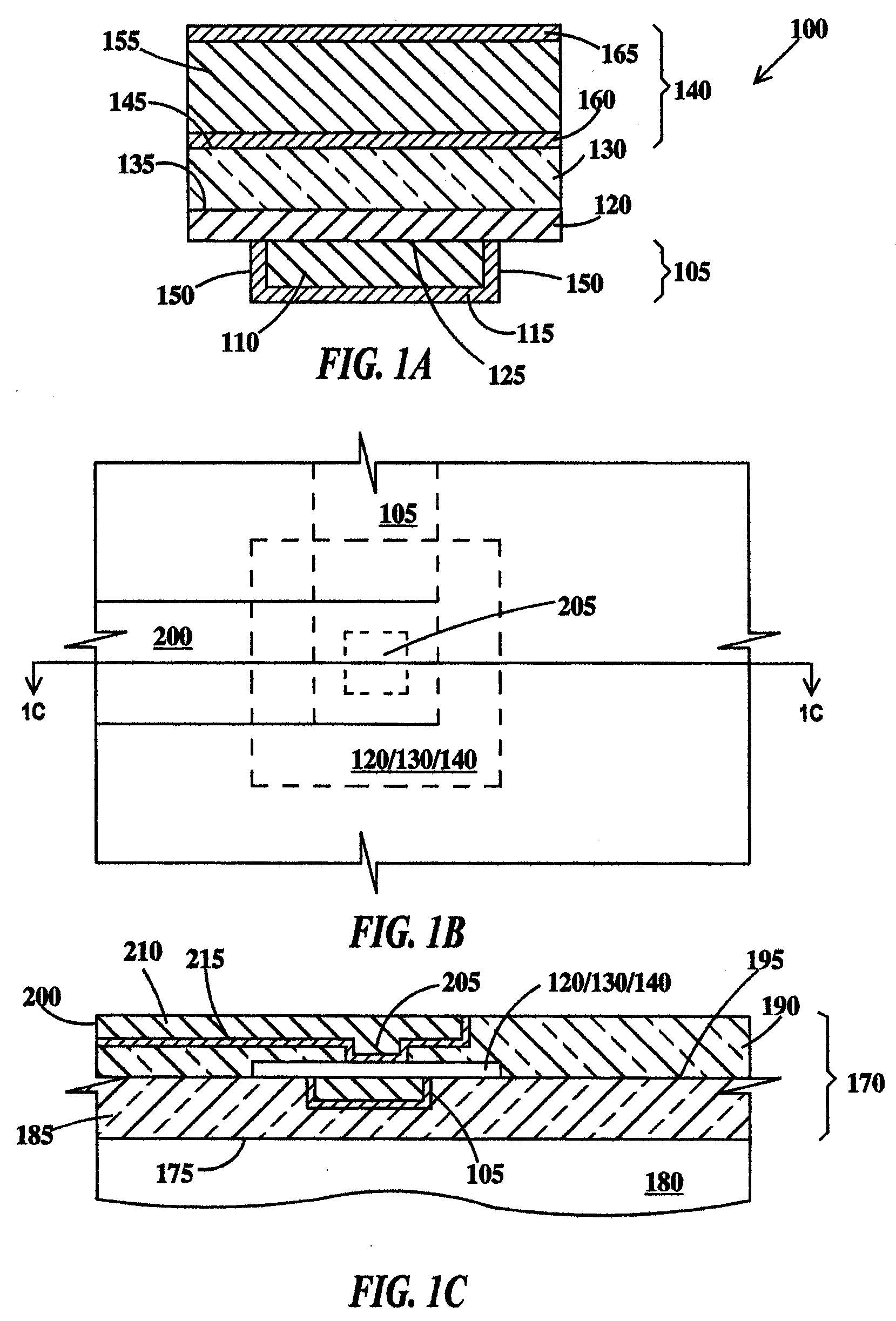

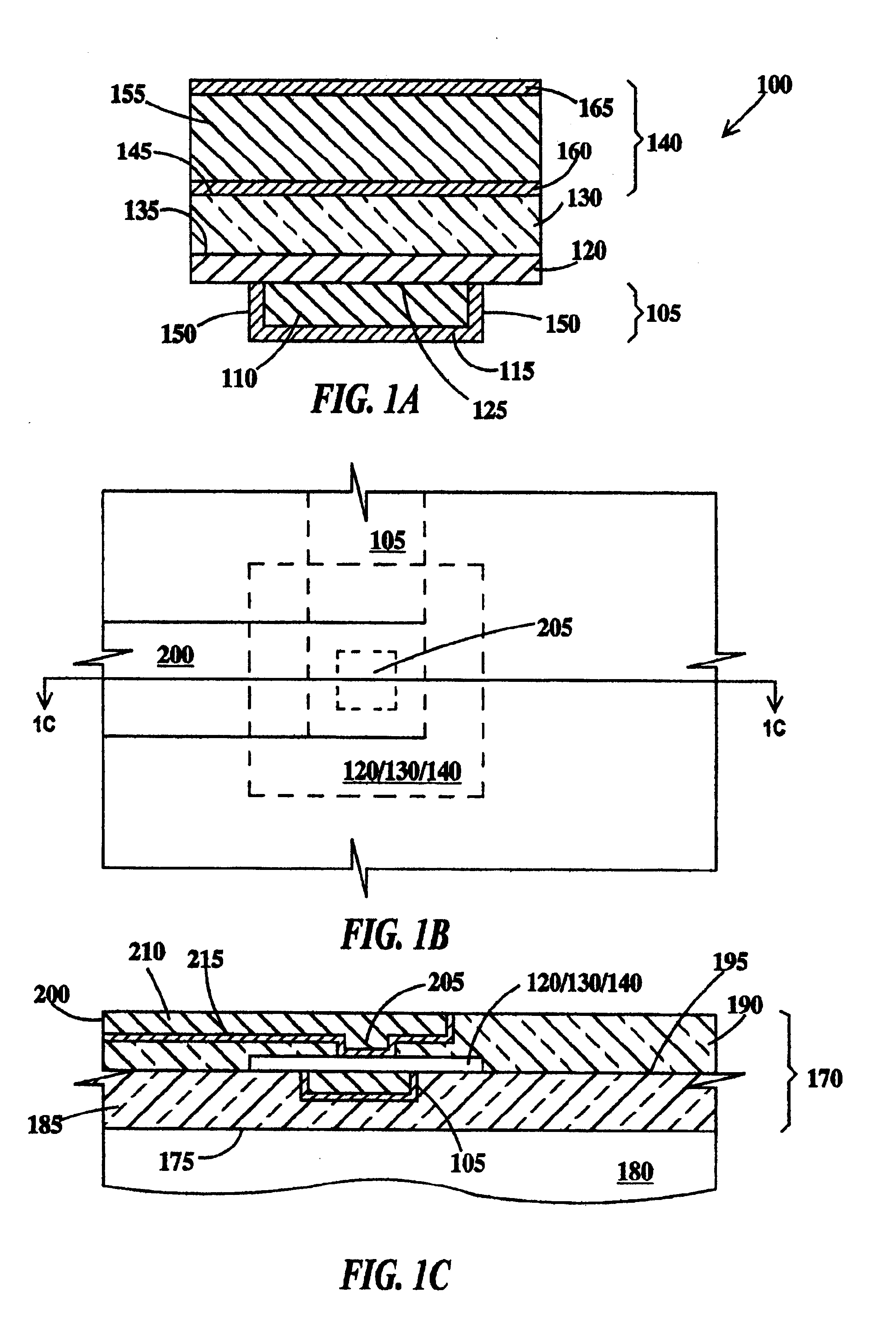

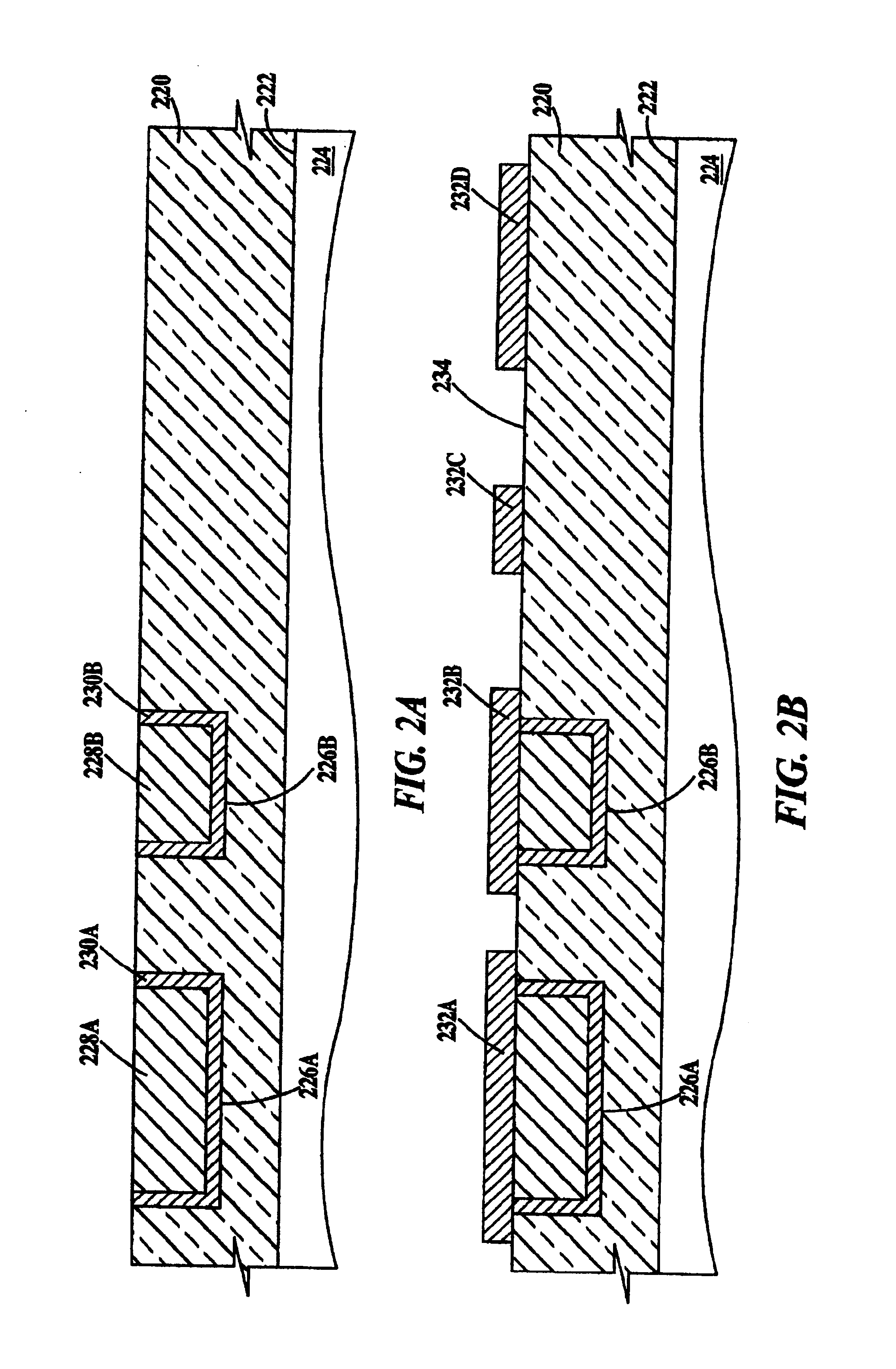

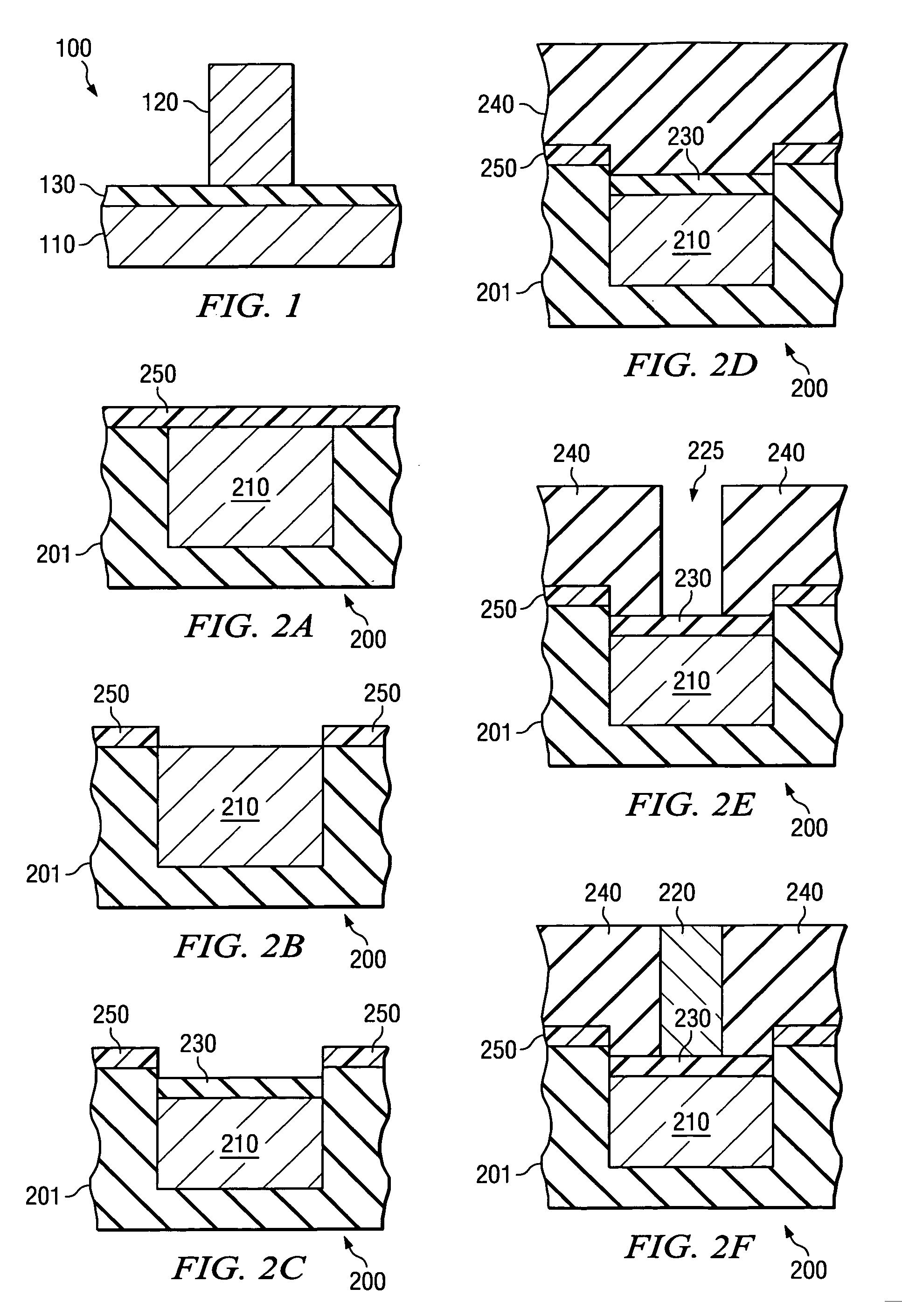

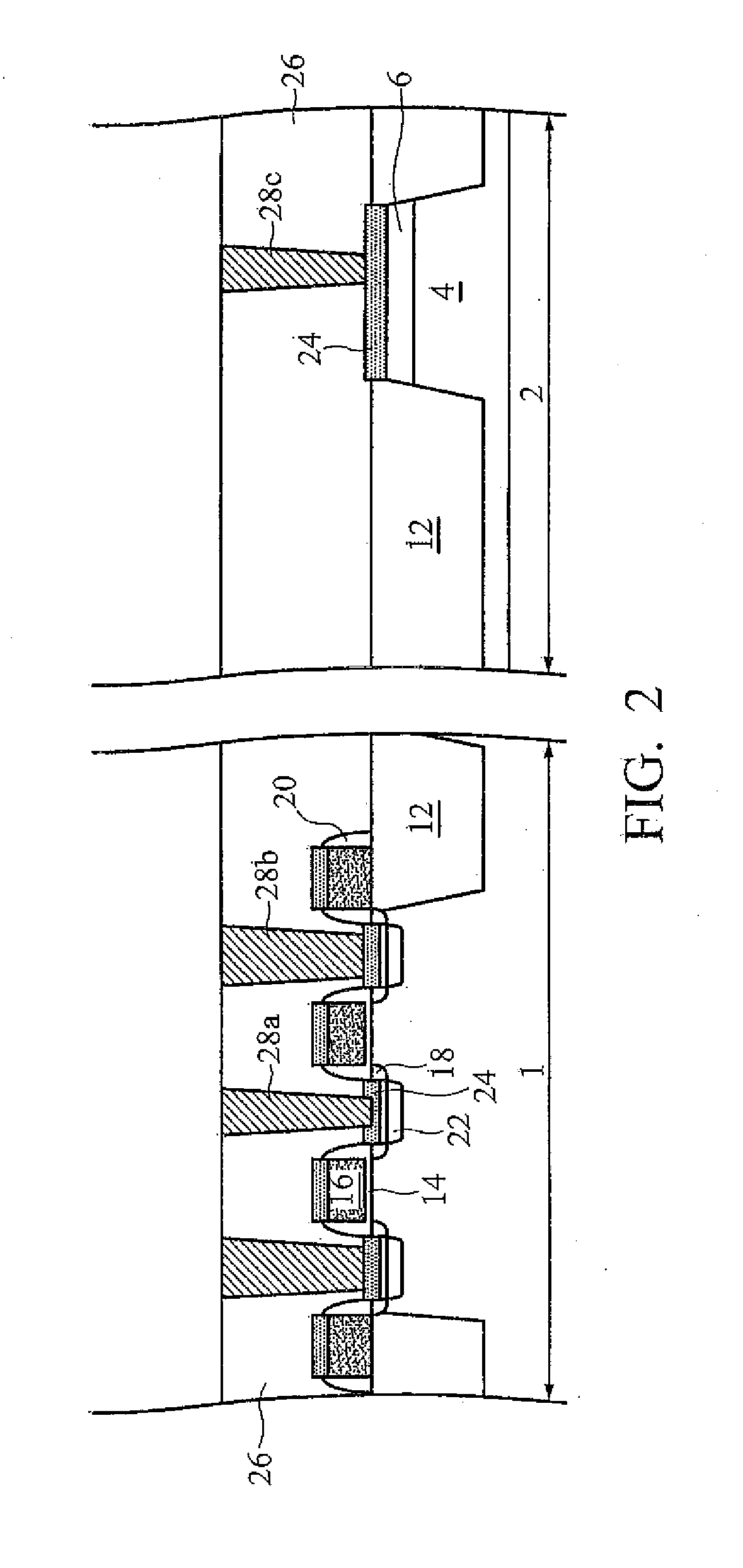

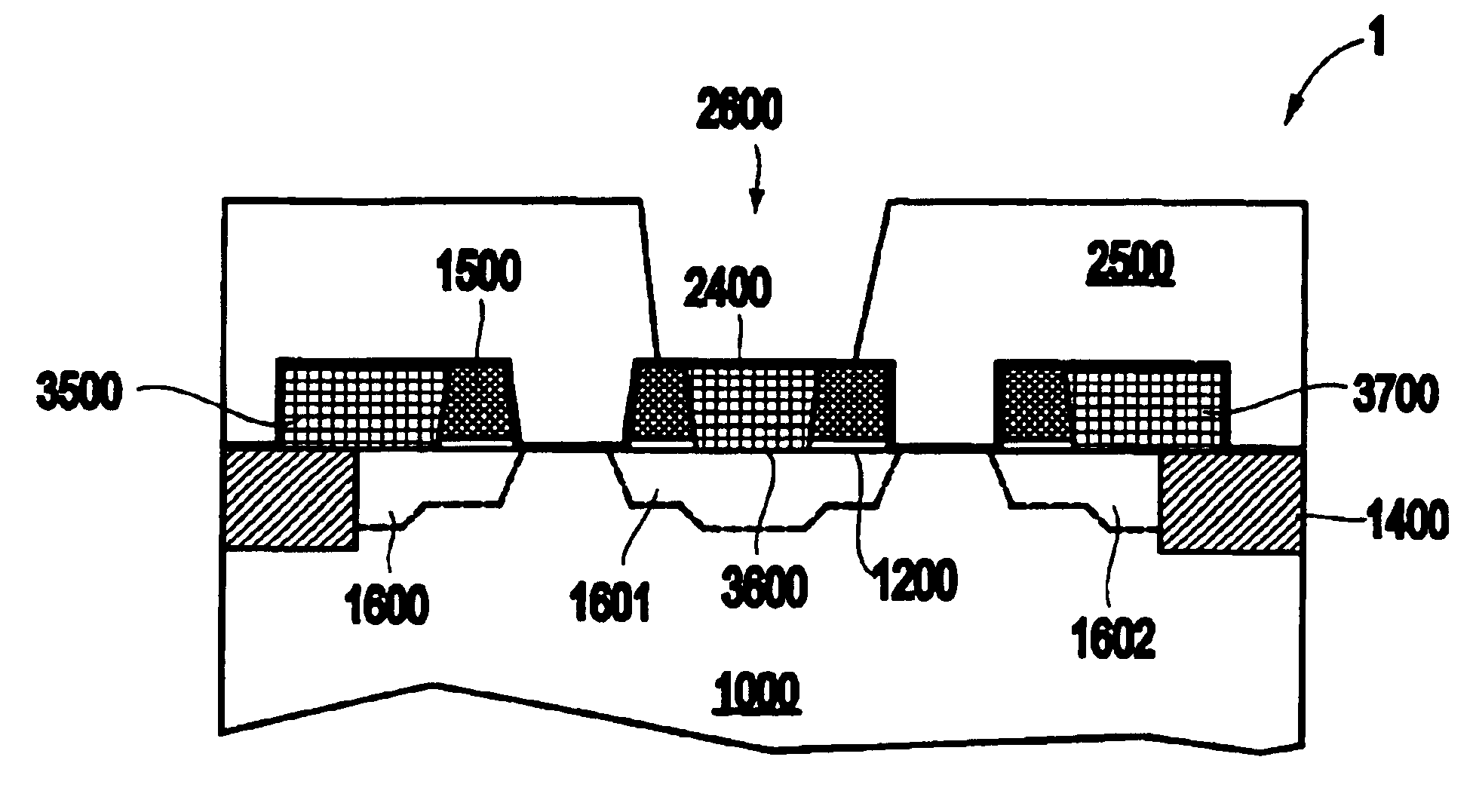

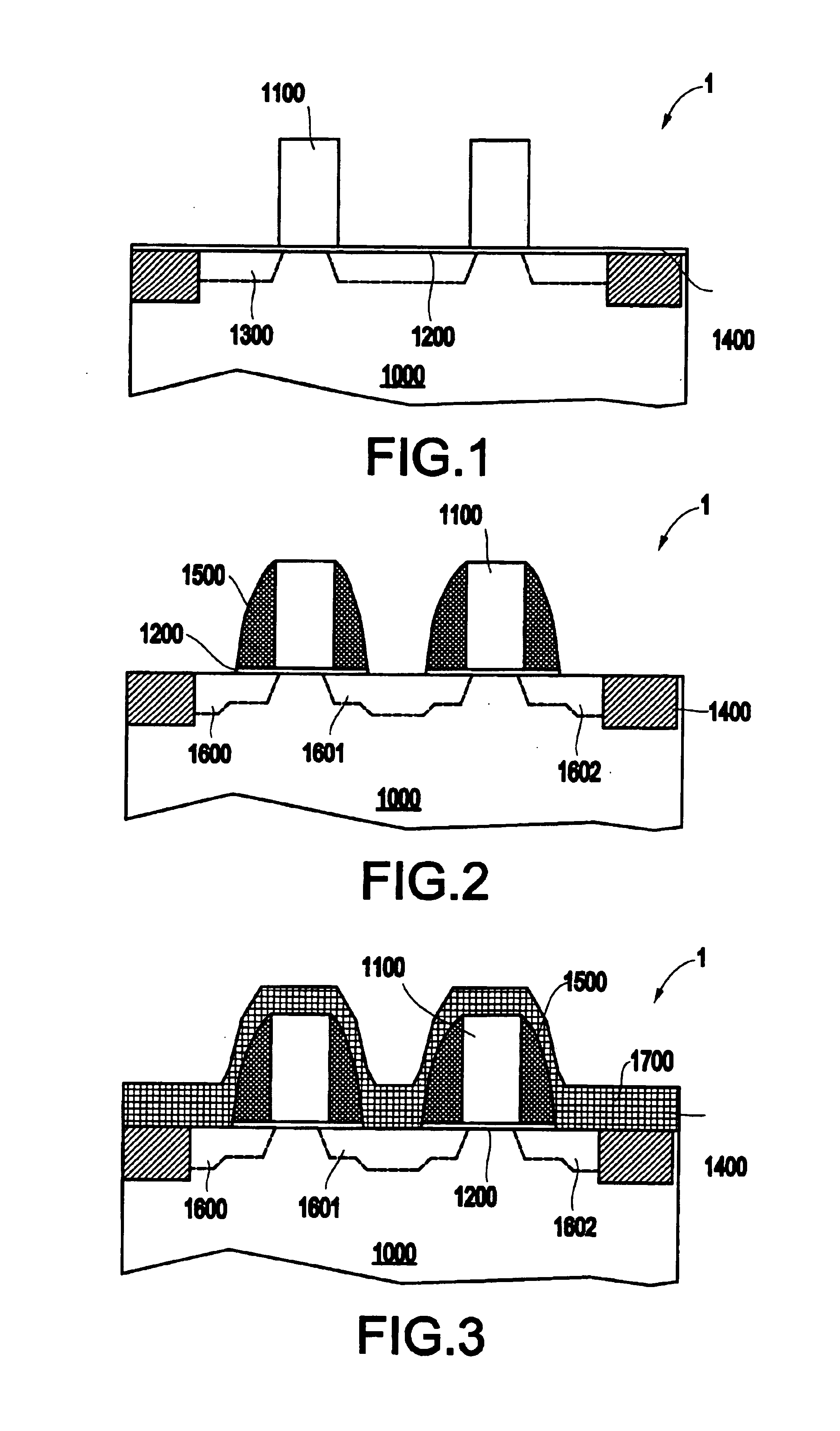

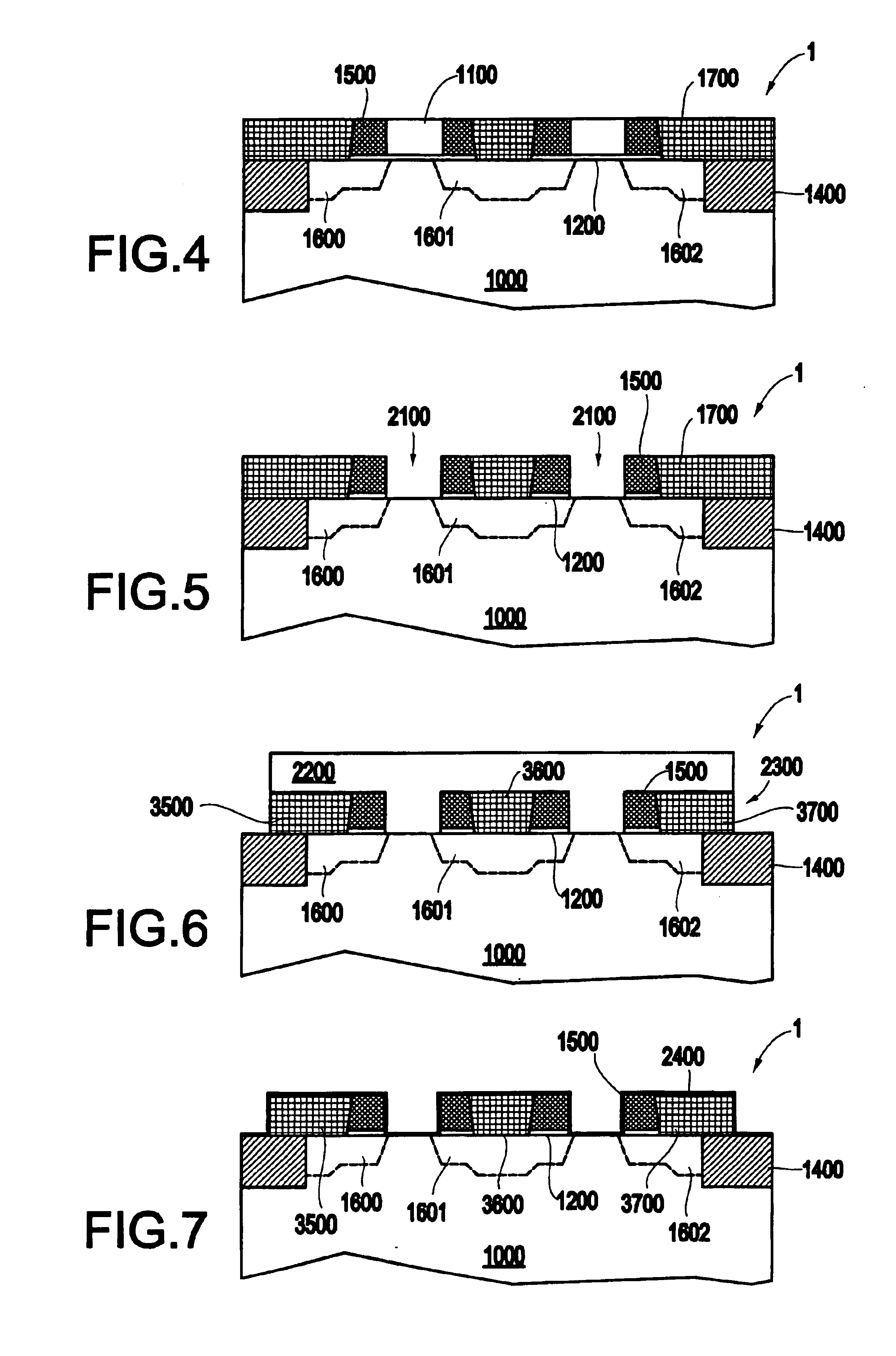

Finfet-compatible metal-insulator-metal capacitor

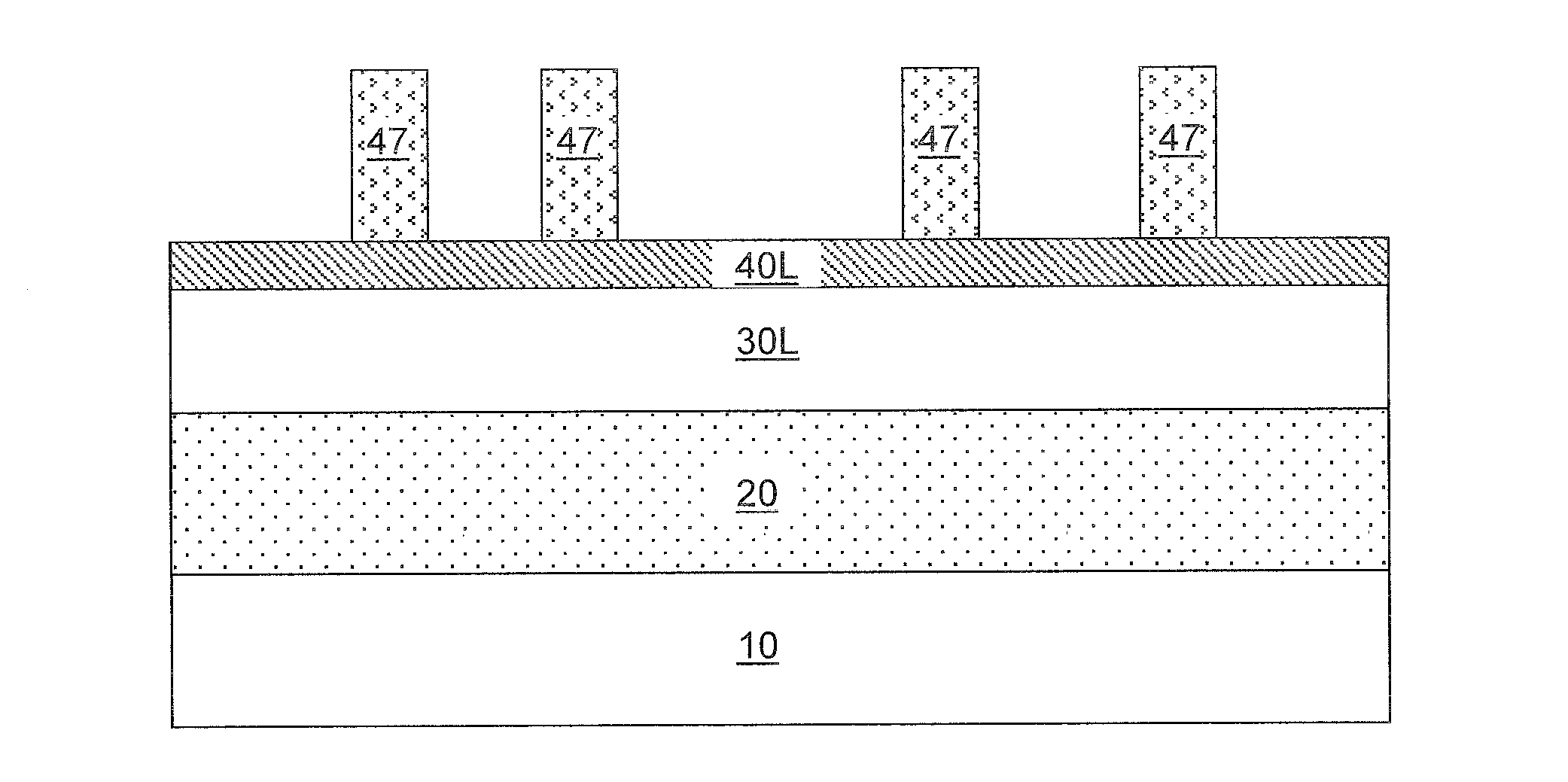

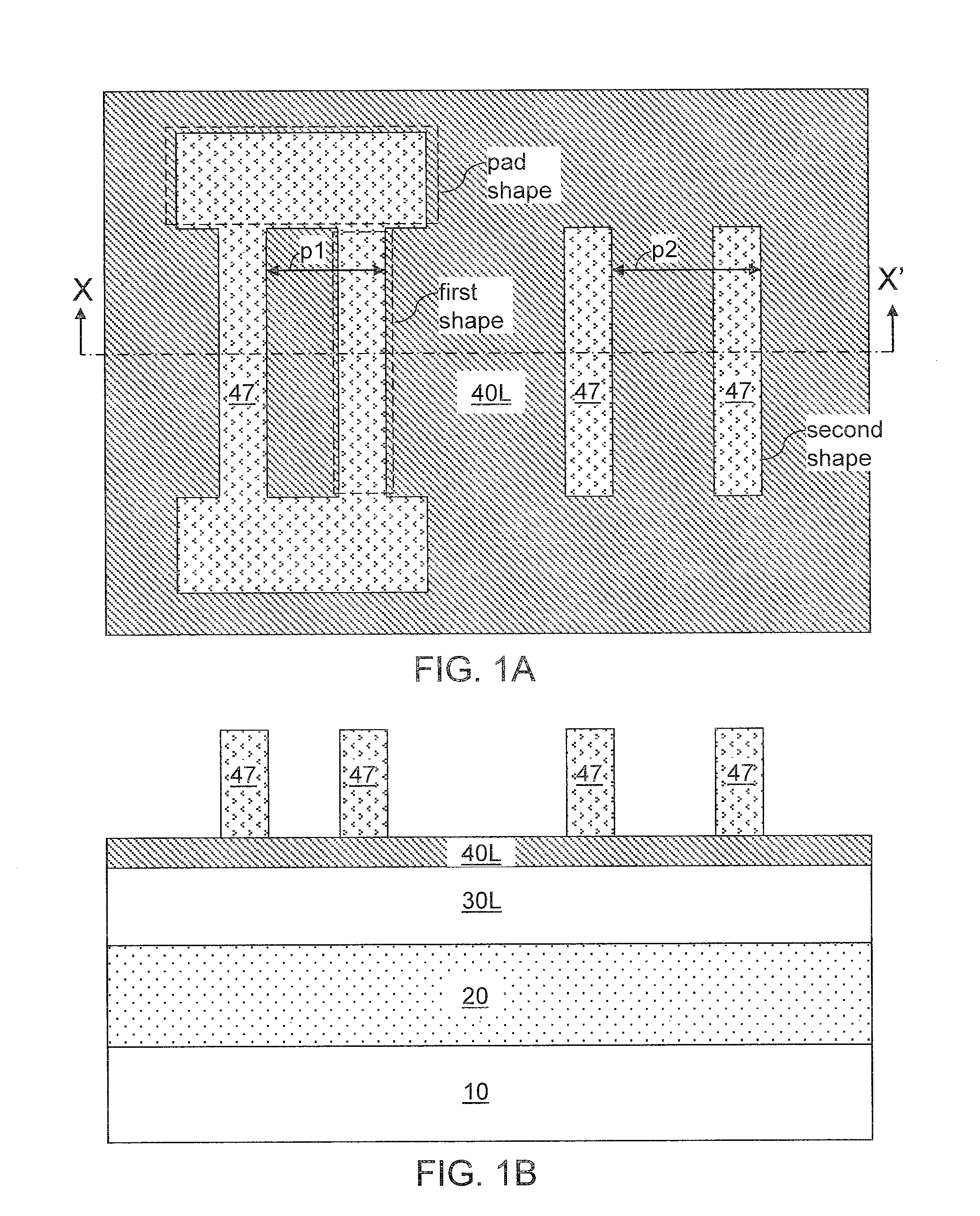

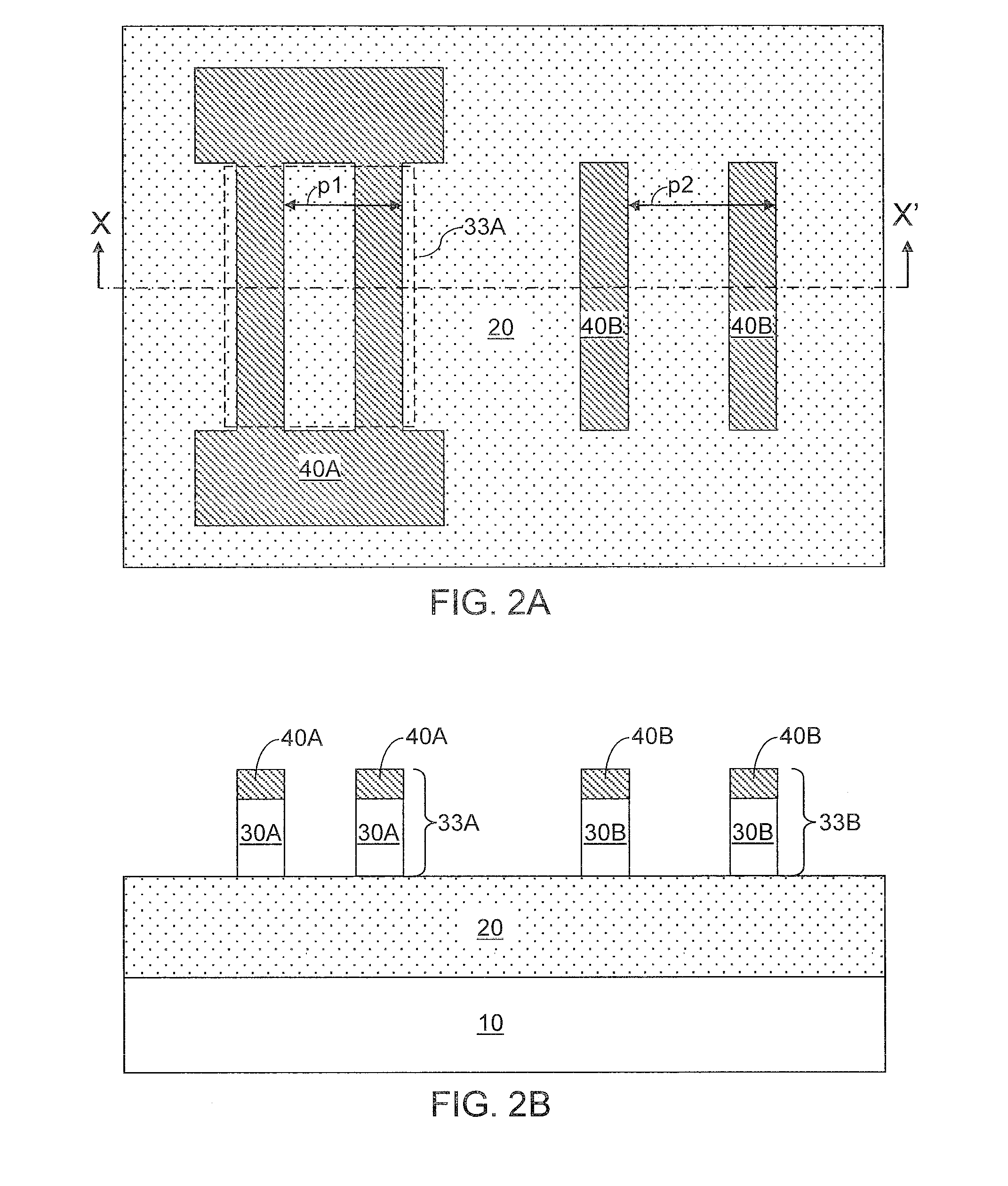

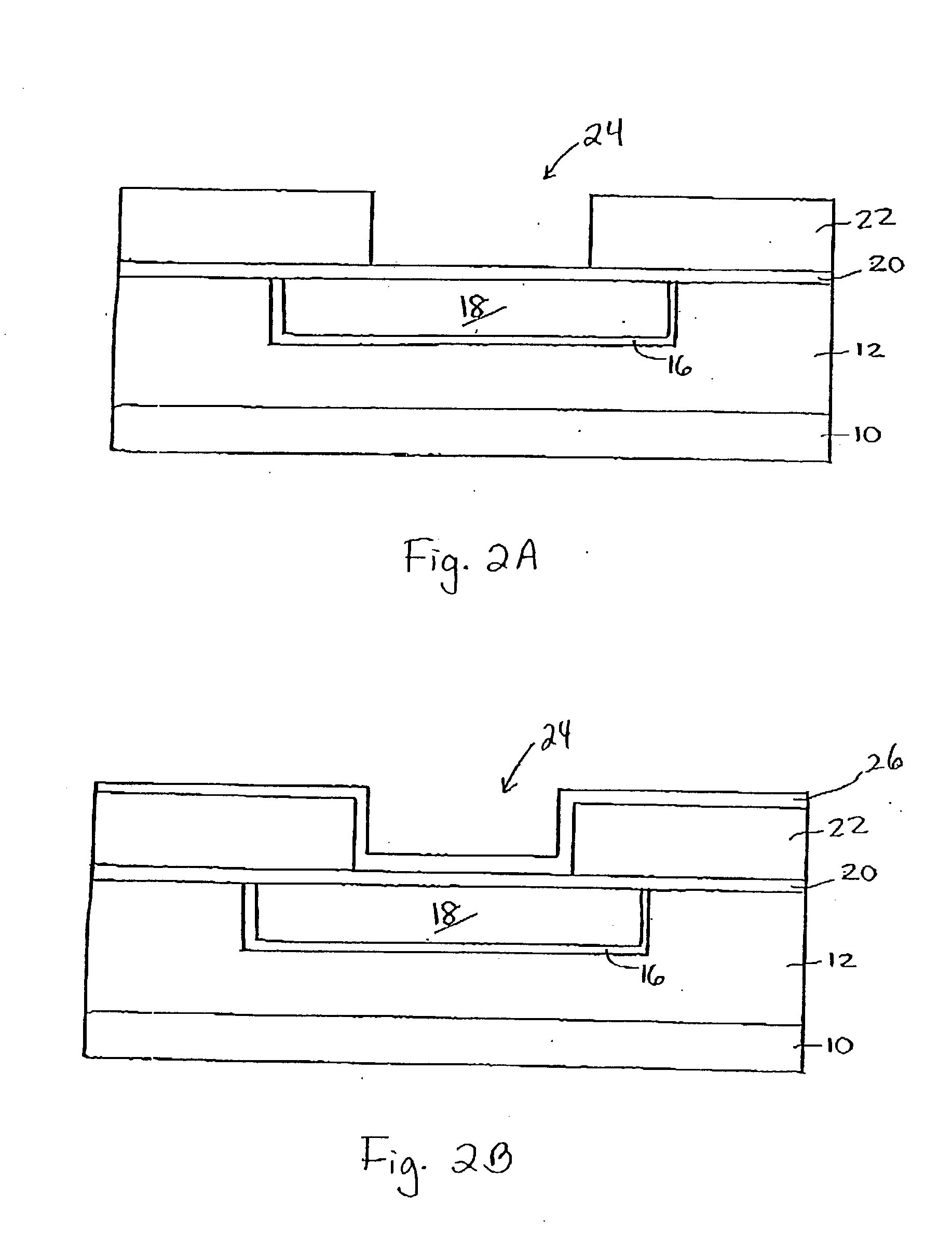

At least one semiconductor fin for a capacitor is formed concurrently with other semiconductor fins for field effect transistors. A lower conductive layer is deposited and lithographically patterned to form a lower conductive plate located on the at least one semiconductor fin. A dielectric layer and at least one upper conductive layer are formed and lithographically patterned to form a node dielectric and an upper conductive plate over the lower conductive plate as well as a gate dielectric and a gate conductor over the other semiconductor fins. The lower conductive plate, the node dielectric, and the upper conductive plate collectively form a capacitor. The finFETs may be dual gate finFETs or trigate finFETs. A buried insulator layer may be optionally recessed to increase the capacitance. Alternately, the lower conductive plate may be formed on a planar surface of the buried insulator layer.

Owner:GLOBALFOUNDRIES US INC

Metal-insulator-metal capacitor for copper damascene process and method of forming the same

A capacitor structure formed on a semiconductor substrate may include a first interconnect wiring (such as copper damascene) and a first conductive barrier layer in contact with the first interconnect wiring. A first capacitor plate, a capacitor dielectric structure and a second capacitor plate may also be included over the first conductive barrier layer. A second conductive barrier layer may be formed on the second capacitor plate and a second planar insulating structure may be formed over the second capacitor plate. Finally, a second interconnect wiring may be embedded within a second planar insulator structure.

Owner:IBM CORP

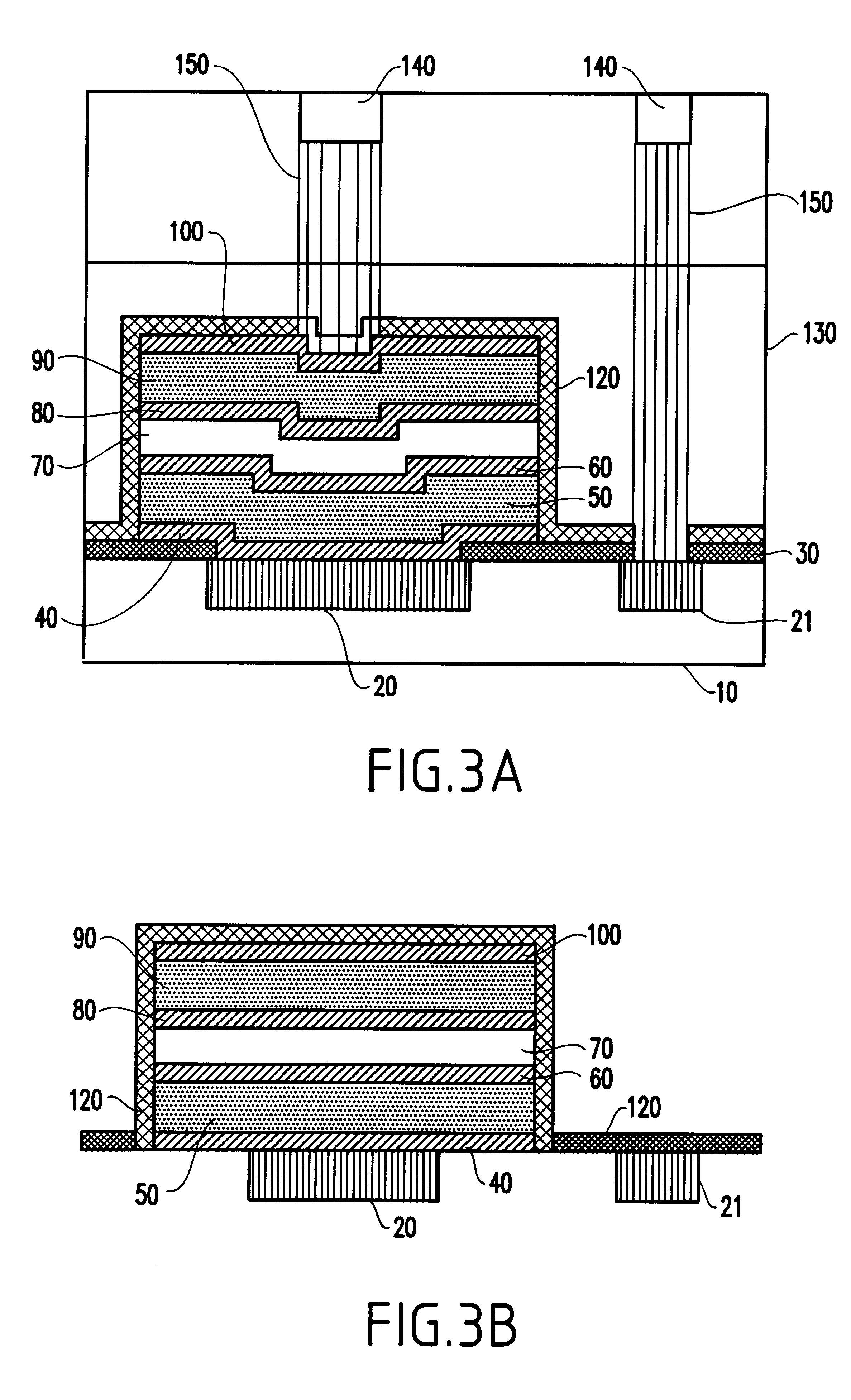

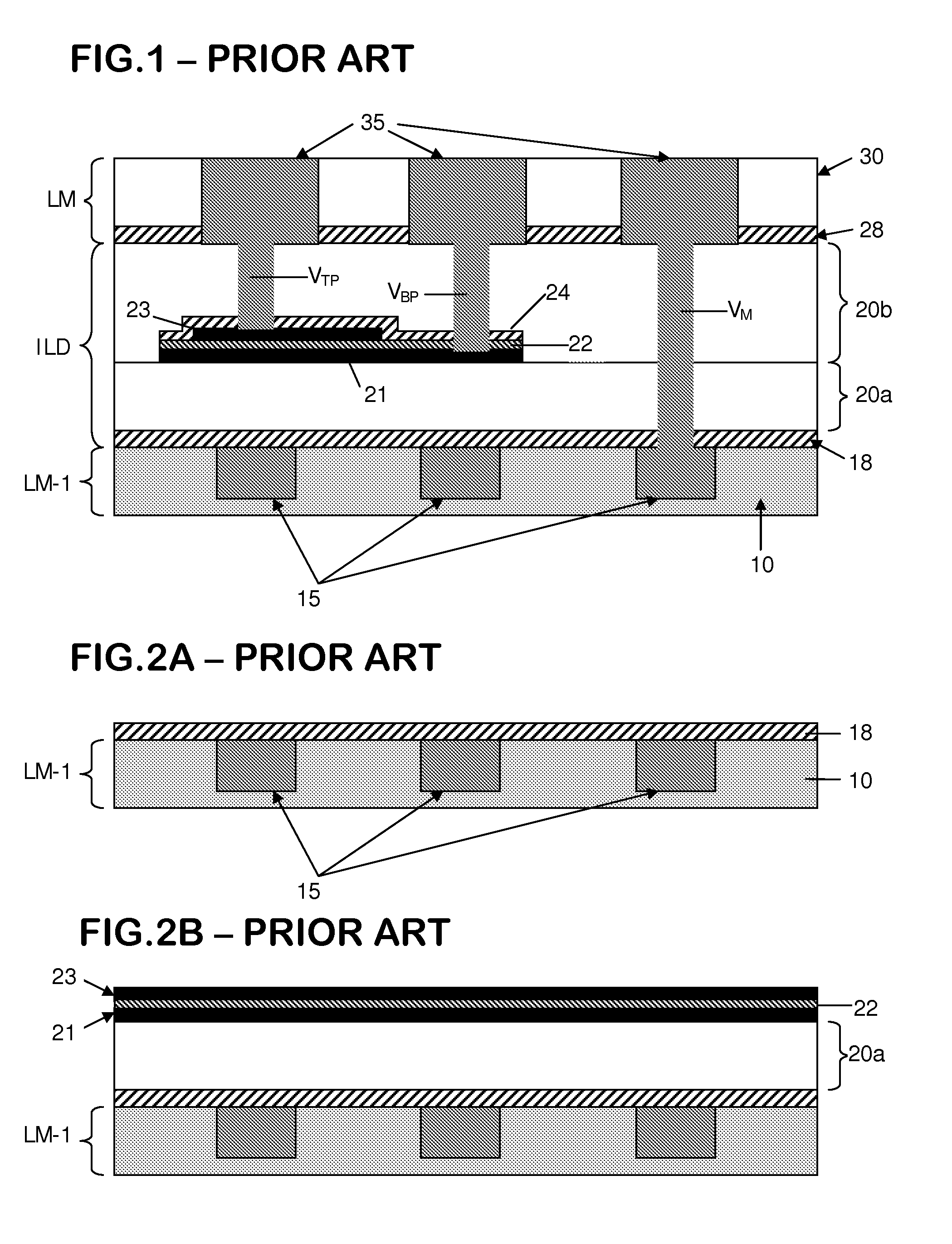

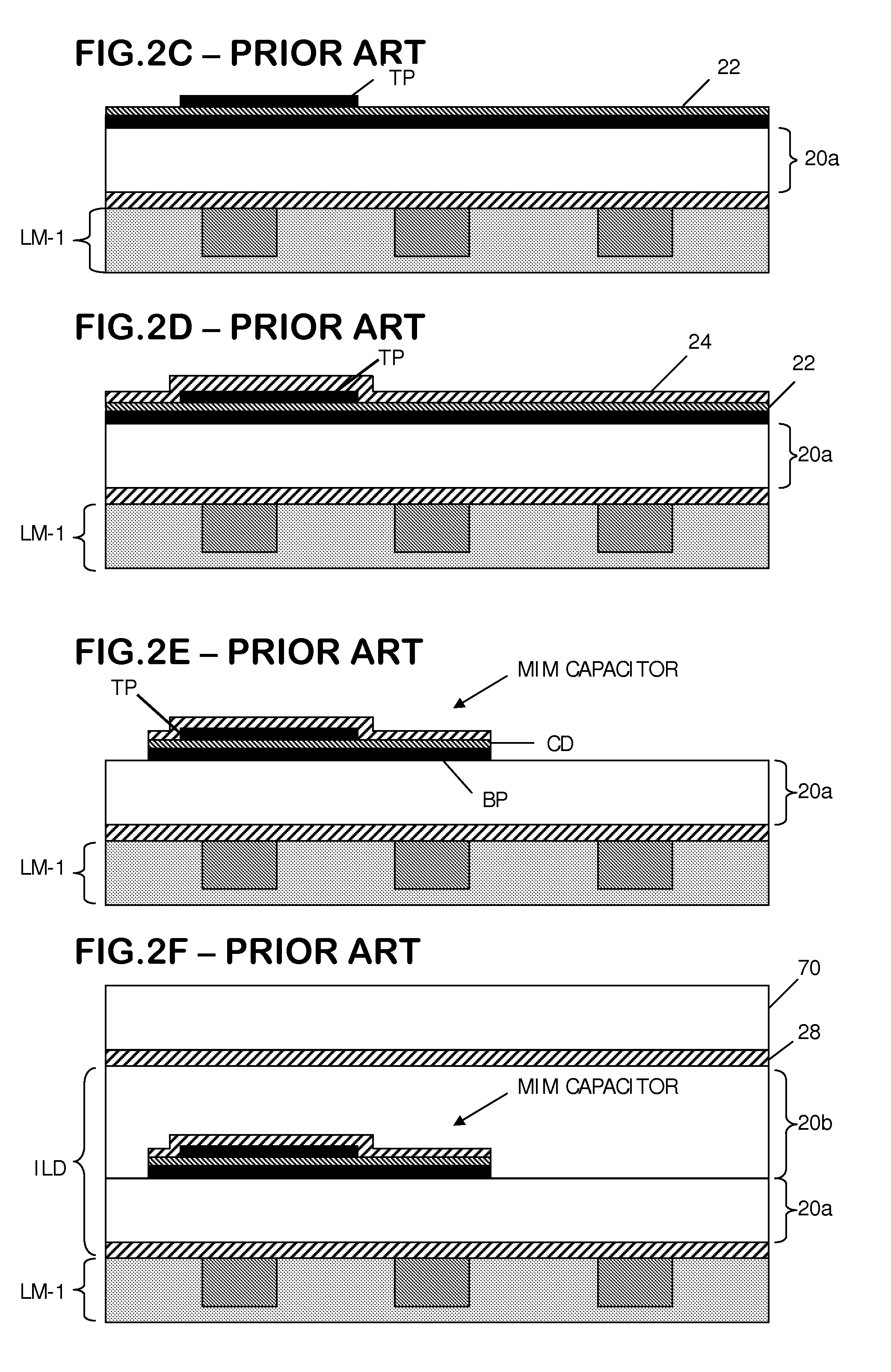

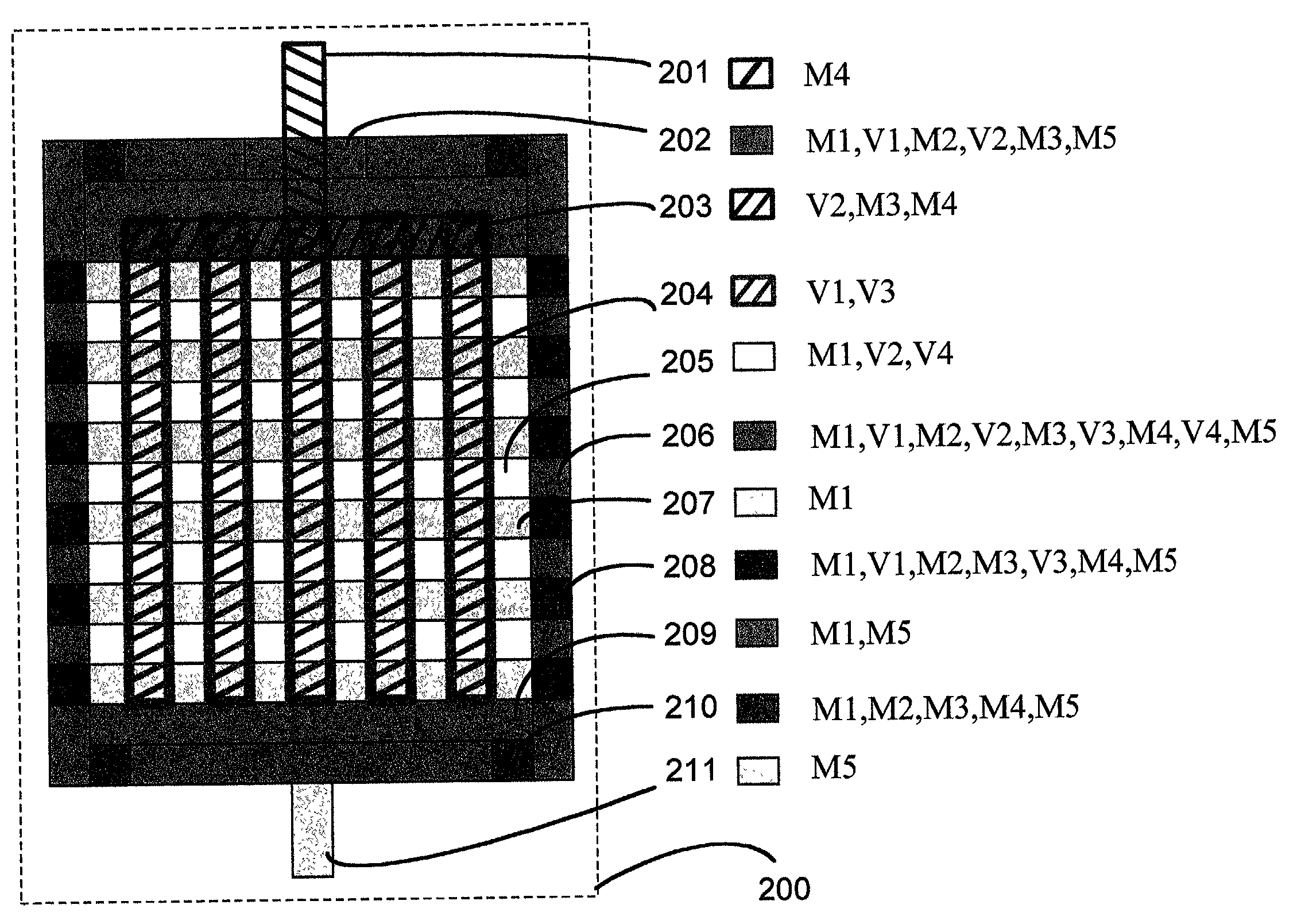

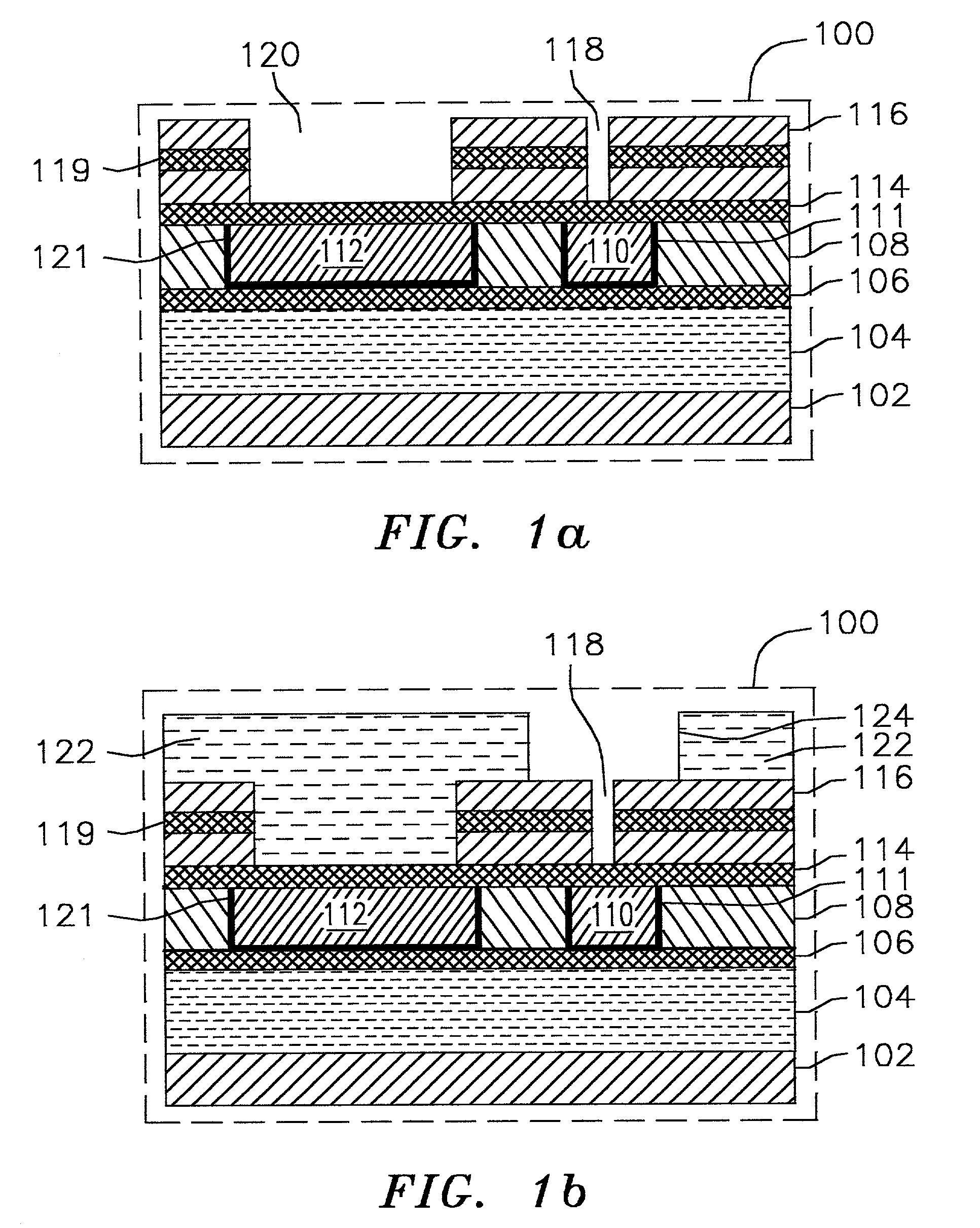

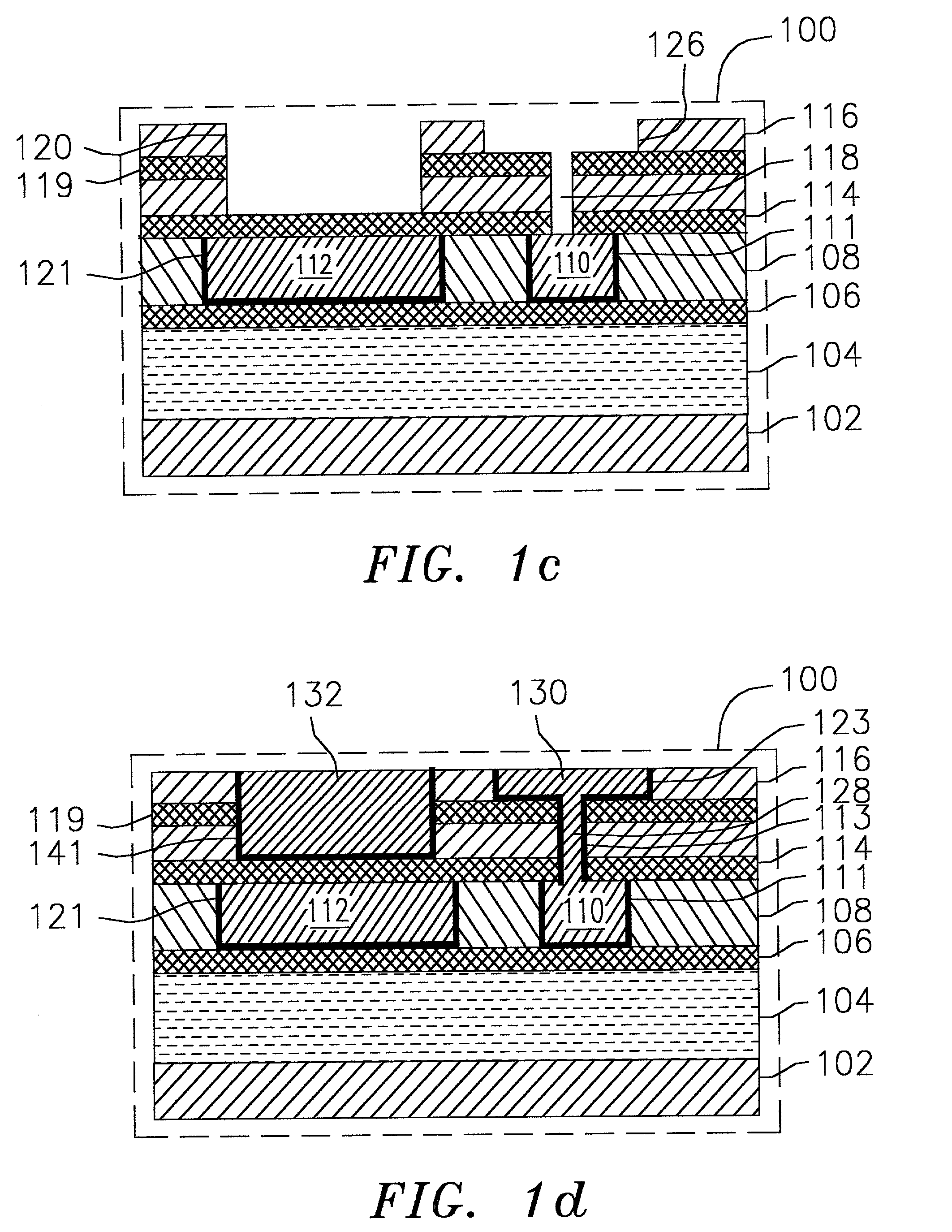

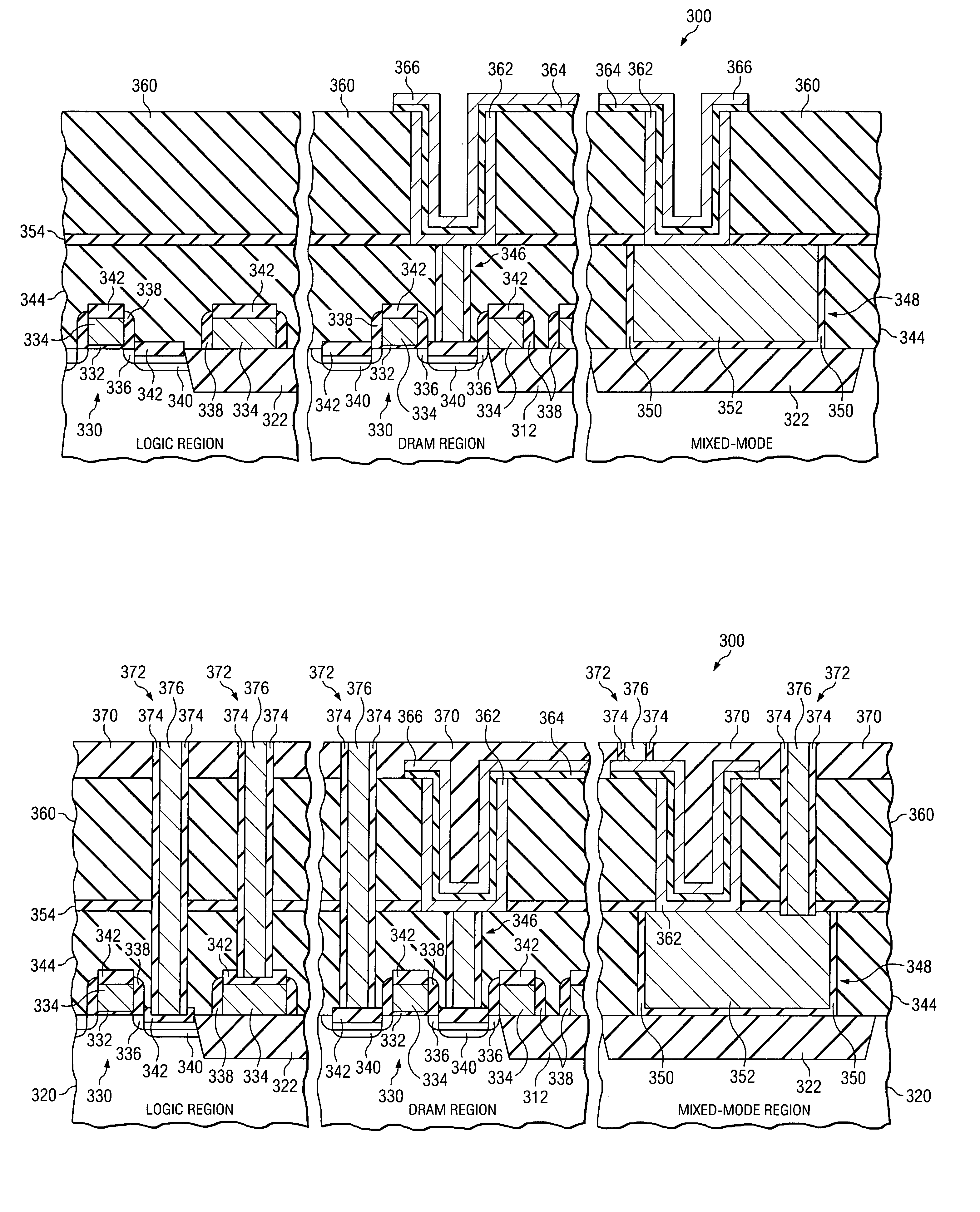

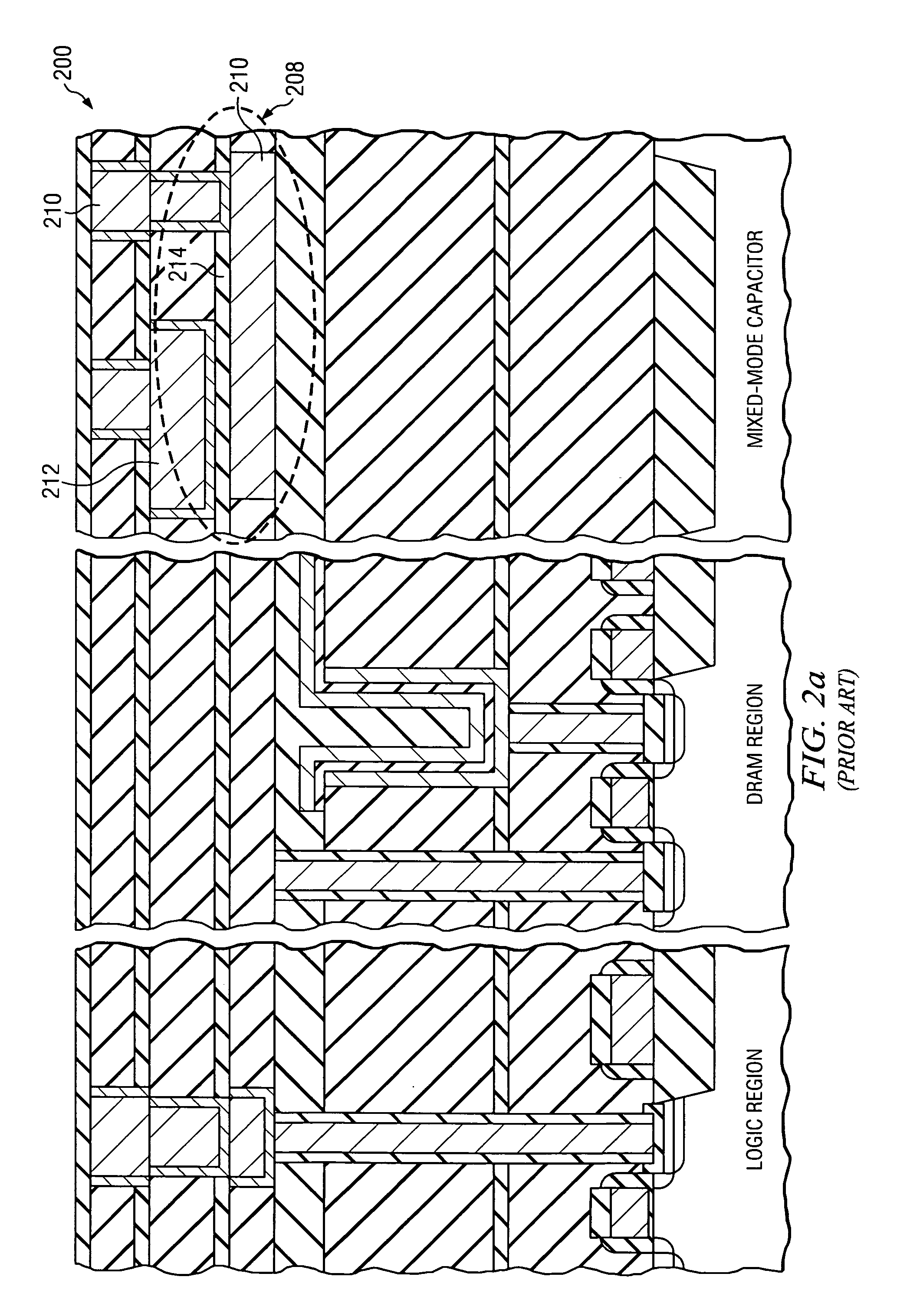

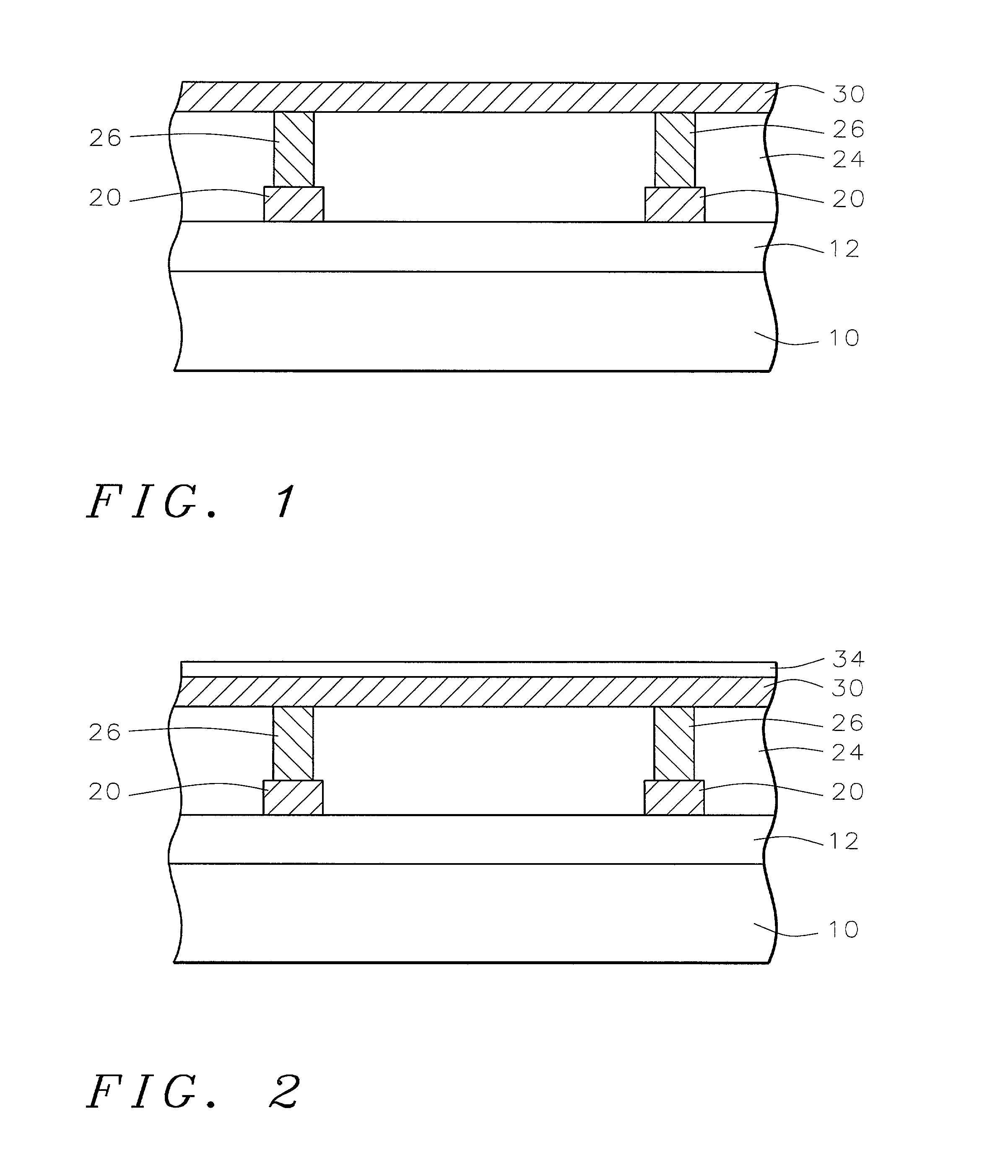

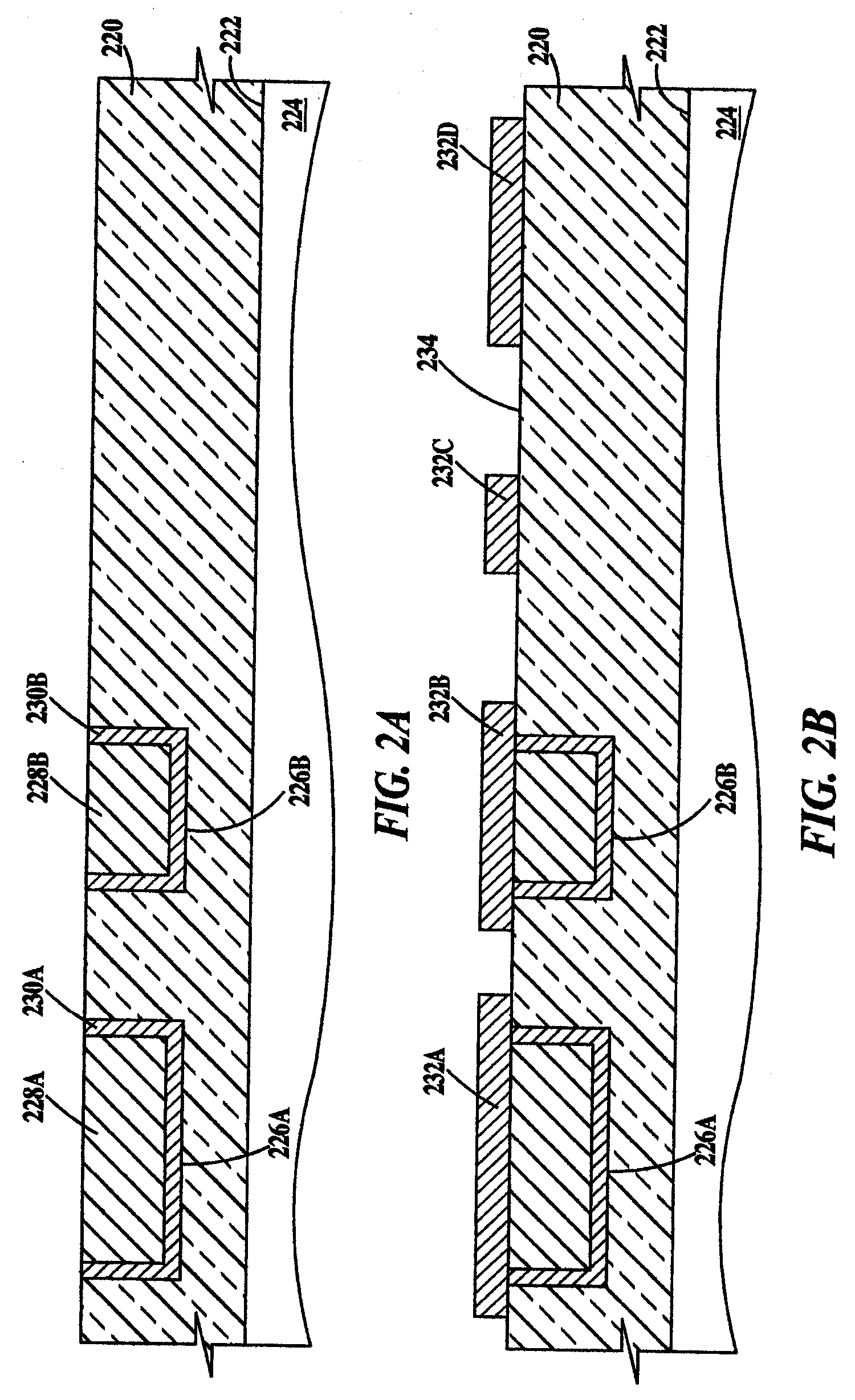

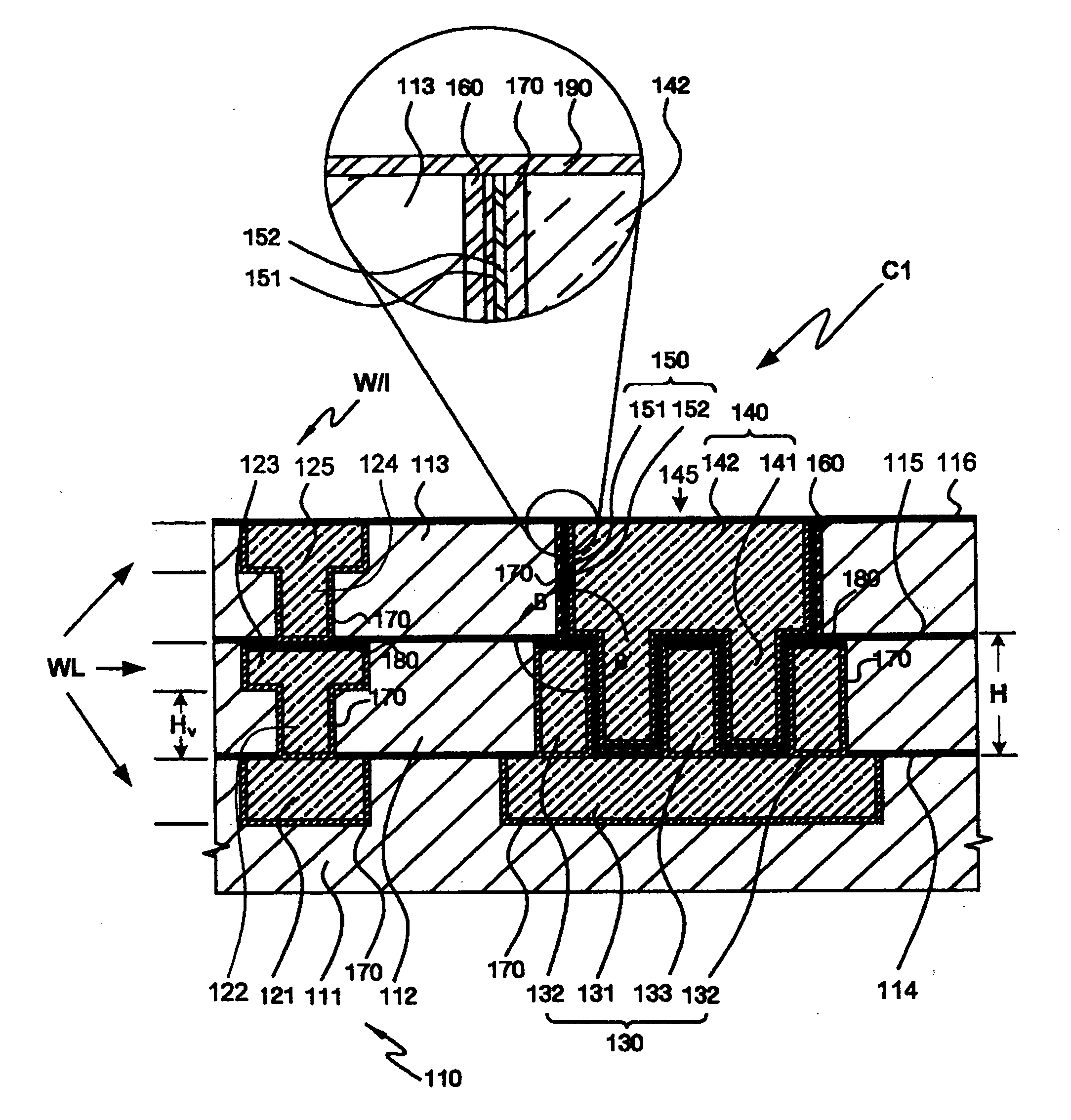

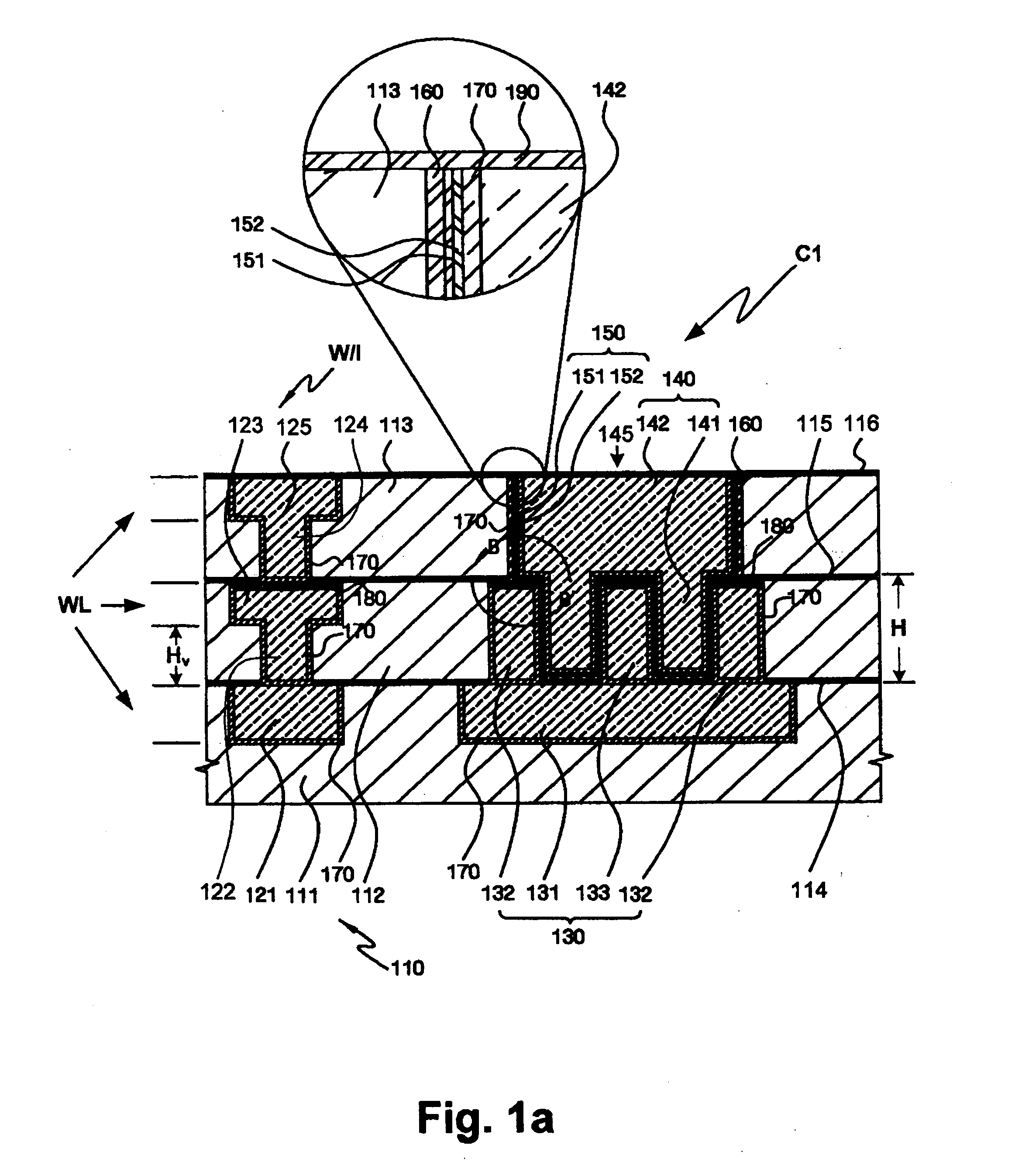

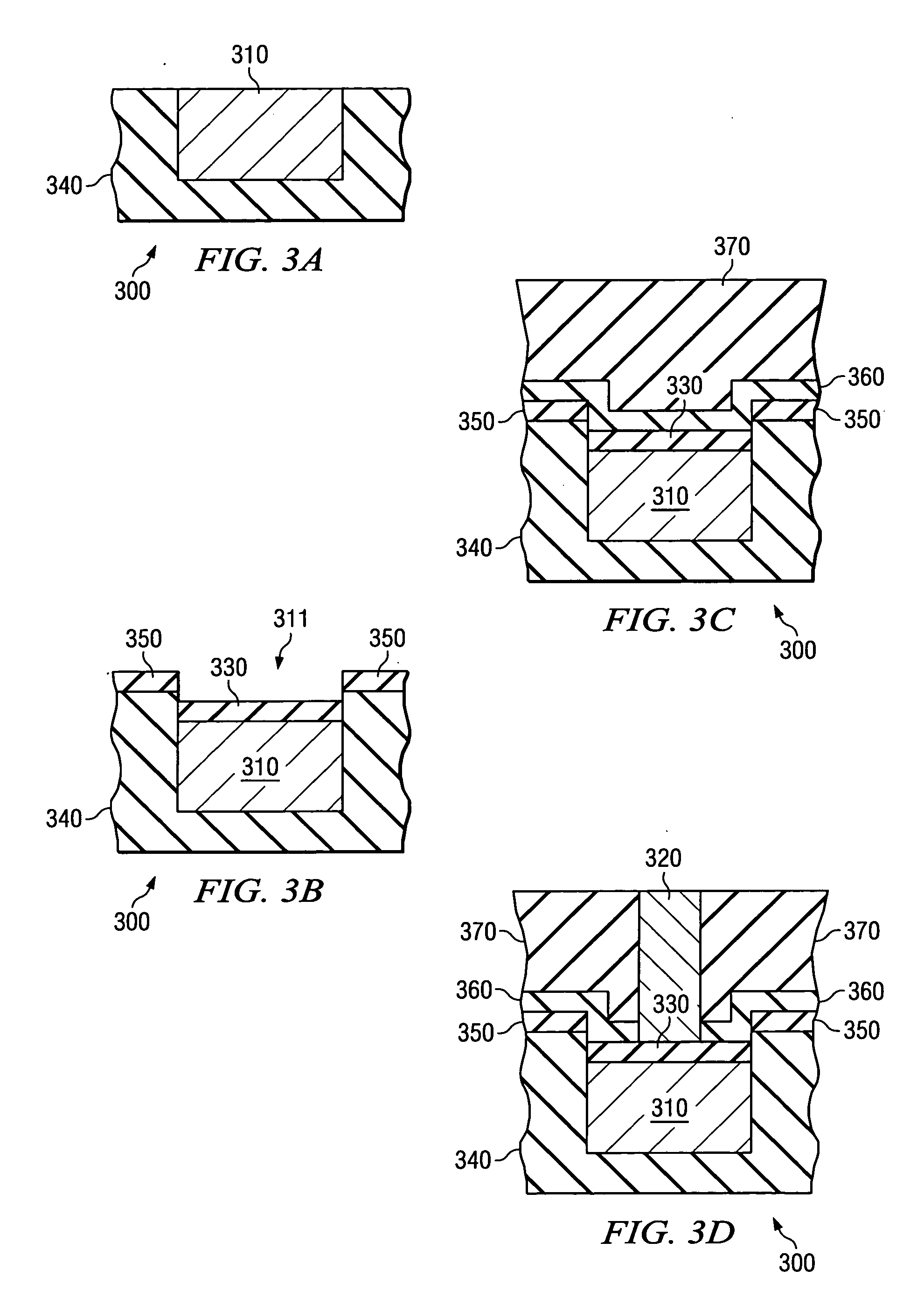

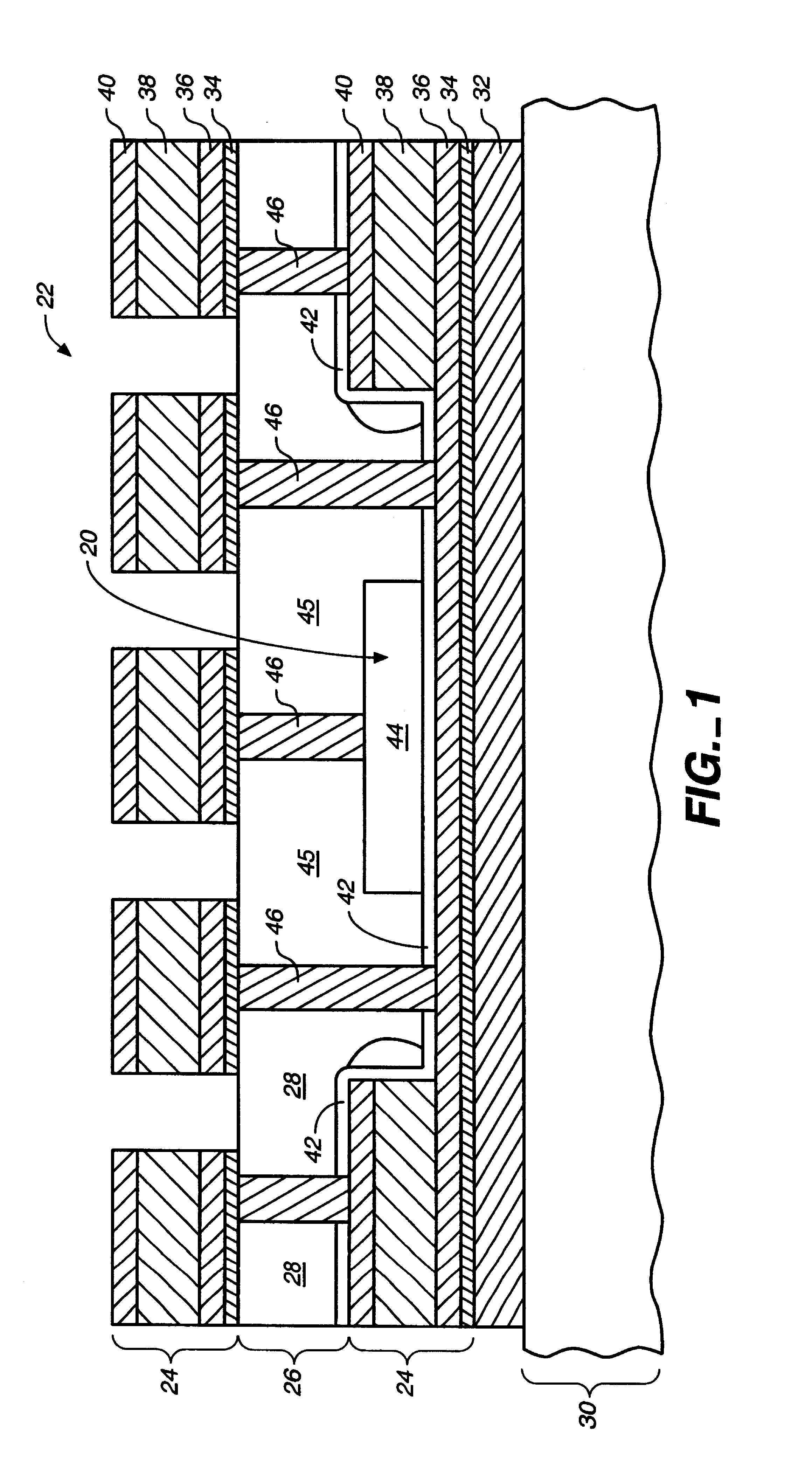

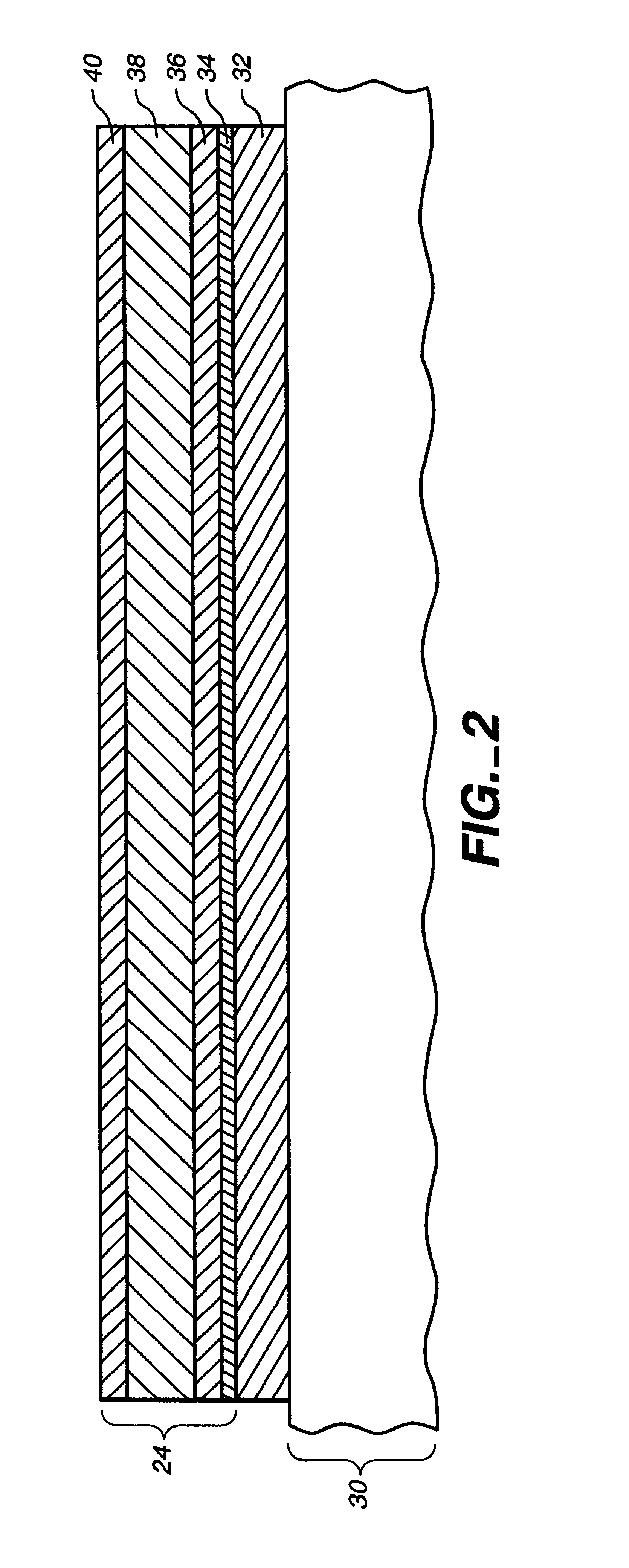

Damascene integration scheme for developing metal-insulator-metal capacitors

InactiveUS20040113235A1Increase capacitanceSave chip areaTransistorSolid-state devicesMetal-insulator-metalGas phase

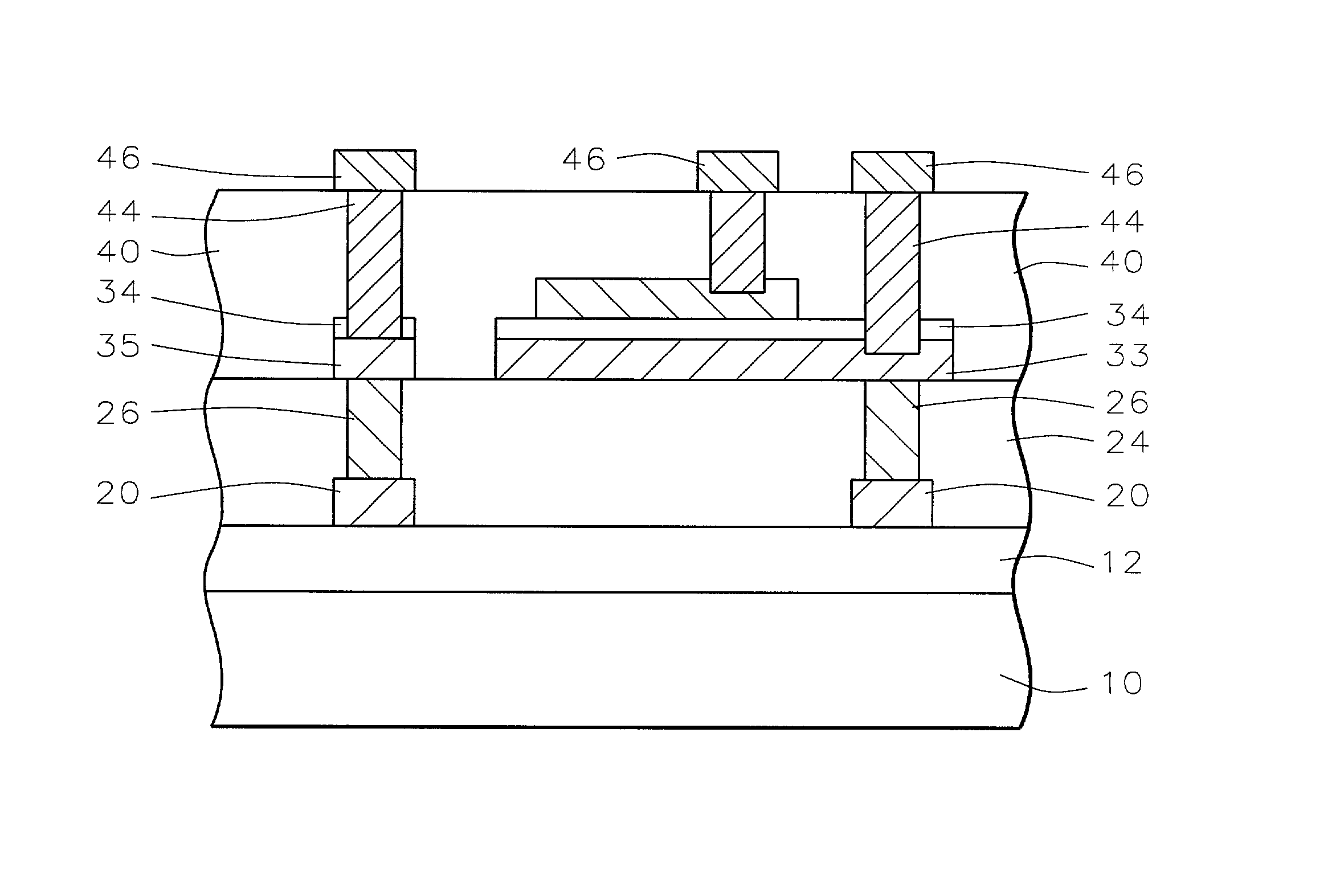

The invention is directed to unique high-surface area BEOL capacitor structures with high-k dielectric layers and methods for fabricating the same. These high-surface area BEOL capacitor structures may be used in analog and mixed signal applications. The capacitor is formed within a trench with pedestals within the trench to provide additional surface area. The top and bottom electrodes are created using damascene integration scheme. The dielectric layer is created as a multilayer dielectric film comprising for instance Al2O3, Al2O3 / Ta2O5, Al2O3 / Ta2O5 / Al2O3 and the like. The dielectric layer may be deposited by methods like atomic layer deposition or chemical vapor deposition. The dielectric layer used in the capacitor may also be produced by anodic oxidation of a metallic precursor to yield a high dielectric constant oxide layer.

Owner:GLOBALFOUNDRIES US INC

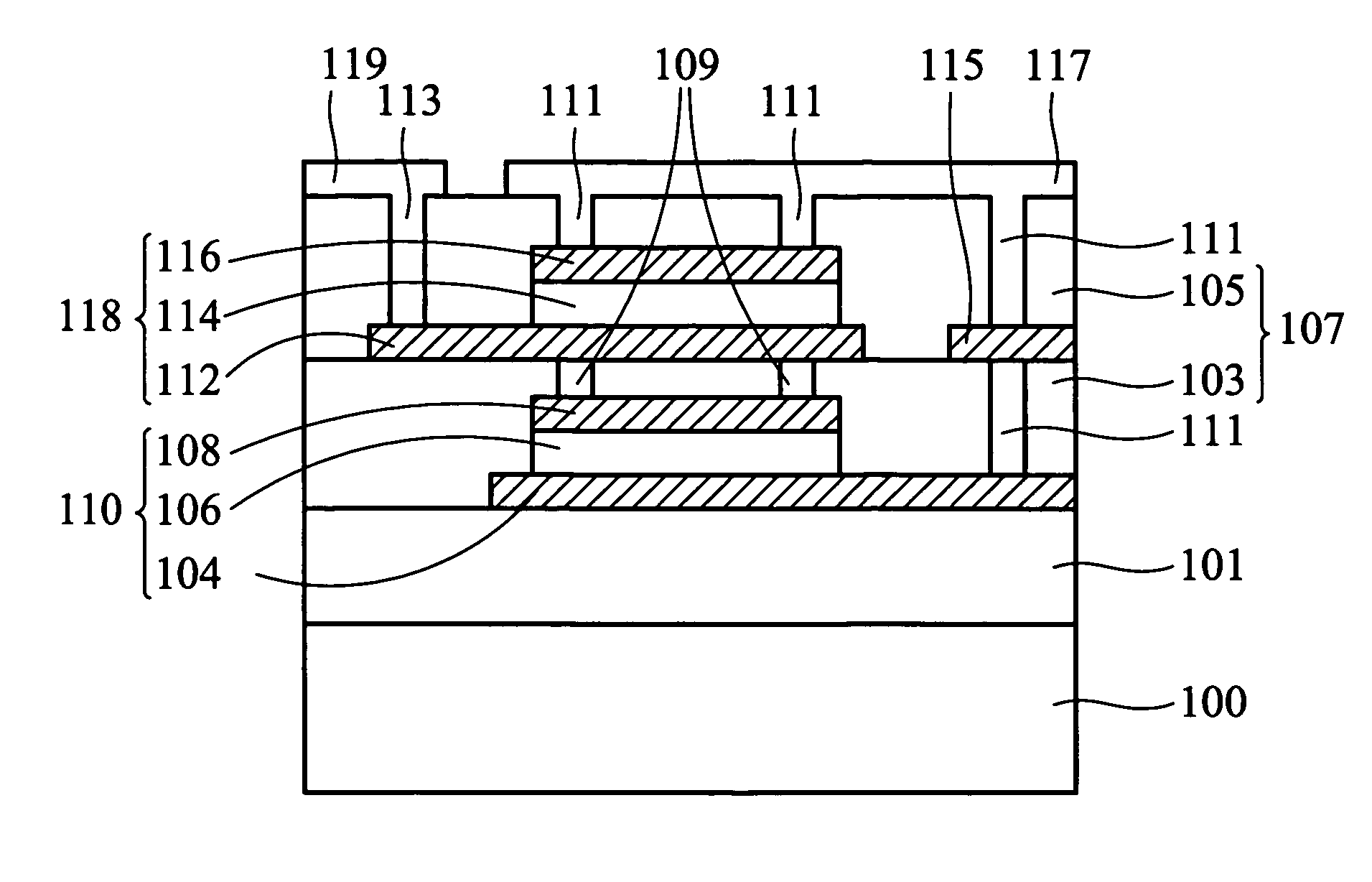

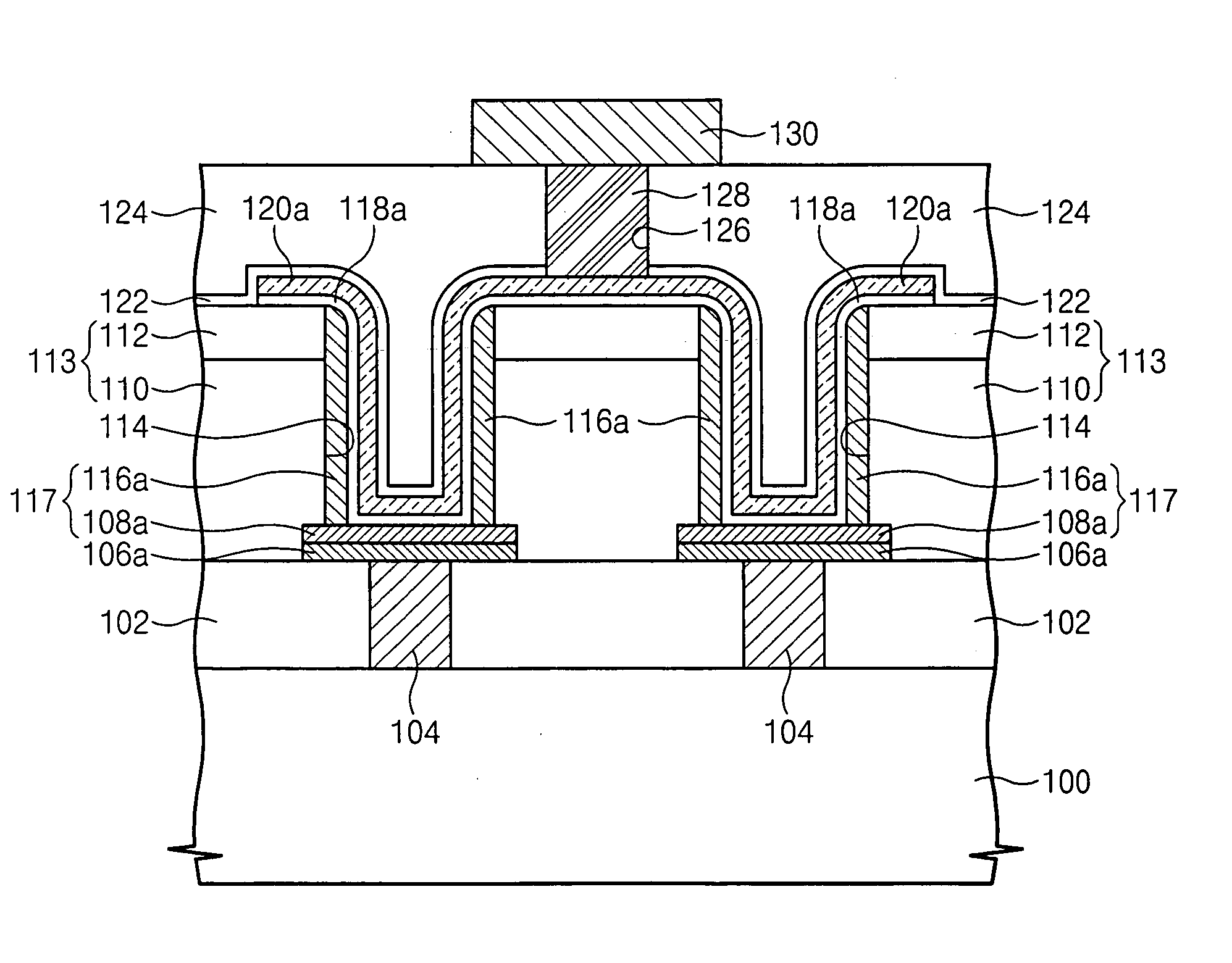

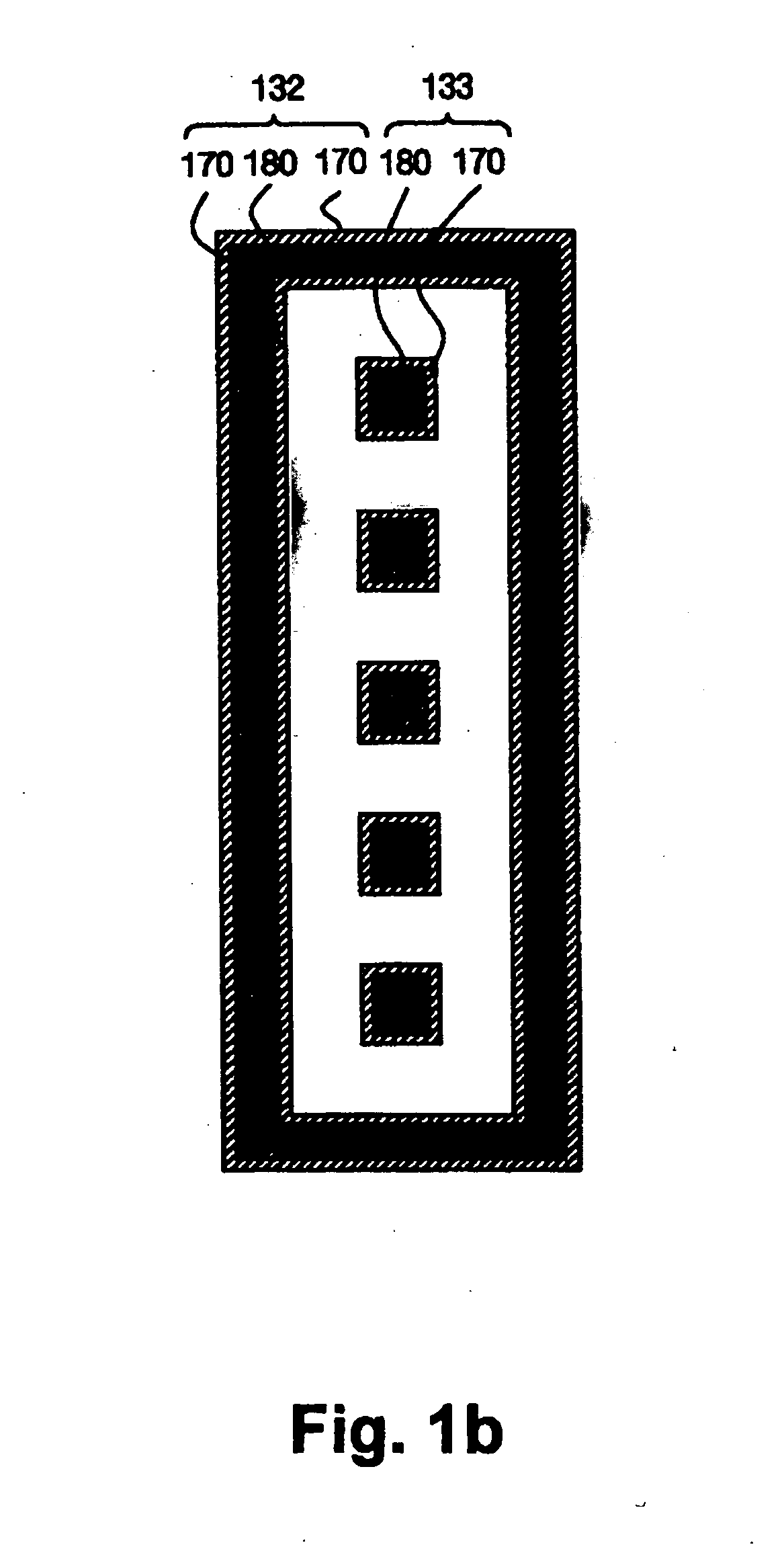

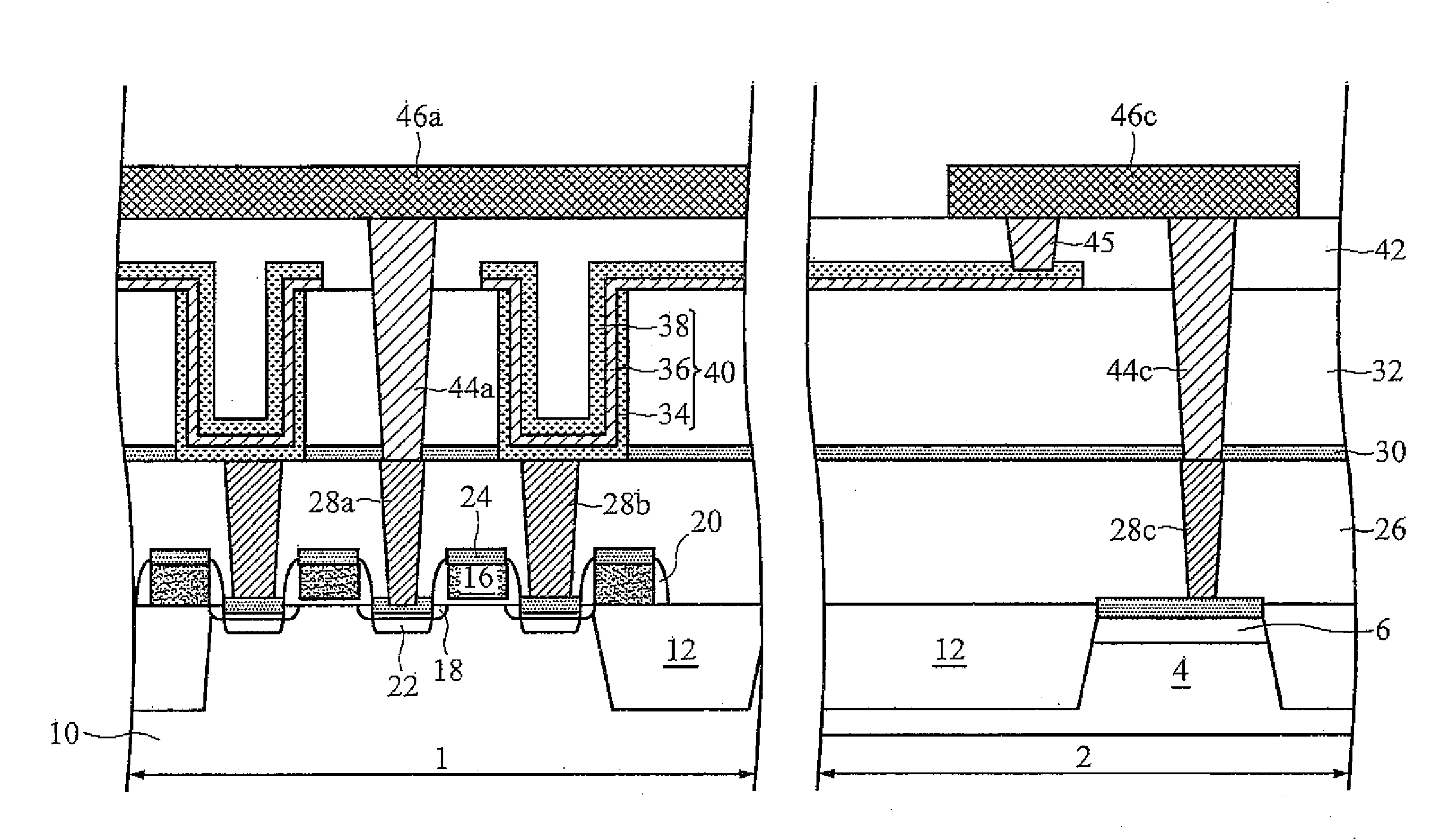

Logic device having vertically extending metal-insulator-metal capacitor between interconnect layers and method of fabricating the same

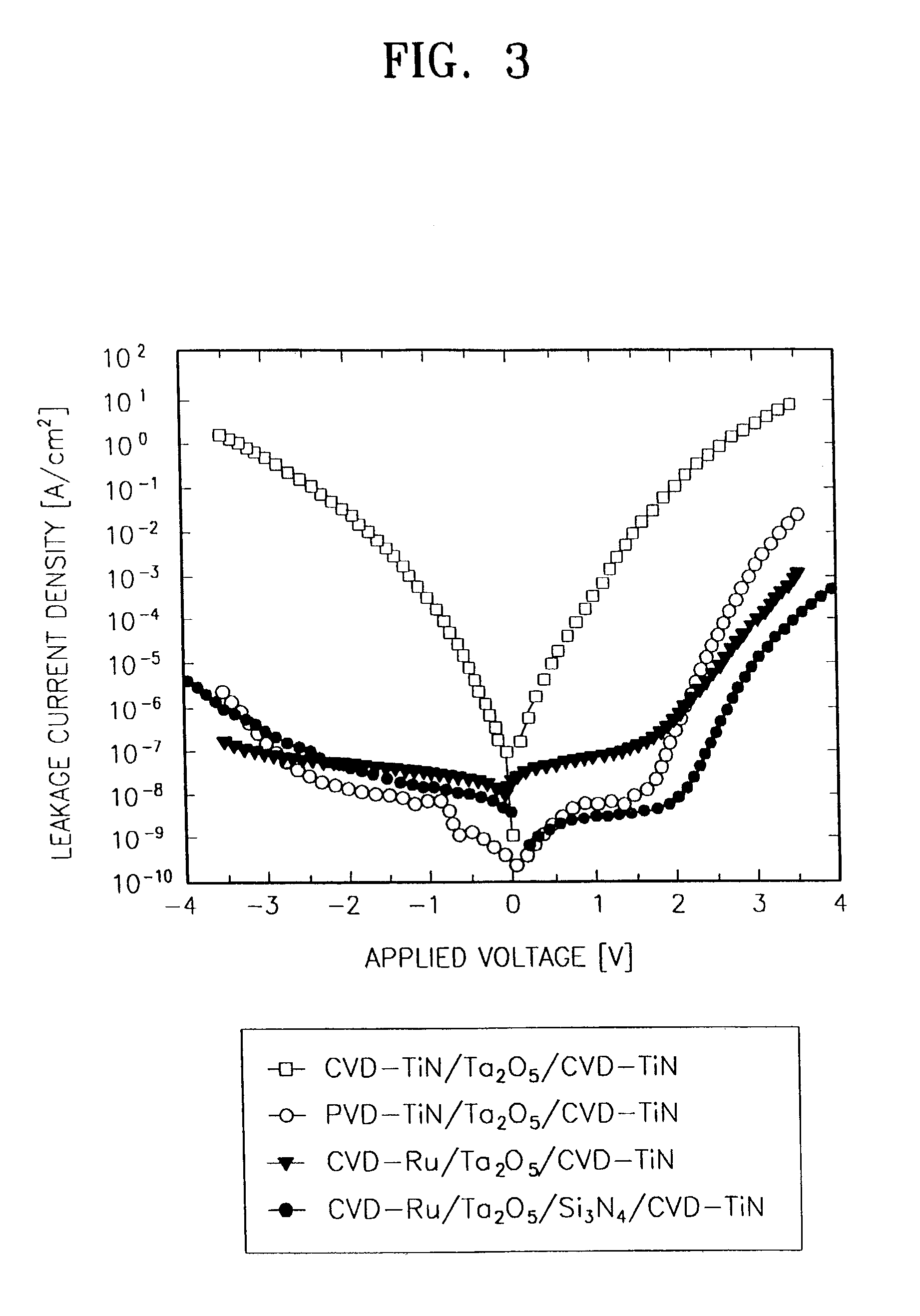

ActiveUS20050087879A1Enhance leakage current characteristicIncrease currentTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

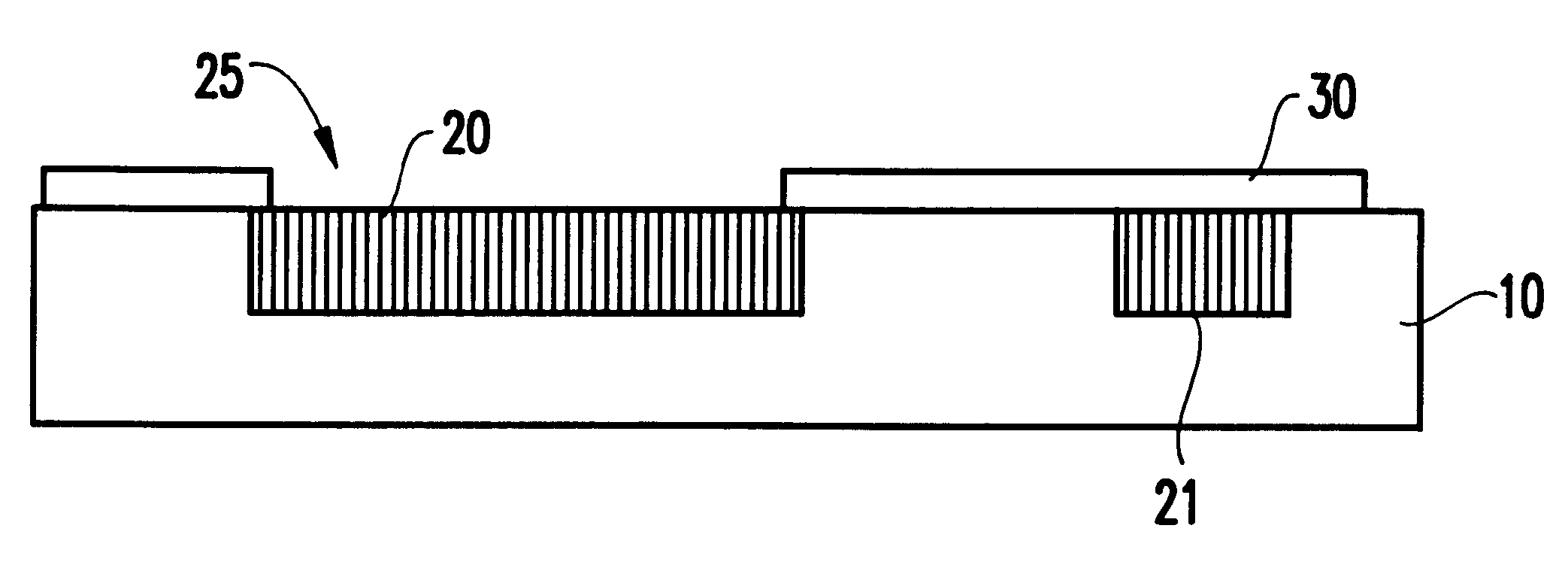

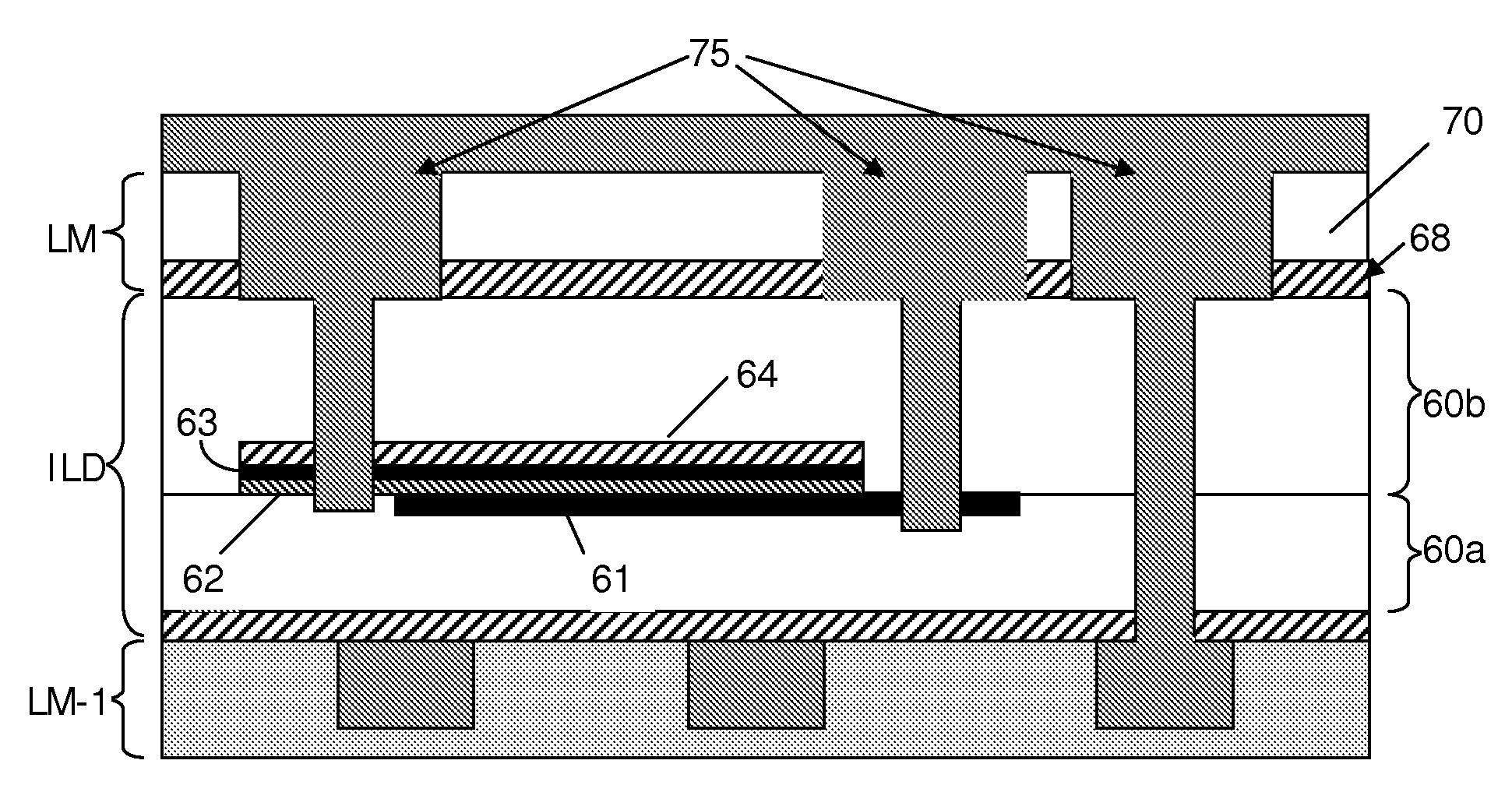

A logic device having a vertically extending MIM capacitor between interconnect layers includes a semiconductor substrate. A lower interconnect layer is located over the semiconductor substrate, and an upper interconnect layer is located over the lower interconnect layer. A U-shaped lower metal plate is interposed between the lower interconnect layer and the upper interconnect layer. The U-shaped lower metal plate directly contacts the lower interconnect layer. The capacitor dielectric layer covers the inner surface of the lower metal plate. Further, the capacitor dielectric layer has an extension portion interposed between the brim of the lower metal plate and the upper interconnect layer. An upper metal plate covers the inner surface of the capacitor dielectric layer. The upper metal plate is in contact with the upper interconnect layer and is confined by the capacitor dielectric layer.

Owner:SAMSUNG ELECTRONICS CO LTD

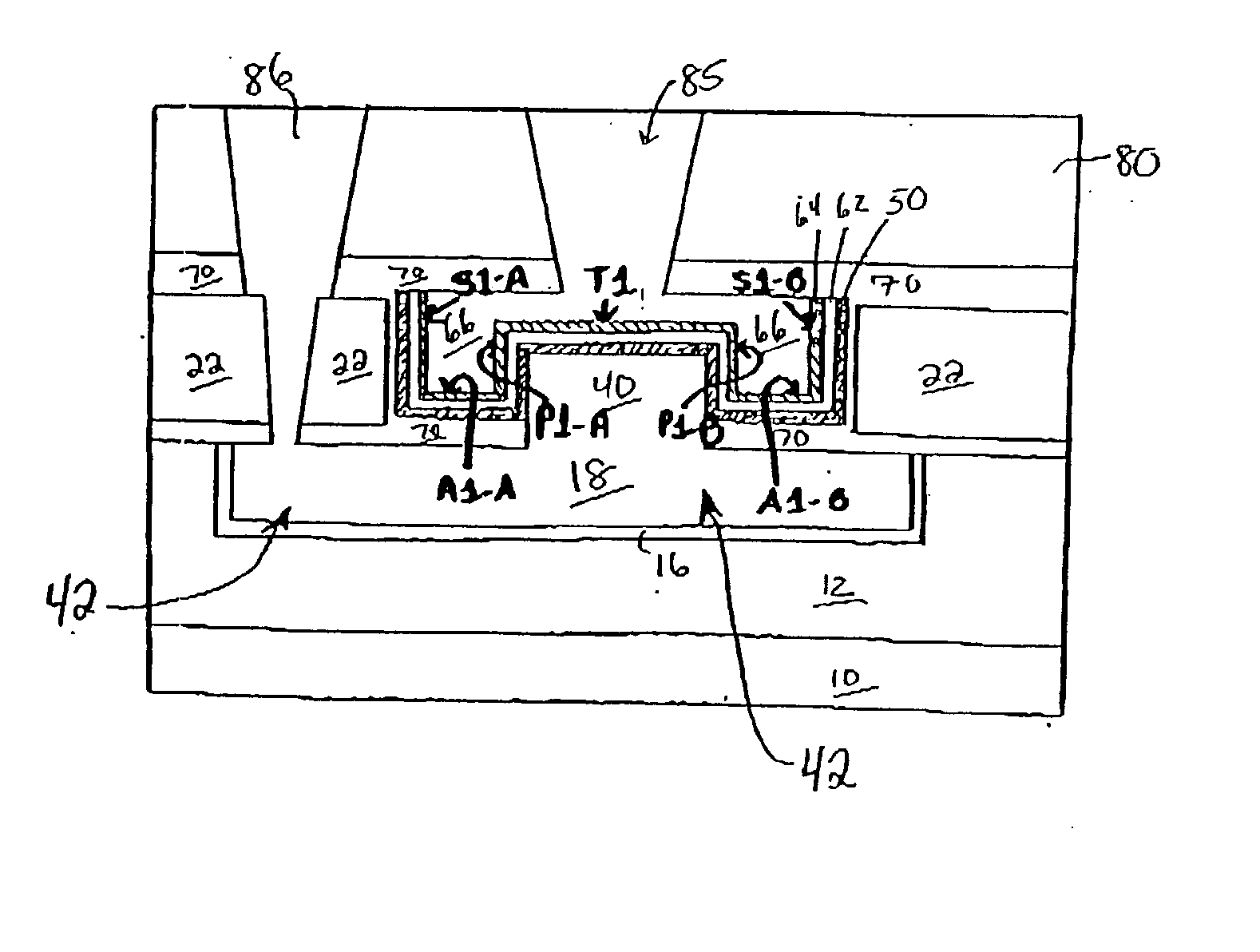

Pixel sensor cell including light shield

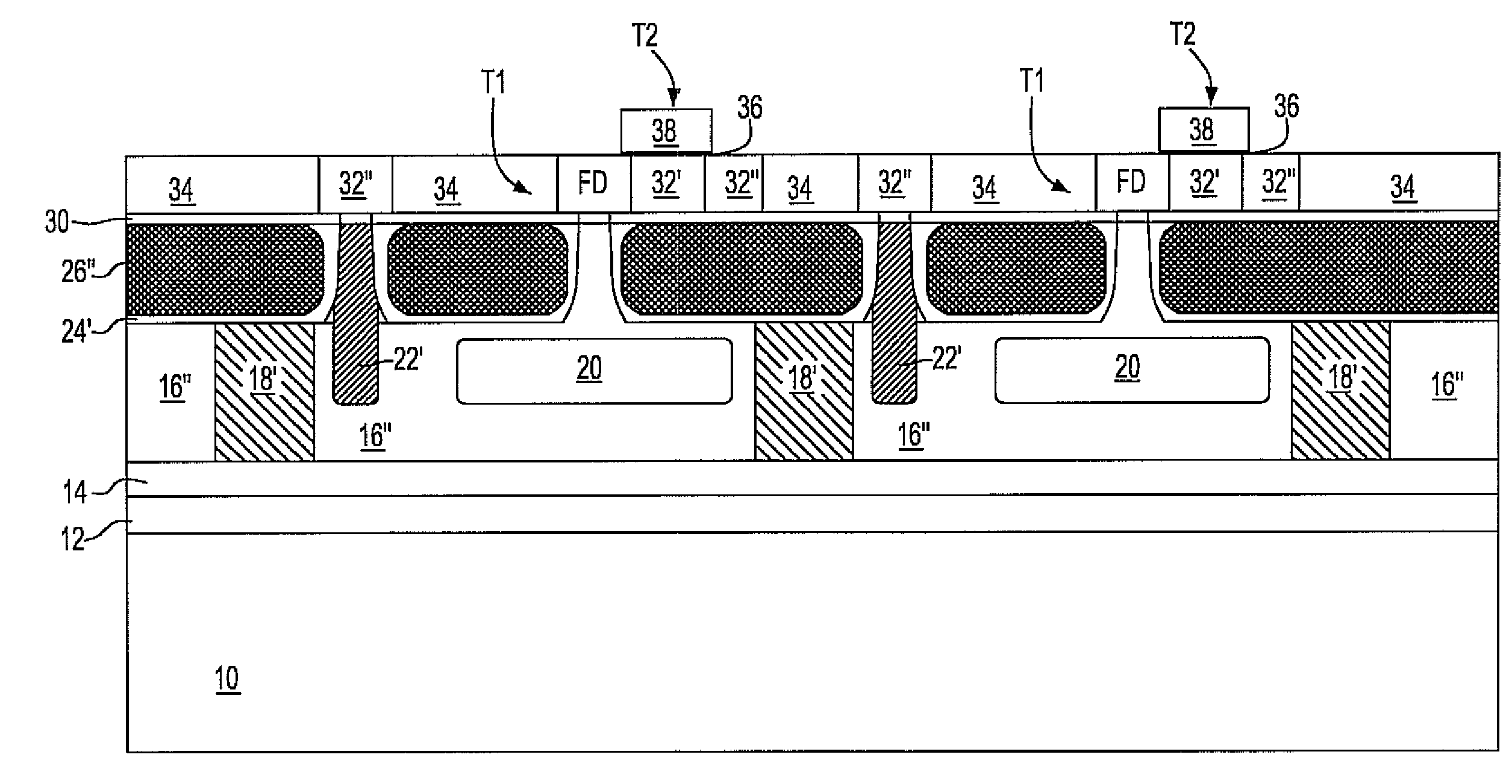

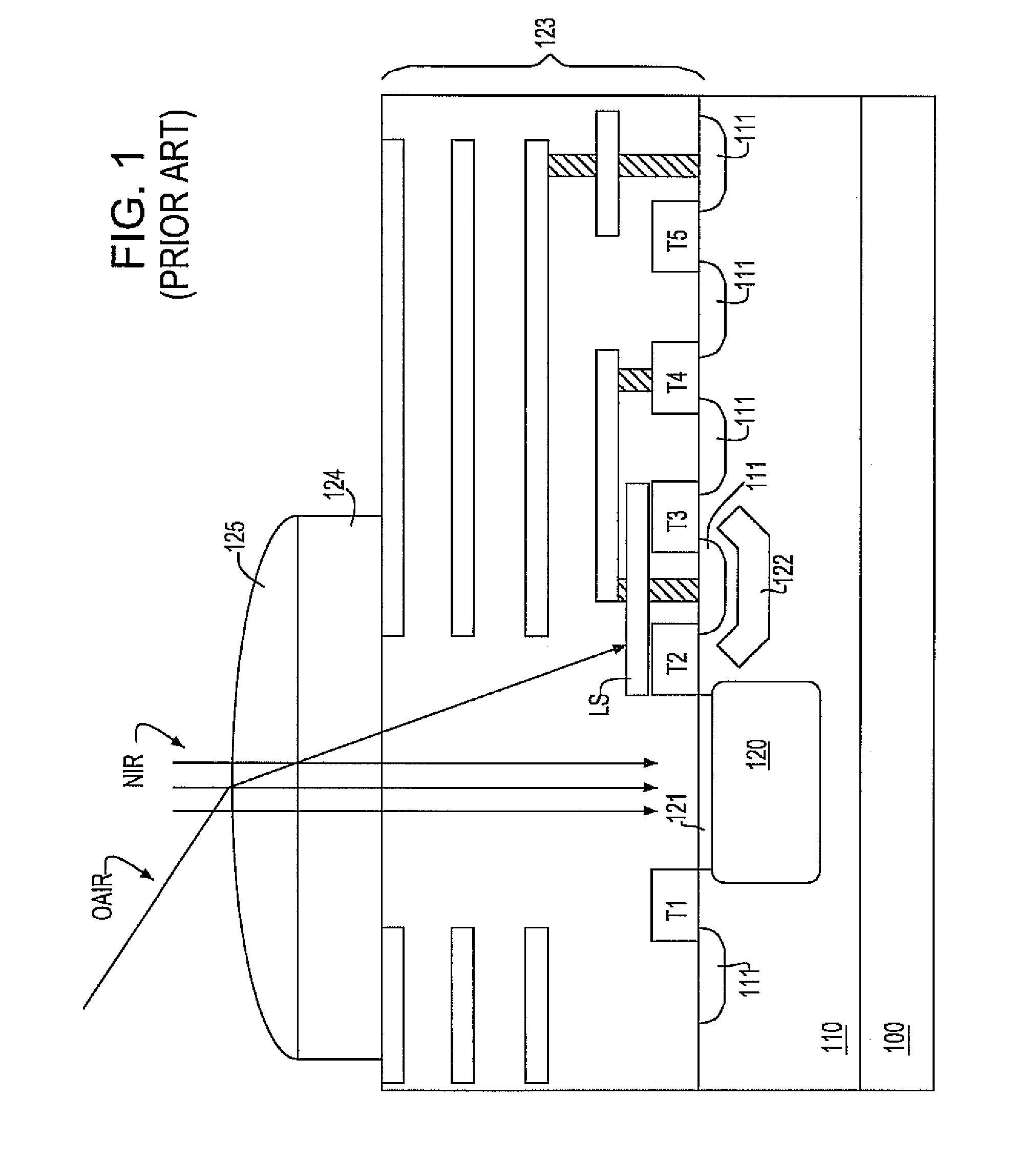

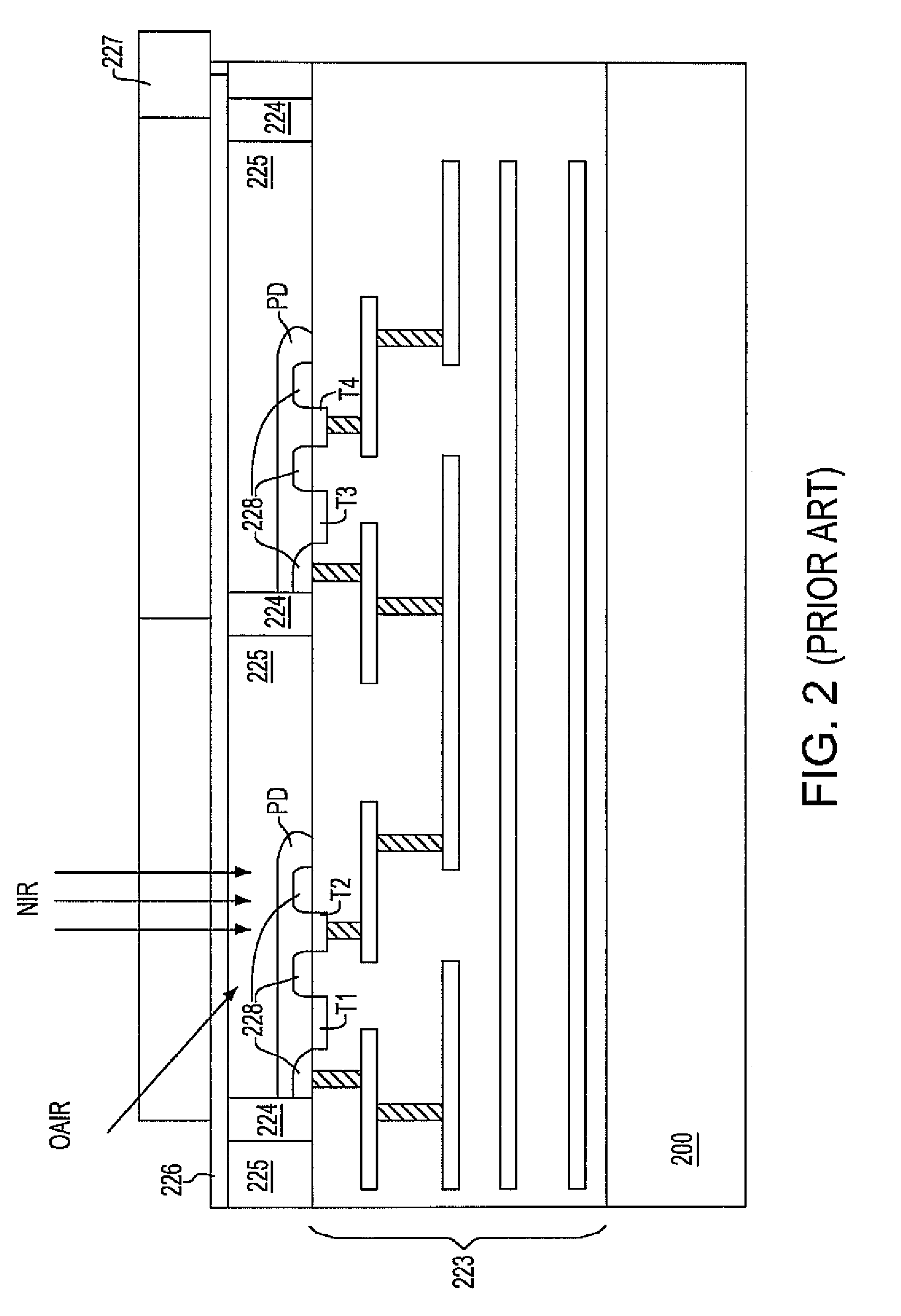

ActiveUS20100230729A1Avoids spurious light effectSolid-state devicesSemiconductor/solid-state device manufacturingCMOSElectrical conductor

CMOS image sensor pixel sensor cells, methods for fabricating the pixel sensor cells and design structures for fabricating the pixel sensor cells are designed to allow for back side illumination in global shutter mode by providing light shielding from back side illumination of at least one transistor within the pixel sensor cells. In a first particular generalized embodiment, a light shielding layer is located and formed interposed between a first semiconductor layer that includes a photoactive region and a second semiconductor layer that includes the at least a second transistor, or a floating diffusion, that is shielded by the light blocking layer. In a second generalized embodiment, a thin film transistor and a metal-insulator-metal capacitor are used in place of a floating diffusion, and located shielded in a dielectric isolated metallization stack over a carrier substrate

Owner:GLOBALFOUNDRIES US INC

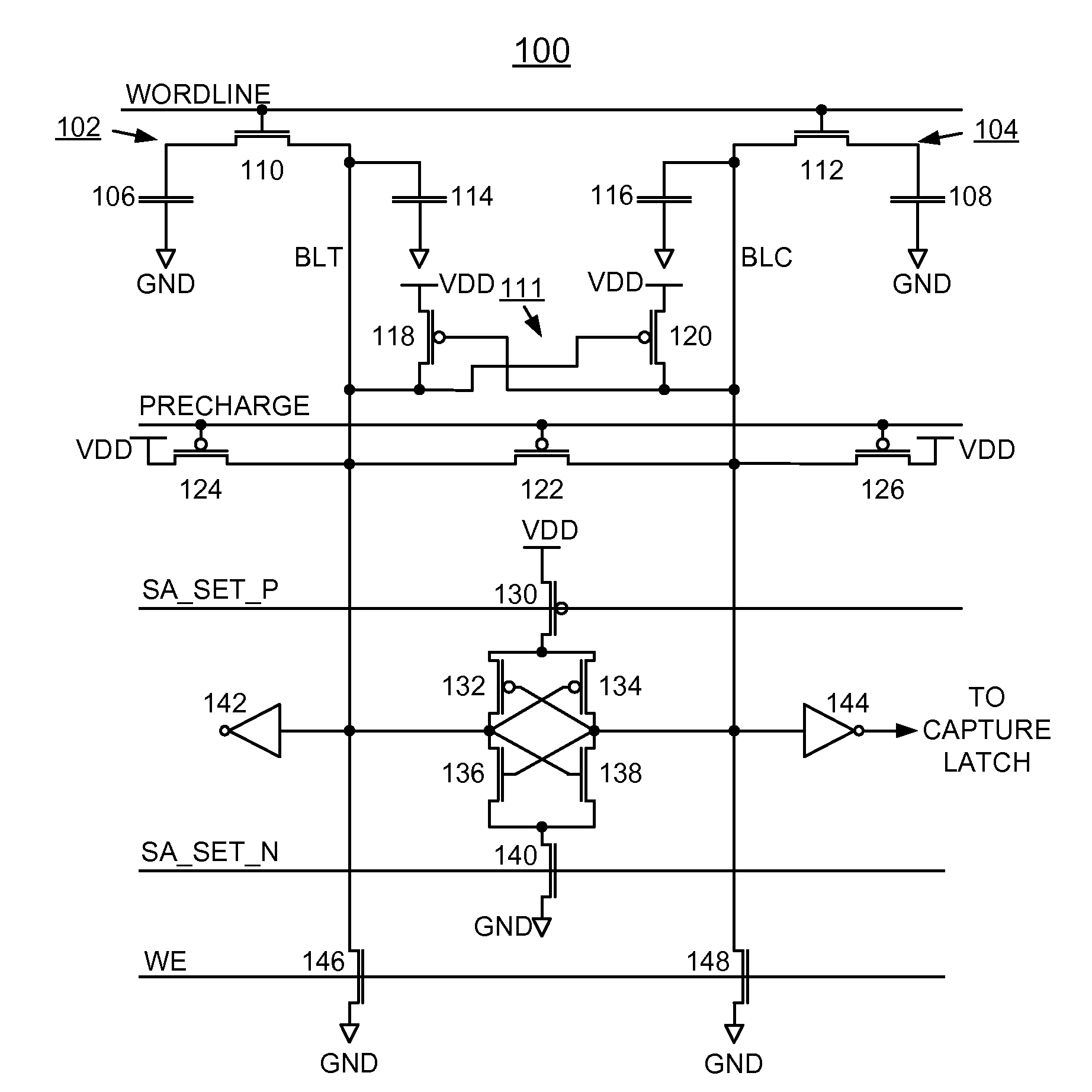

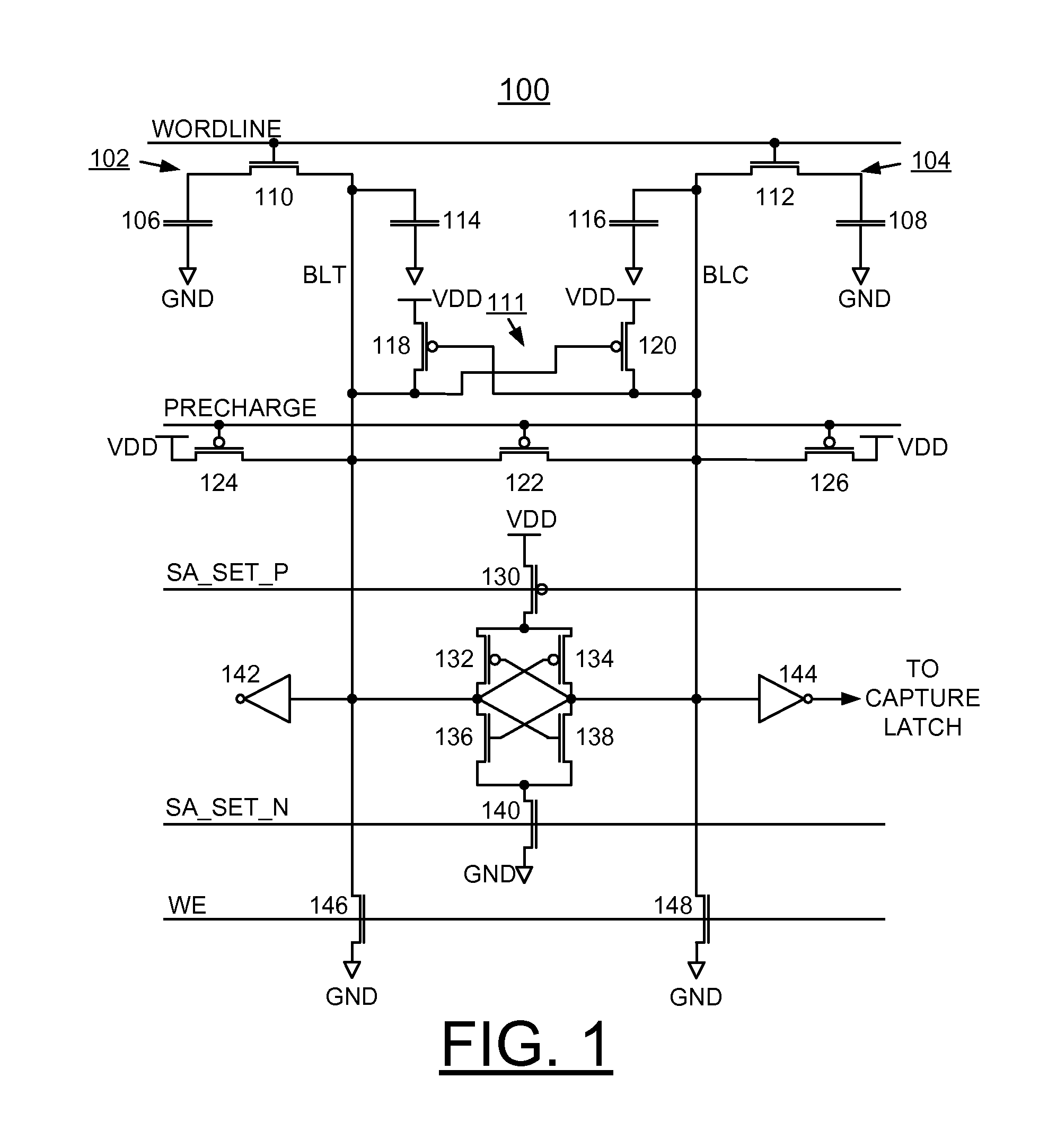

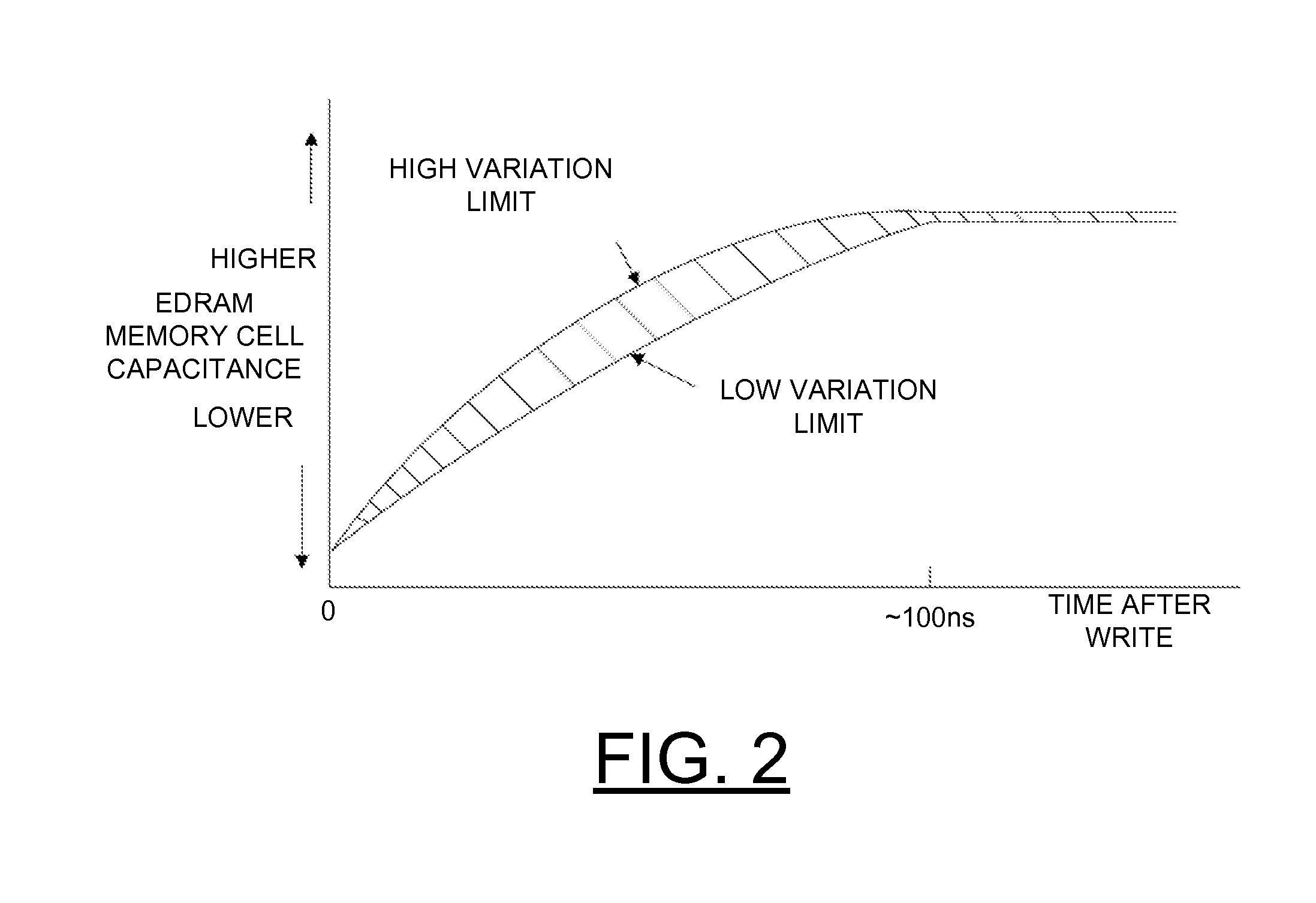

Implementing physically unclonable function (PUF) utilizing edram memory cell capacitance variation

ActiveUS20120106235A1Overcome disadvantagesDigital data processing detailsDigital storageCapacitanceMetal-insulator-metal

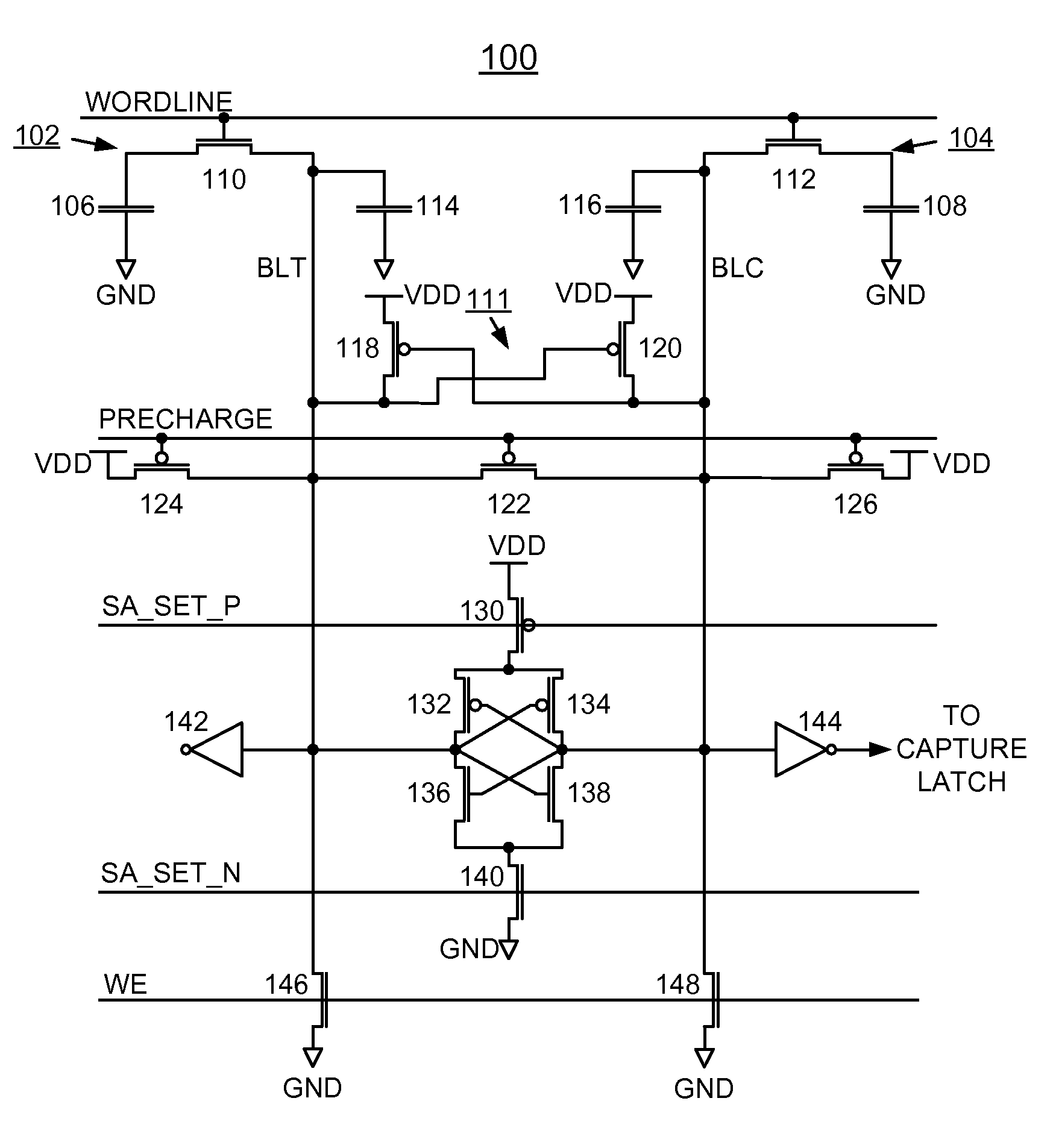

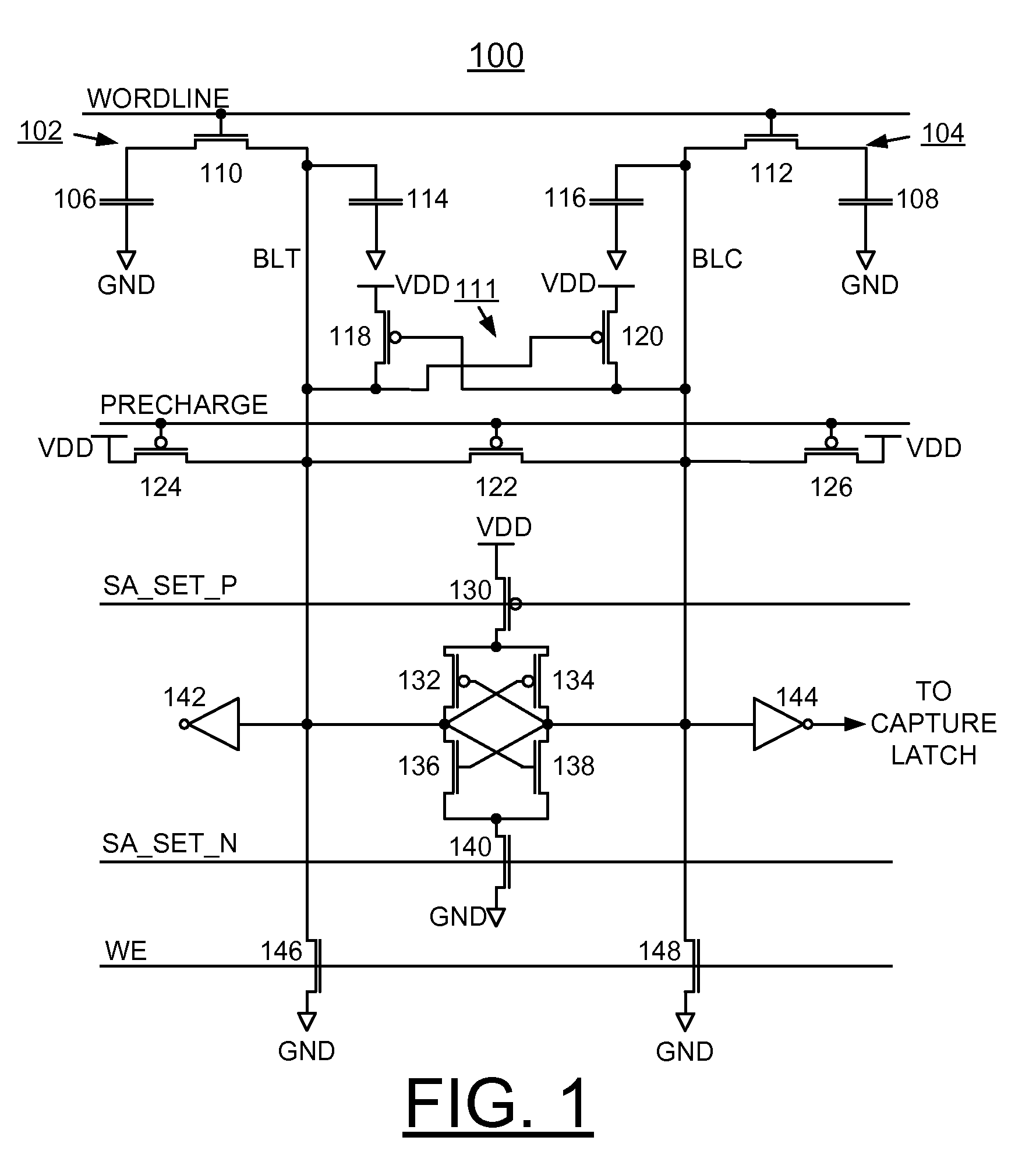

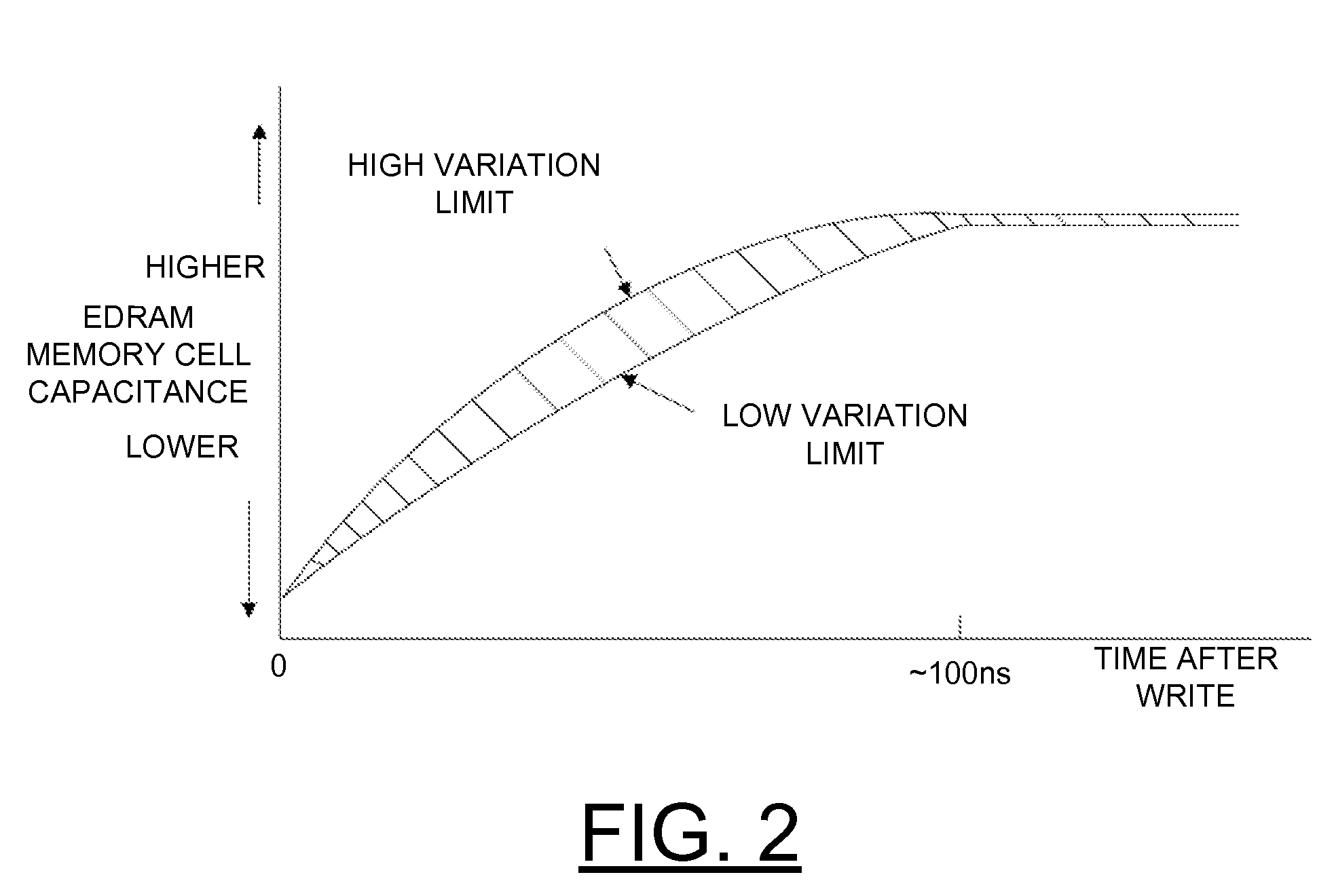

A method and embedded dynamic random access memory (EDRAM) circuit for implementing a physically unclonable function (PUF), and a design structure on which the subject circuit resides are provided. An embedded dynamic random access memory (EDRAM) circuit includes a first EDRAM memory cell including a memory cell true storage capacitor and a second EDRAM memory cell including a memory cell complement storage capacitor. The memory cell true storage capacitor and the memory cell complement storage capacitor include, for example, trench capacitors or metal insulator metal capacitors (MIM caps). A random variation of memory cell capacitance is used to implement the physically unclonable function. Each memory cell is connected to differential inputs to a sense amplifier. The first and second EDRAM memory cells are written to zero and then the first and second EDRAM memory cells are differentially sensed and the difference is amplified to consistently read the same random data.

Owner:MARVELL ASIA PTE LTD

Method of fabrication of thin film resistor with zero TCR

InactiveUS6890810B2Reduce interfacial resistanceKeep shapeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringEffective temperature

A thin film resistor that has a substantially zero TCR is provided as well as a method for fabricating the same. The thin film resistor includes at least two resistor materials located over one another. Each resistor material has a different temperature coefficient of resistivity such that the effective temperature coefficient of resistivity of the thin film resistor is substantially 0 ppm / ° C. The thin film resistor may be integrated into a interconnect structure or it may be integrated with a metal-insulator-metal capacitor (MIMCAP).

Owner:IBM CORP

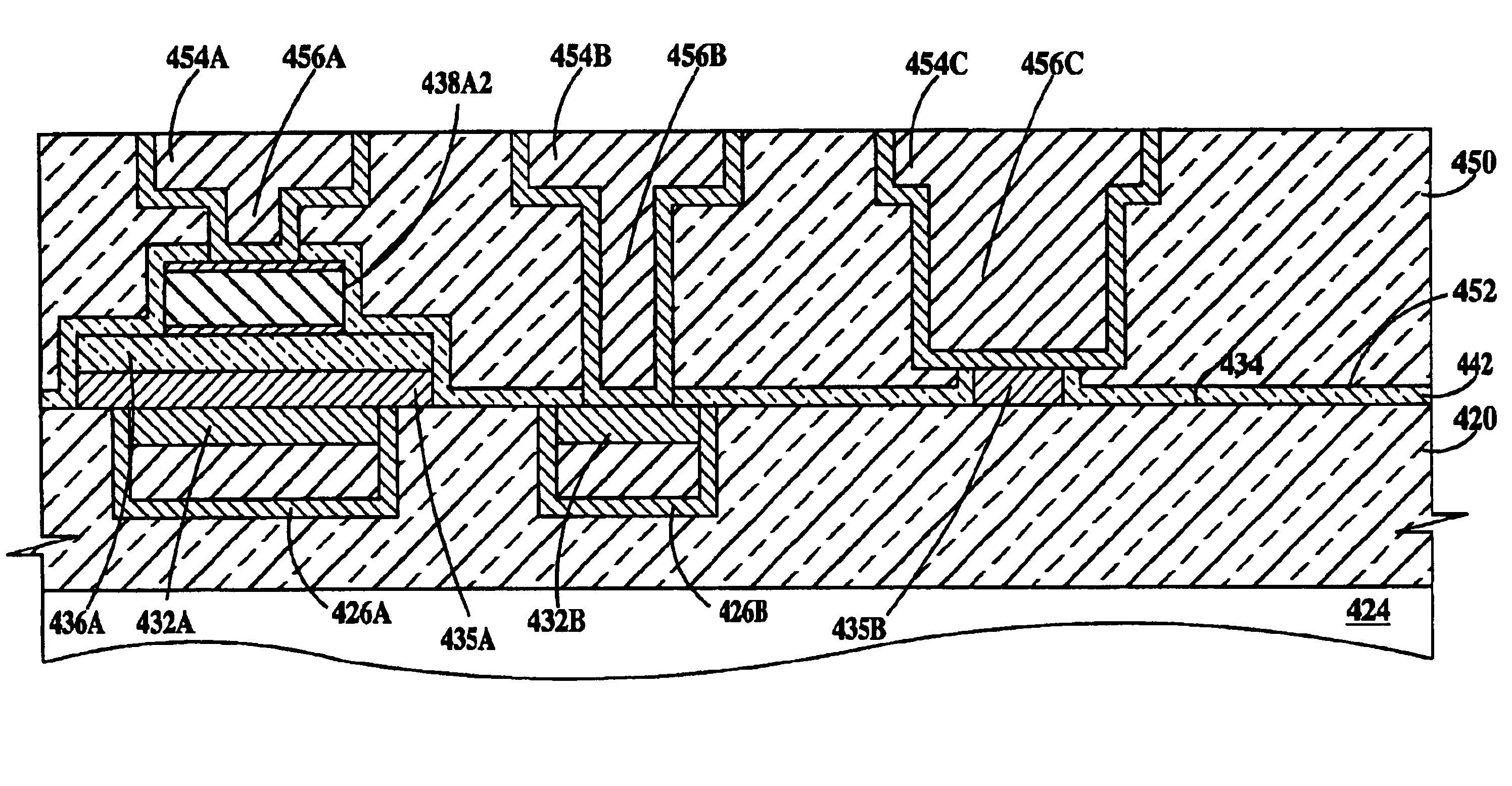

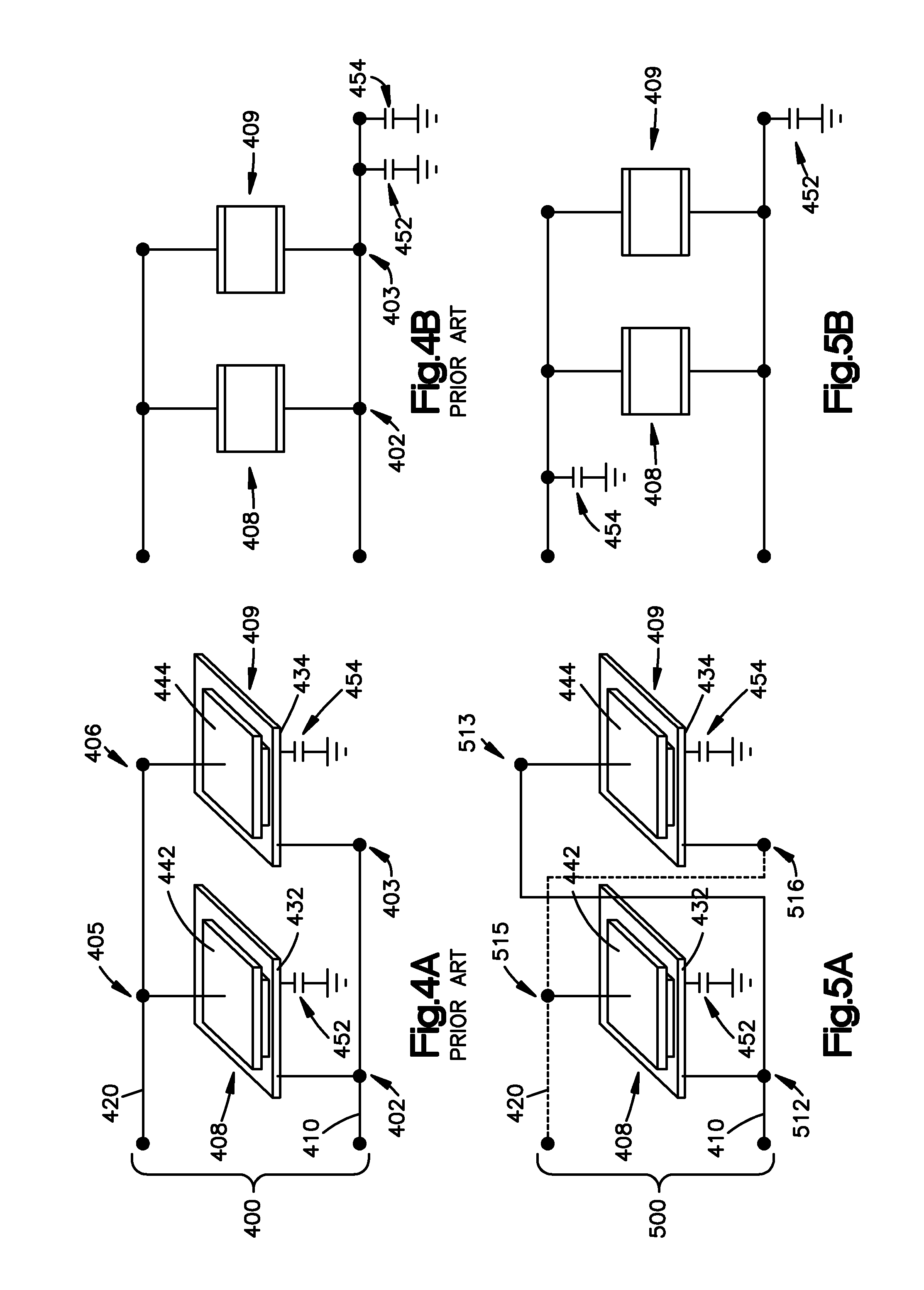

MIM capacitor integration

ActiveUS20090200638A1TransistorSolid-state devicesElectrical conductorMetal insulator metal capacitor

An integrated metal-insulator-metal capacitor is formed so that there is an extension portion of its top plate that does not face any portion of the bottom plate, and an extension portion of its bottom plate that does not face any portion of the top plate. Vias connecting the MIM capacitor plates to conductors in an overlying metallization layer are formed so as to contact the extension portions of the top and bottom plates. Etching of the via holes is simplified because it is permissible for the via holes to punch through the extension portions of the capacitor plates. The bottom plate of the MIM capacitor is inlaid. The top plate of the MIM capacitor may be inlaid.

Owner:III HLDG 12 LLC

High density metal capacitor using dual-damascene copper interconnect

InactiveUS20020038903A1Semiconductor/solid-state device detailsSolid-state devicesElectronic structureCopper interconnect

An electronic structure having a first conductive layer provided by a dual damascene fabrication process; an etch-stop layer provided by the fabrication process, and electrically coupled with the first conductive layer, the etch-stop layer having a preselected dielectric constant and a predetermined geometry; and a second conductive layer, electrically coupled with the etch-stop layer. The structure can be, for example, a metal-insulator-metal capacitor, an antifuse, and the like.

Owner:AVAGO TECH INT SALES PTE LTD

Metal-insulator-metal capacitor structure having low voltage dependence

InactiveUS20070152295A1Extended working voltage rangeIncrease capacitance densityTransistorSemiconductor/solid-state device detailsCapacitanceLow voltage

A semiconductor capacitor device. A dielectric layer is on a substrate. A stack capacitor structure is disposed in the dielectric layer and comprises first and overlying second MIM capacitors electrically connected in parallel. The first and second MIM capacitors have individual upper and lower electrode plates and different compositions of capacitor dielectric layers.

Owner:TAIWAN SEMICON MFG CO LTD

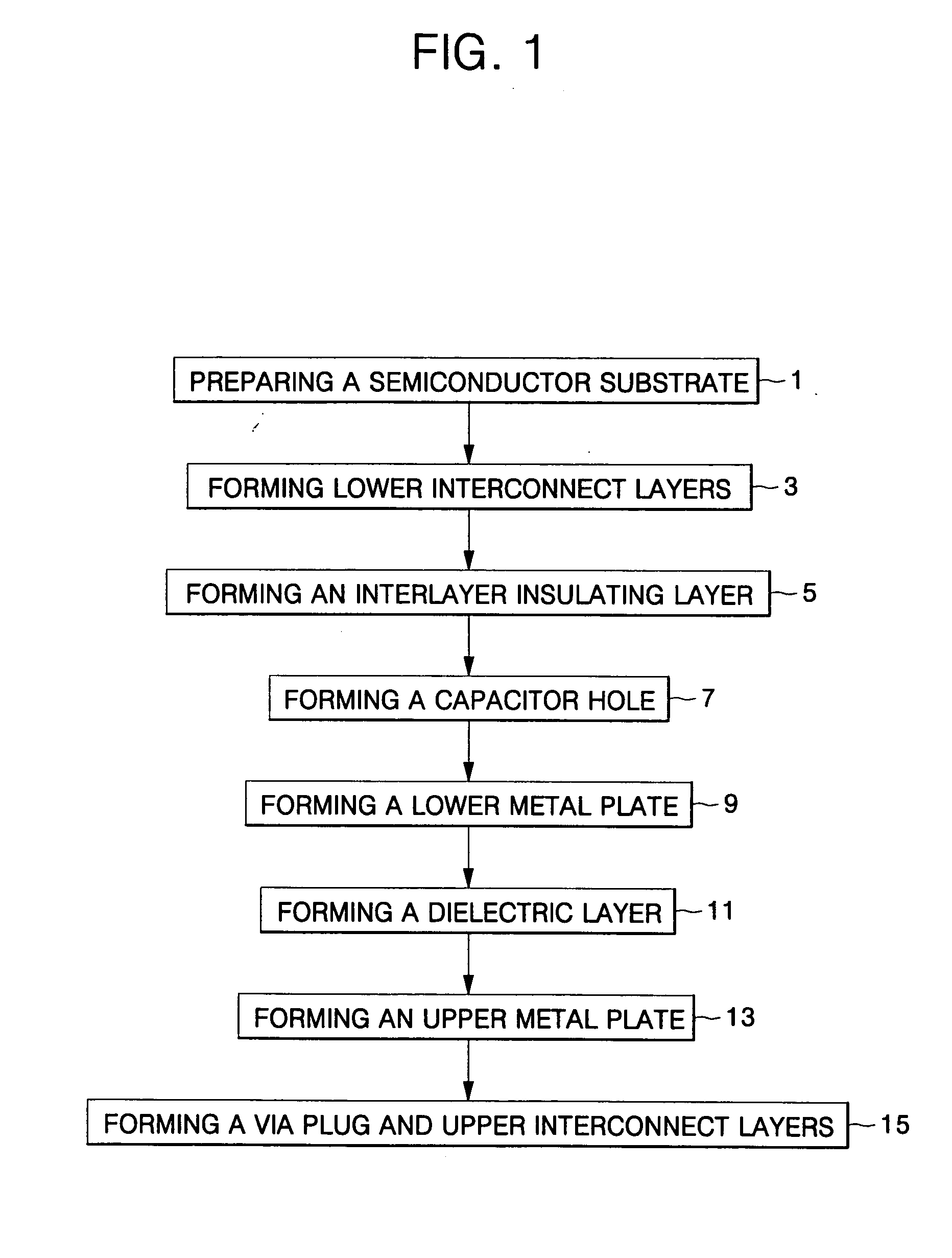

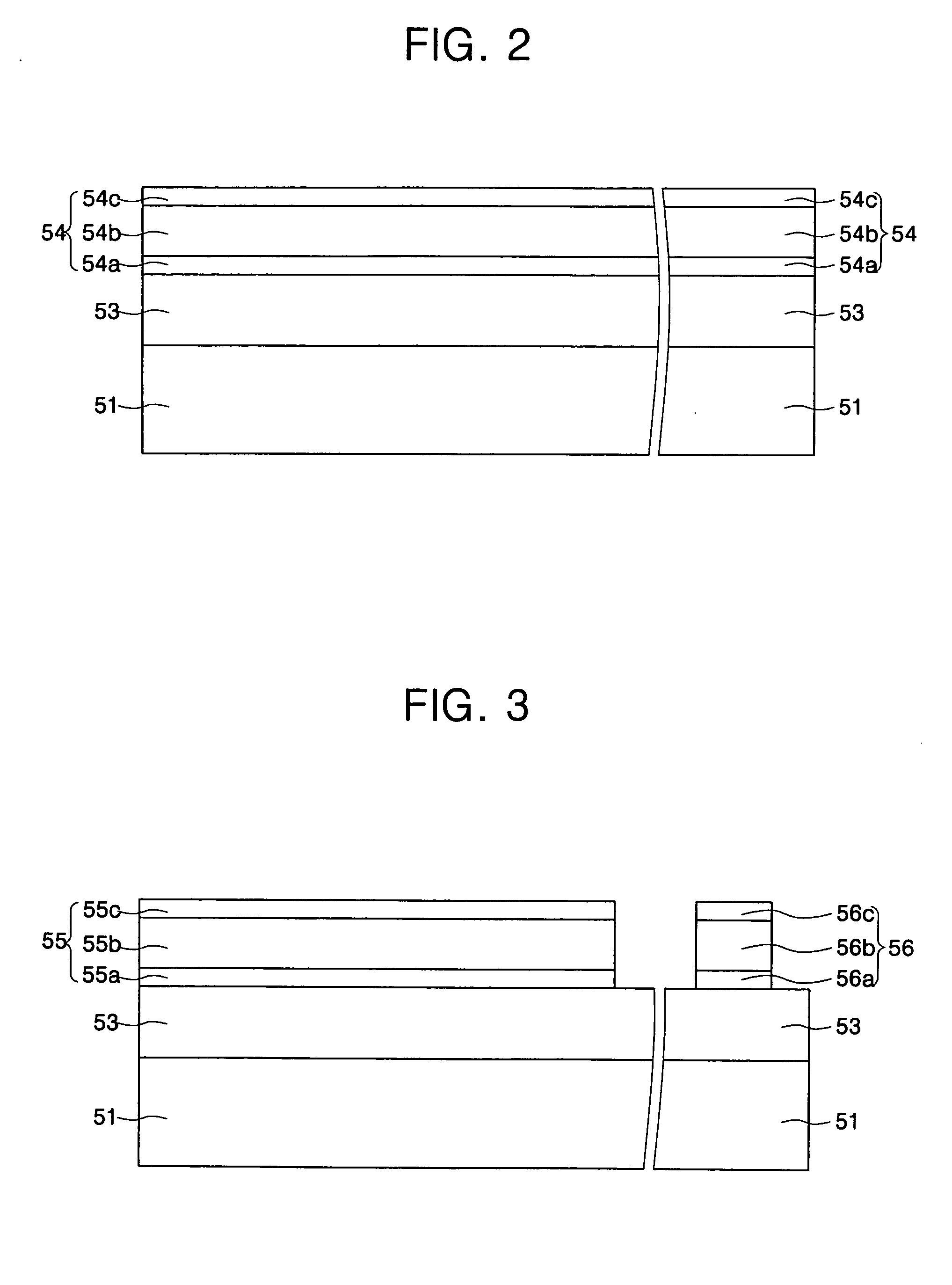

Semiconductor device having a metal-insulator-metal capacitor

A method for manufacturing a semiconductor device having a metal-insulator-metal (MIM) capacitor comprises the steps of forming a first dielectric film on a substrate, forming a MIM capacitor on the first dielectric film, forming a second dielectric film covering the MIM capacitor, selectively removing the first and second dielectric films to expose the substrate surface, surface treating using a hydrochloric acid solution, forming a third dielectric film on the second dielectric film and the substrate, and forming a transistor on the third dielectric film. The second dielectric film protects the capacitor insulator film of the MIM capacitor.

Owner:NEC CORP

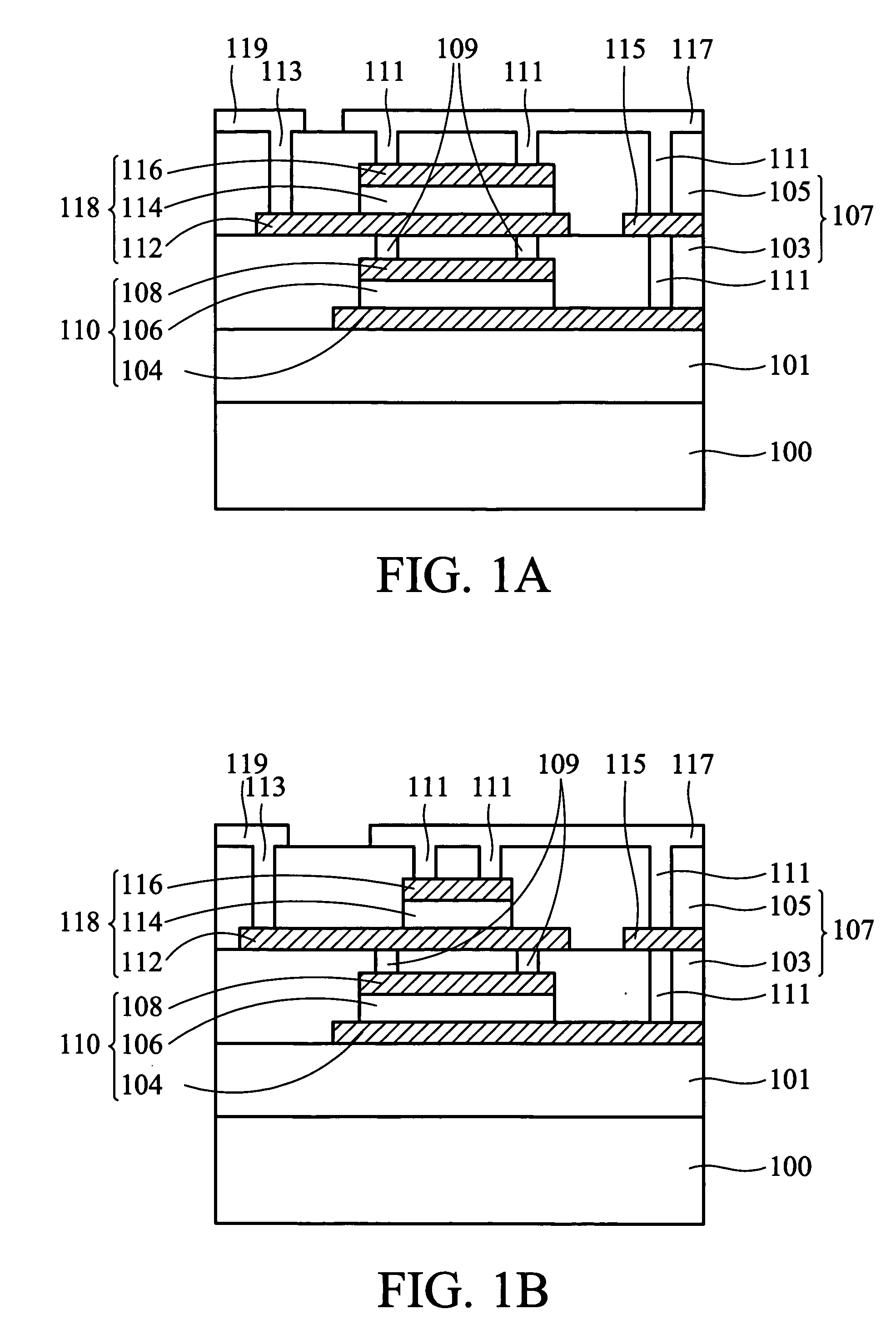

Metal-insulator-metal capacitors

A metal-insulator-metal (MIM) capacitor is provided. The bottom electrode of the MIM capacitor is electrically connected to a connection node. The connection node may be, for example, a contact formed in an interlayer dielectric, a polysilicon connection node, a doped polysilicon or silicon region, or the like. A contact provides an electrical connection between the connection node and components formed above the connection node. A second contact provides an electrical connection to the top electrode.

Owner:TAIWAN SEMICON MFG CO LTD

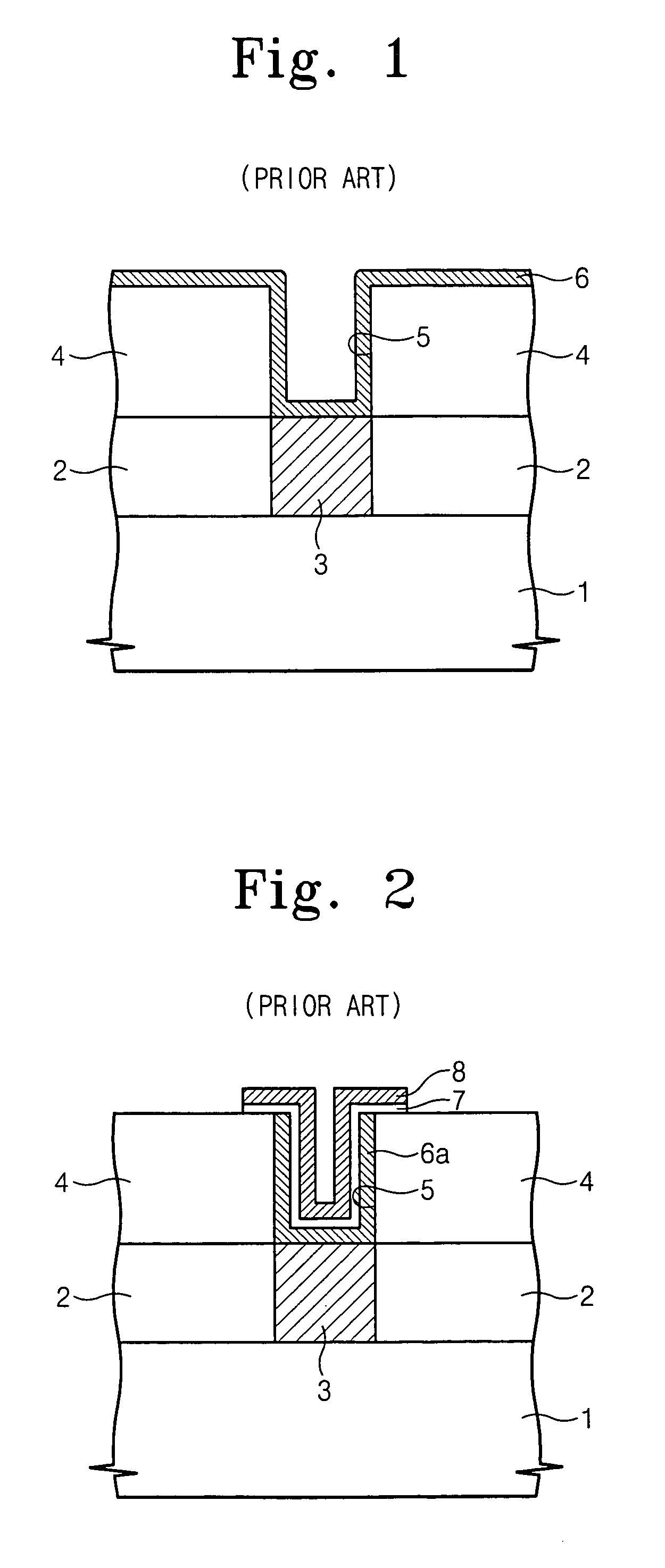

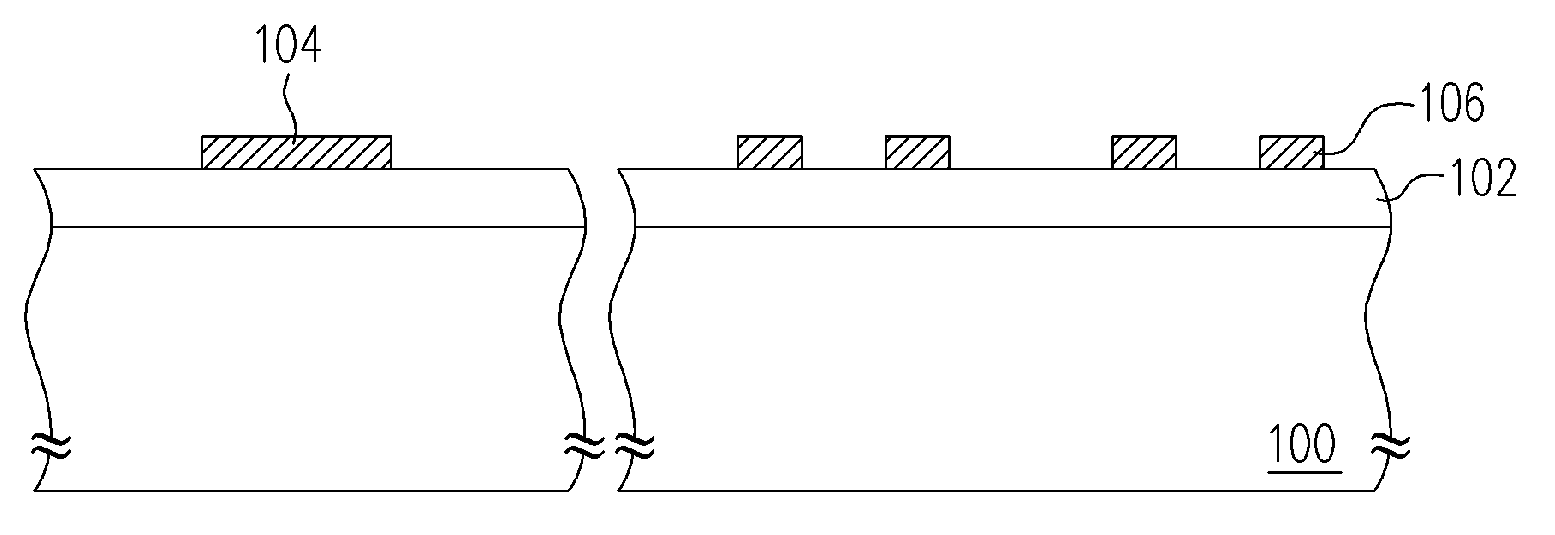

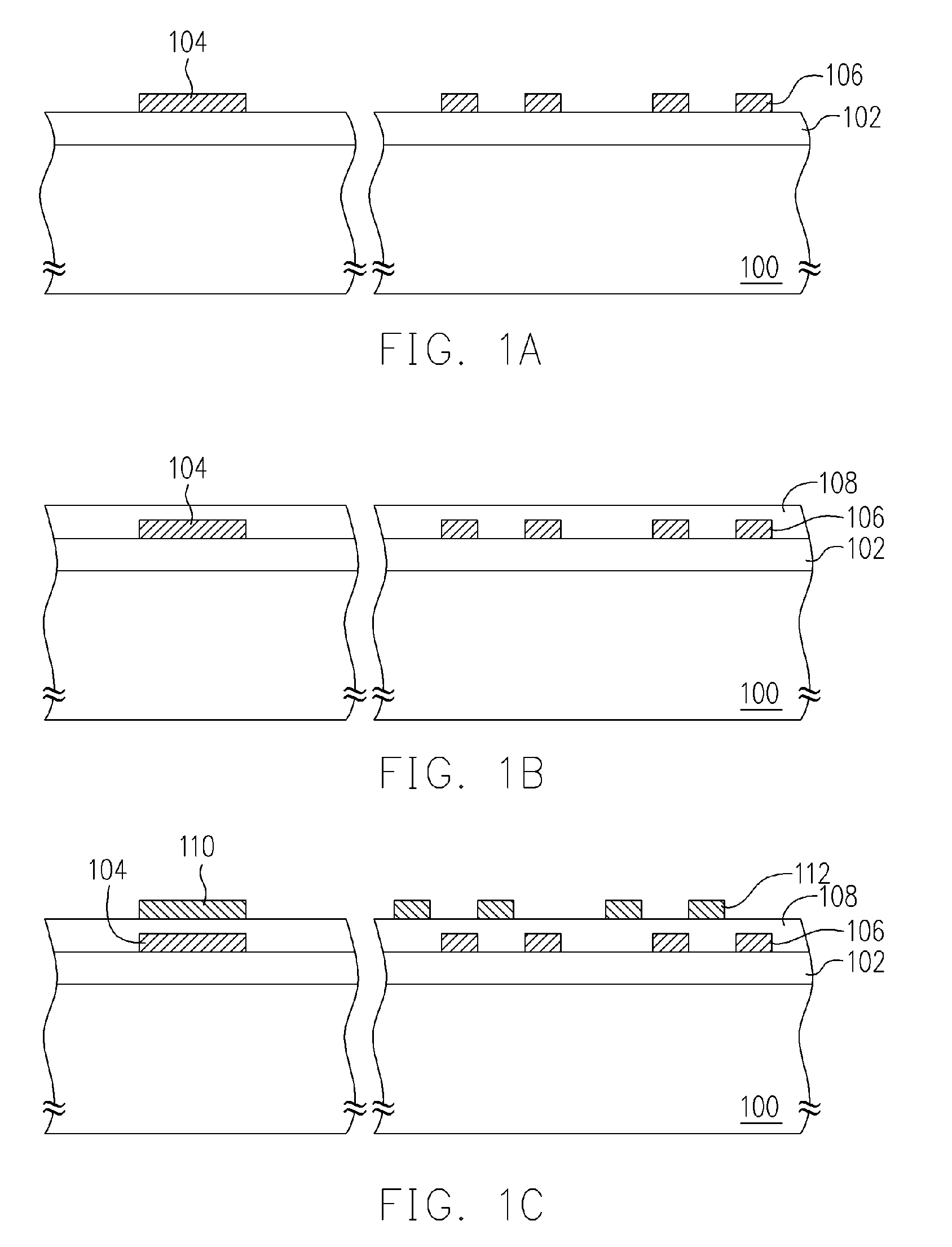

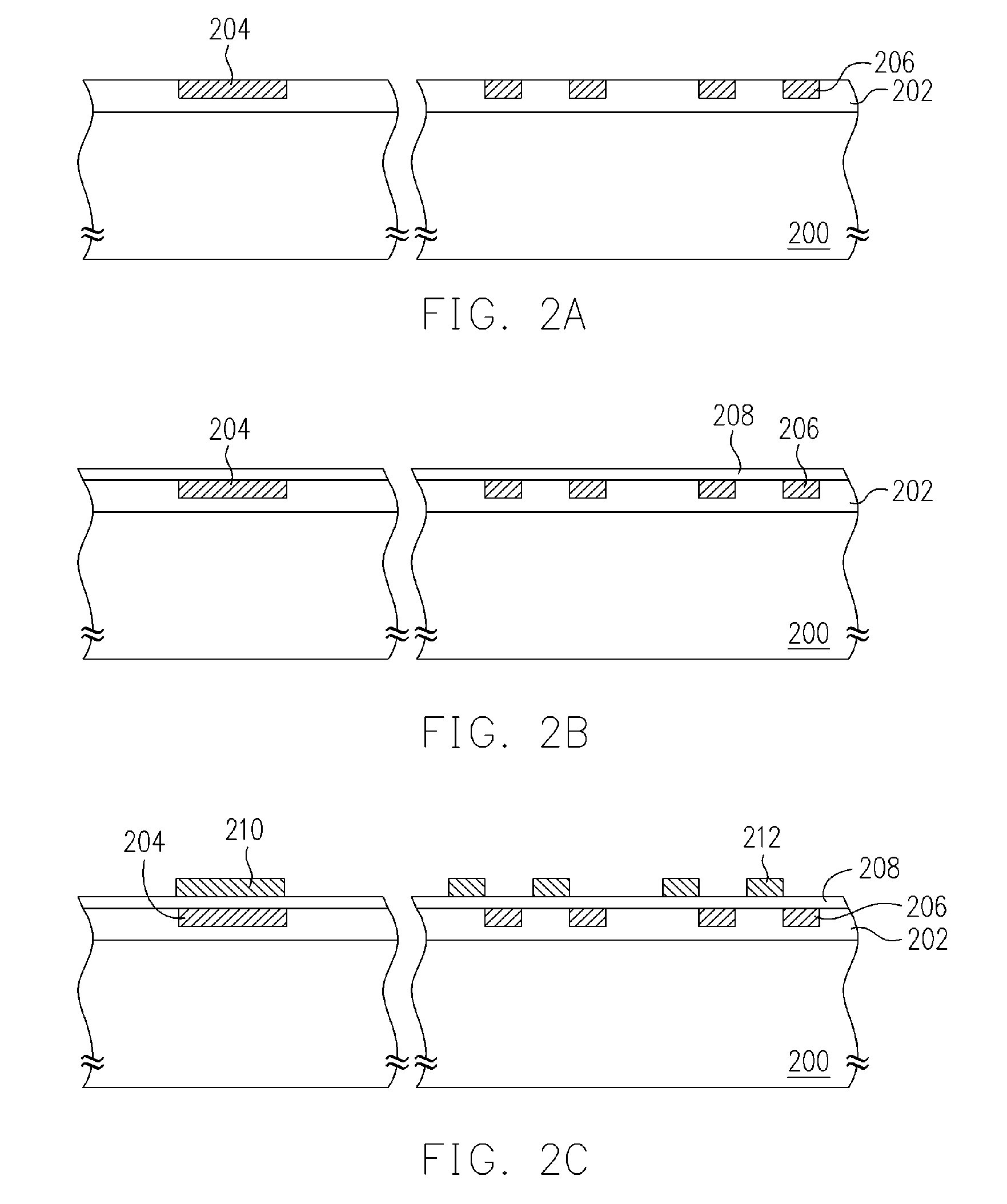

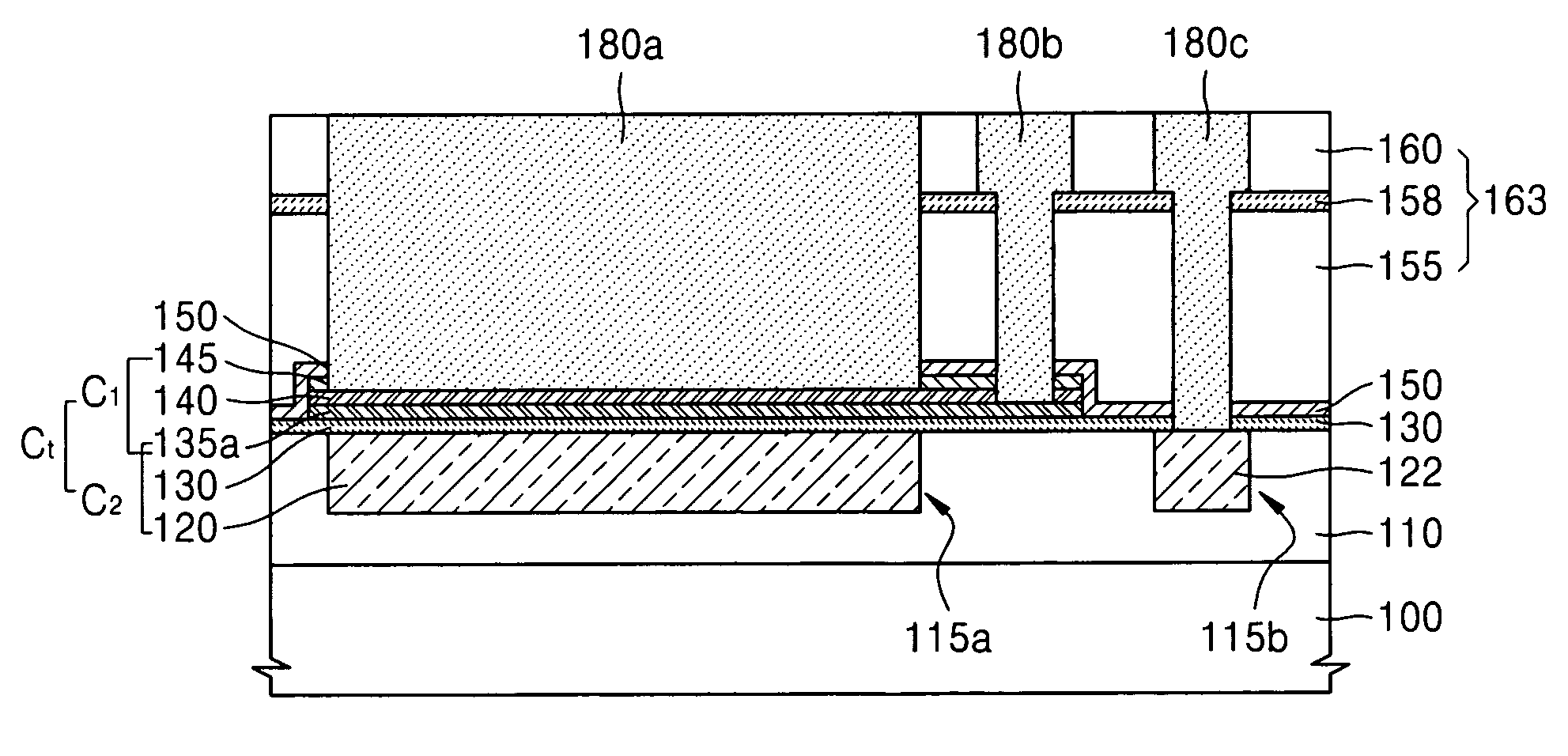

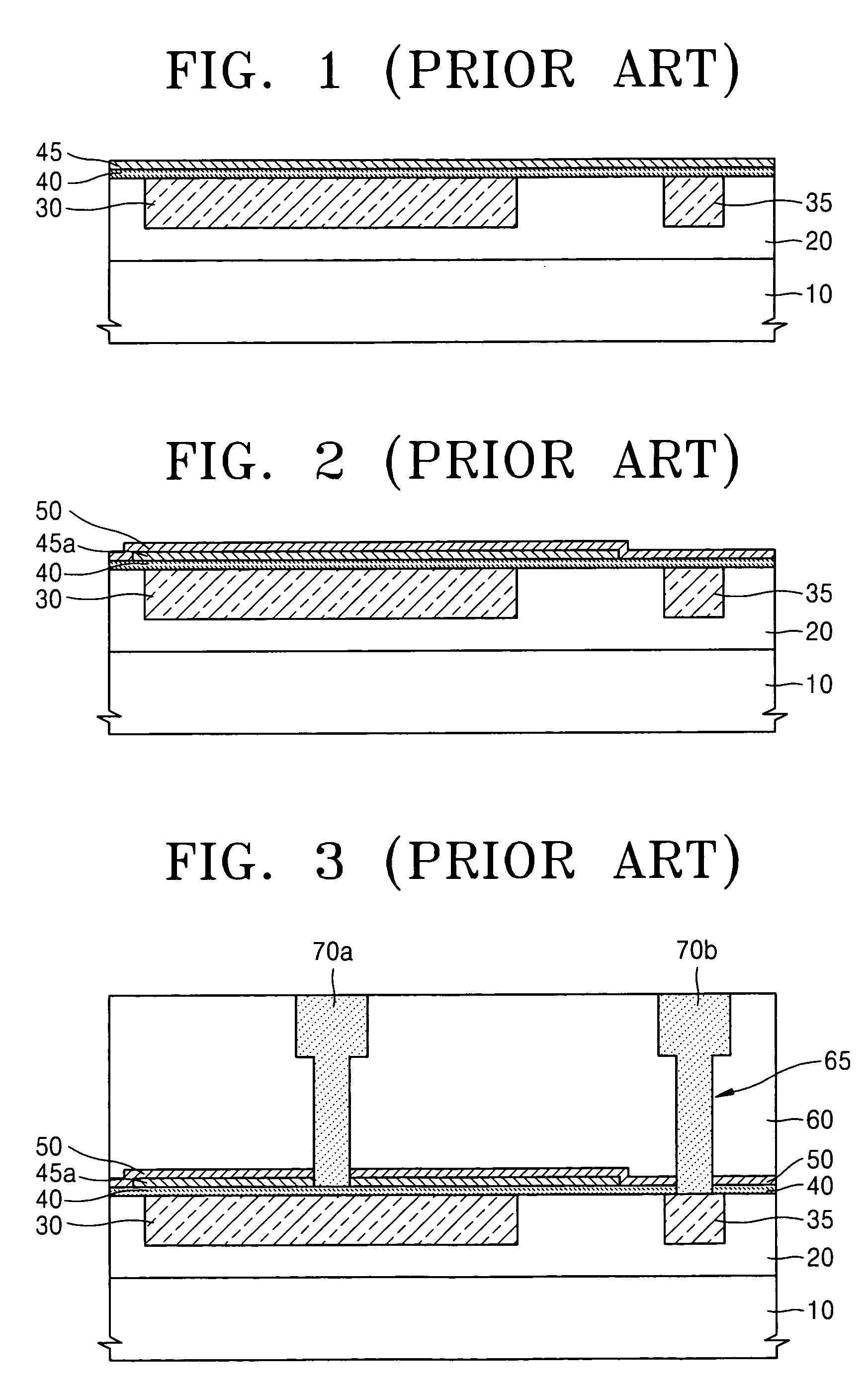

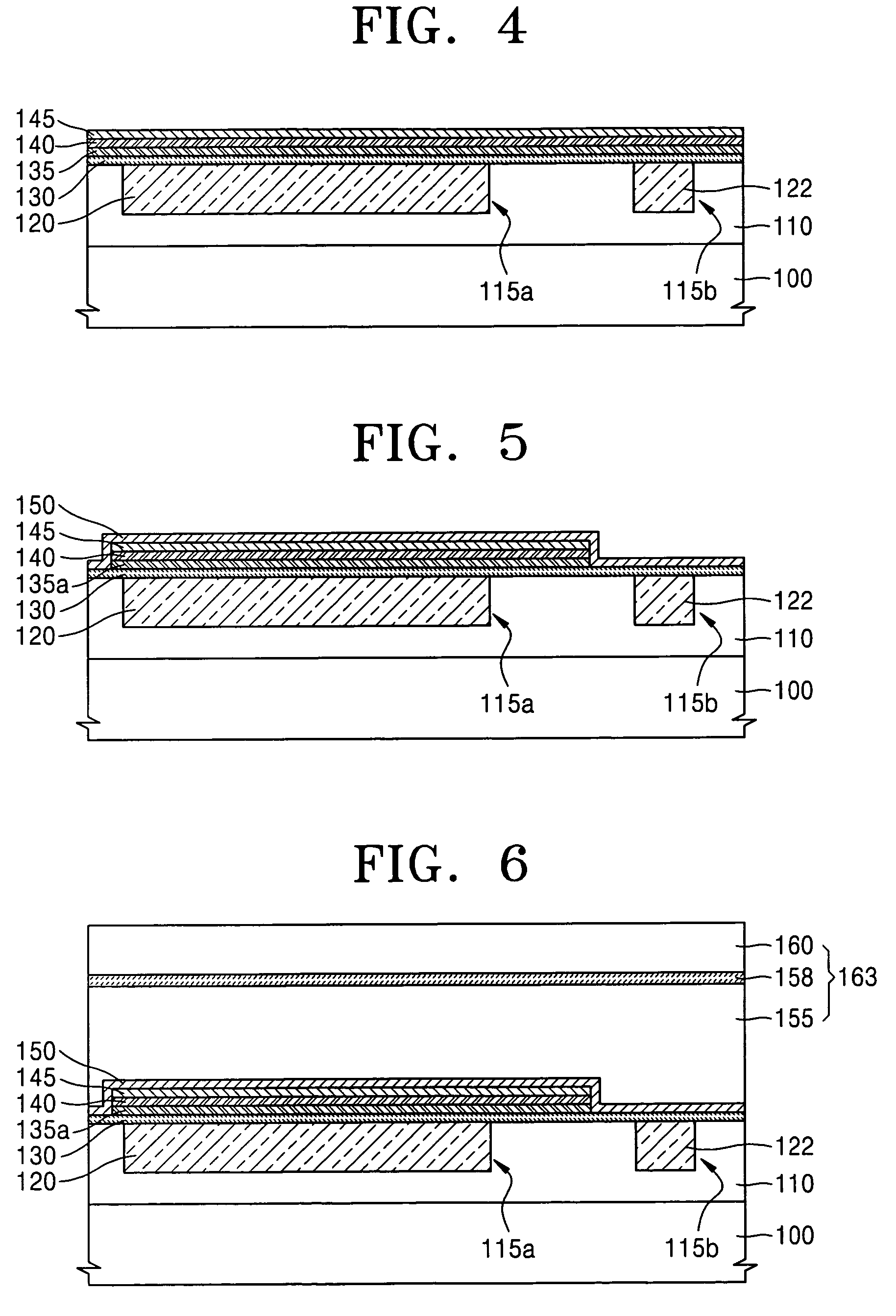

Metal-insulator-metal capacitors and methods of forming the same

InactiveUS20060183280A1Simple processSimplify the manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalSemiconductor

There are provided metal-insulator-metal (MIM) capacitors and methods of forming the same. The capacitors and the formation methods thereof provide a way of simplifying semiconductor fabrication processes, using component elements of the capacitor and insulating layers around the capacitor. To this end, lower and upper electrodes are sequentially stacked on a semiconductor substrate. A dielectric layer pattern is interposed between the upper and lower electrodes. An etch stop layer pattern and an etch buffer layer are disposed on the upper electrode and under the lower electrode, respectively. The upper and lower electrodes are disposed to expose the dielectric layer pattern and the etch buffer layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Implementing physically unclonable function (PUF) utilizing EDRAM memory cell capacitance variation

Owner:MARVELL ASIA PTE LTD

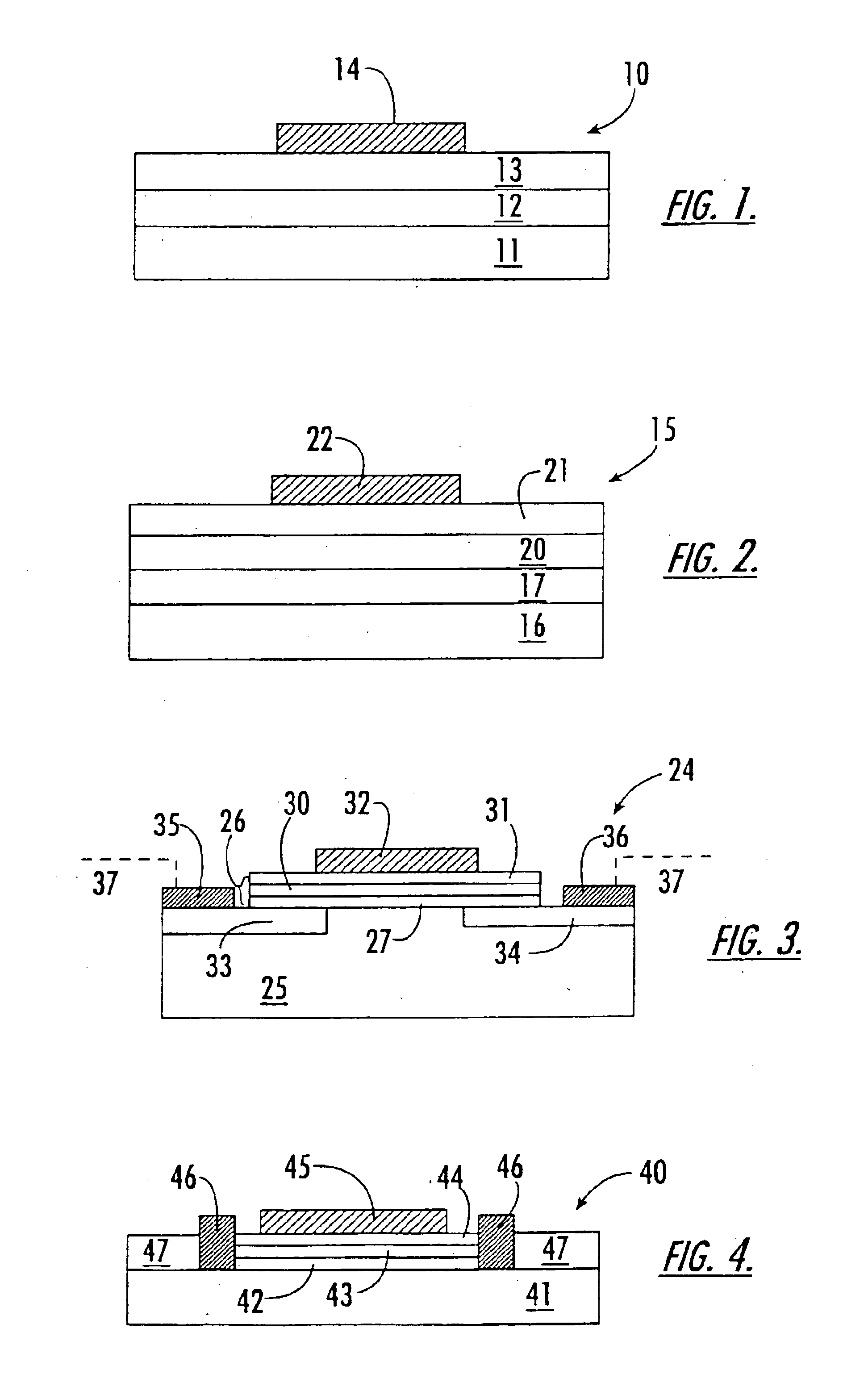

Method of making a metal-insulator-metal capacitor in the CMOS process

InactiveUS7294544B1Low resistivityTransistorSemiconductor/solid-state device detailsSemiconductorMetal

A method for fabricating an improved metal-insulator-metal capacitor is achieved. An insulating layer is provided overlying conducting lines on a semiconductor substrate. Via openings through the insulating layer to the conducting lines are filled with metal plugs. A first metal layer is deposited overlying the insulating layer and the metal plugs. A capacitor dielectric layer is deposited overlying the first metal layer wherein capacitor dielectric layer is deposited as a dual layer, each layer deposited within a separate chamber whereby pinholes are eliminated. A second metal layer and a barrier metal layer are deposited overlying the capacitor dielectric layer. The second metal layer and the barrier metal layer are patterned to form a top plate electrode. Thereafter, the capacitor dielectric layer and the first metal layer are patterned to form a bottom plate electrode completing fabrication of a metal-insulator-metal capacitor.

Owner:TAIWAN SEMICON MFG CO LTD

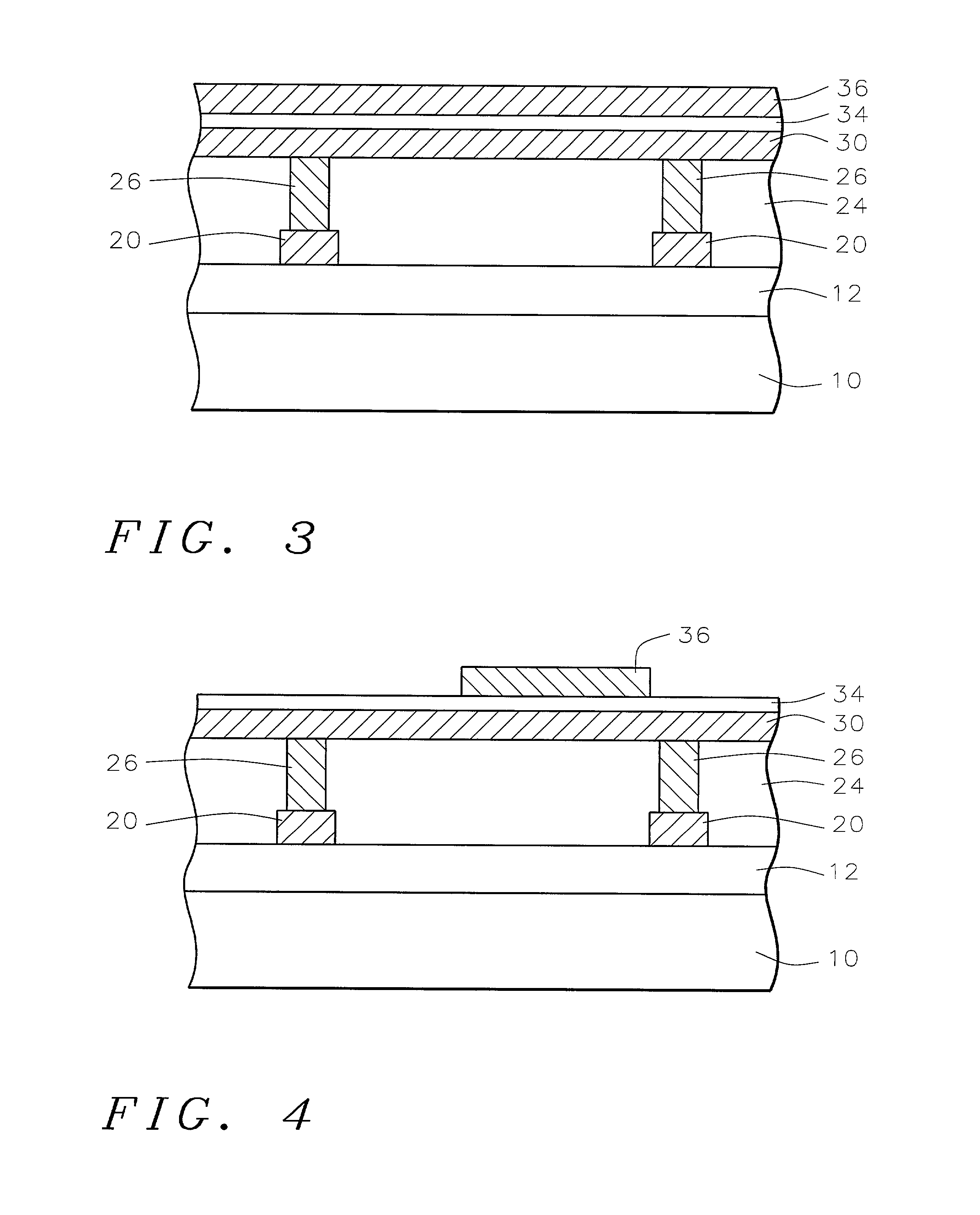

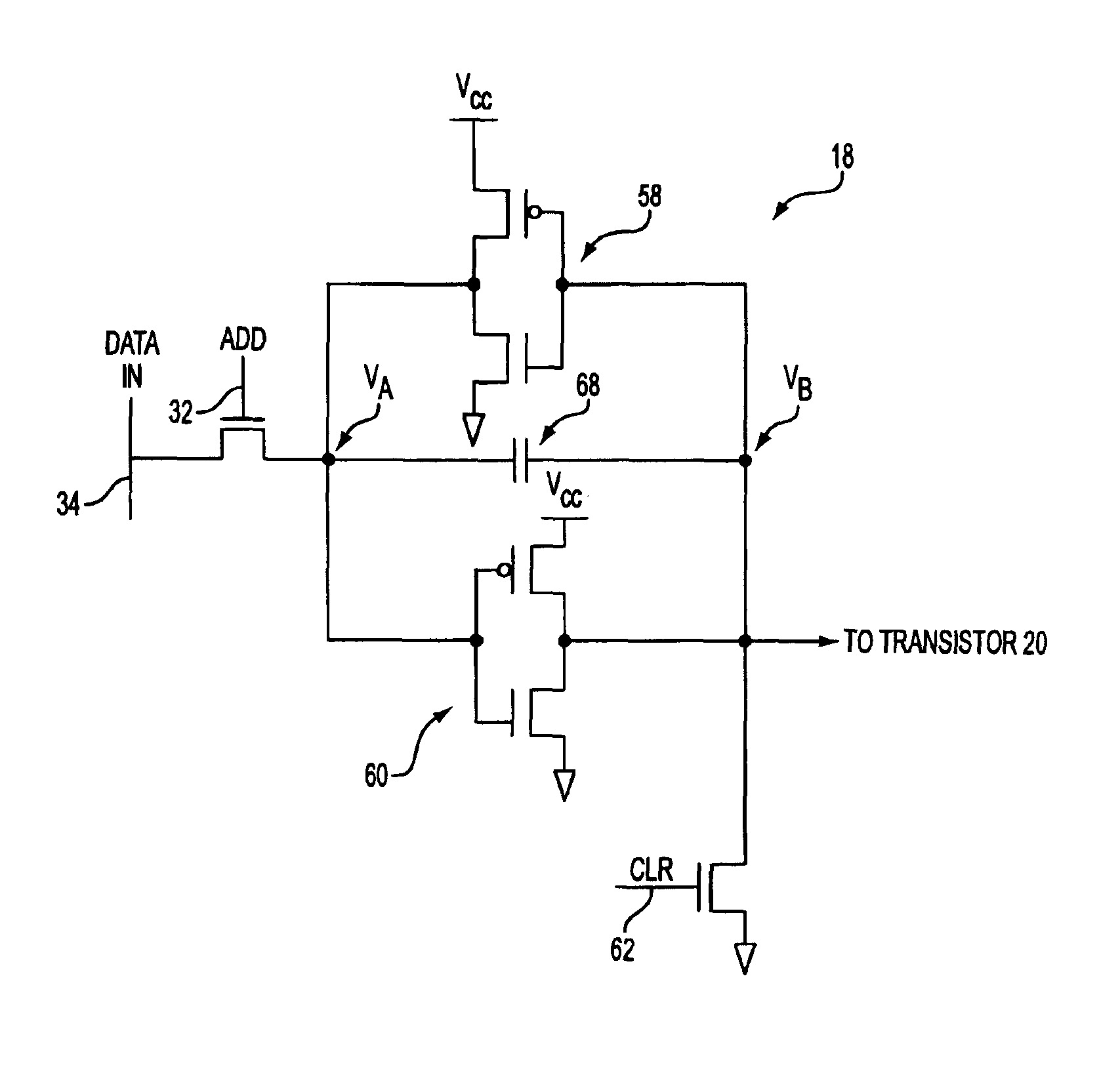

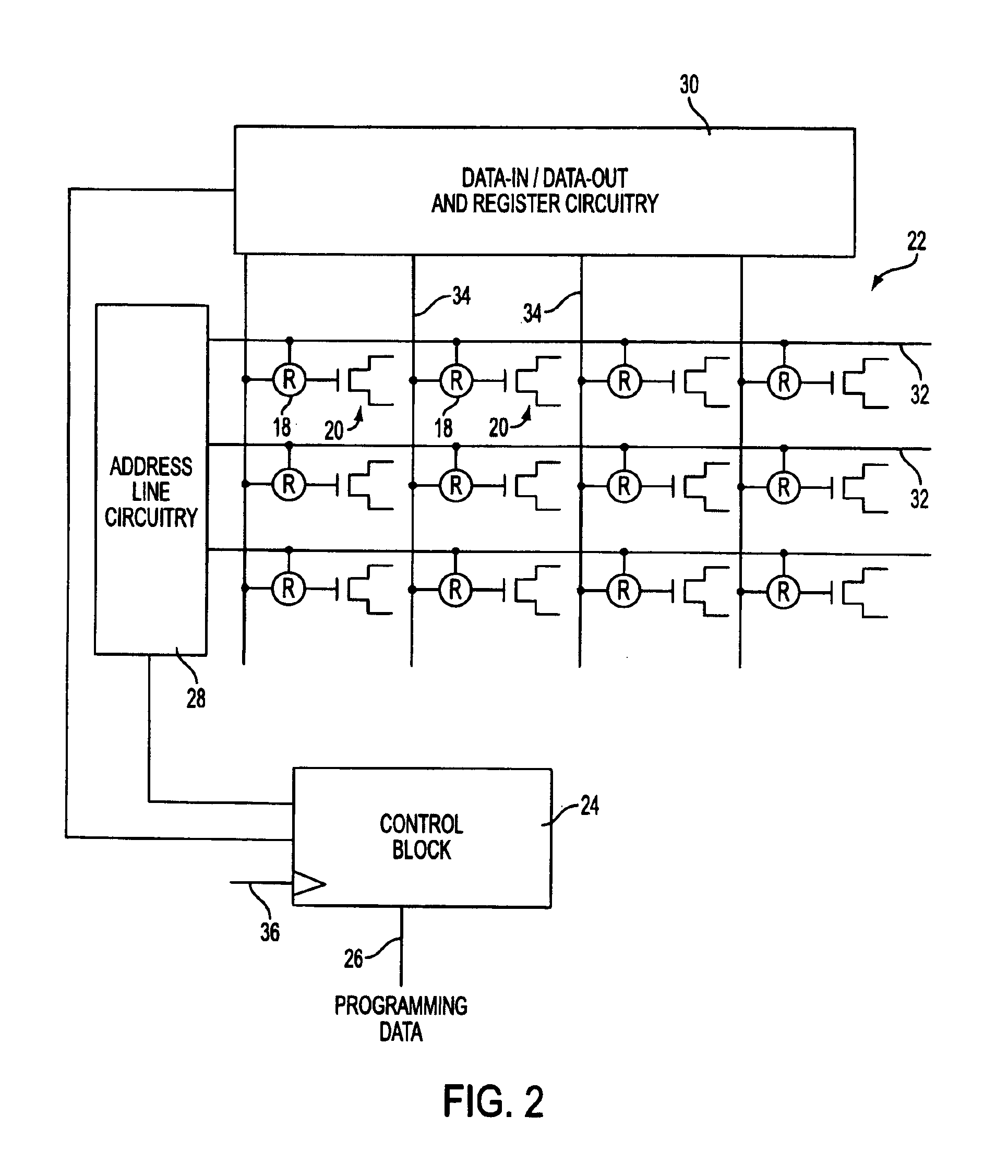

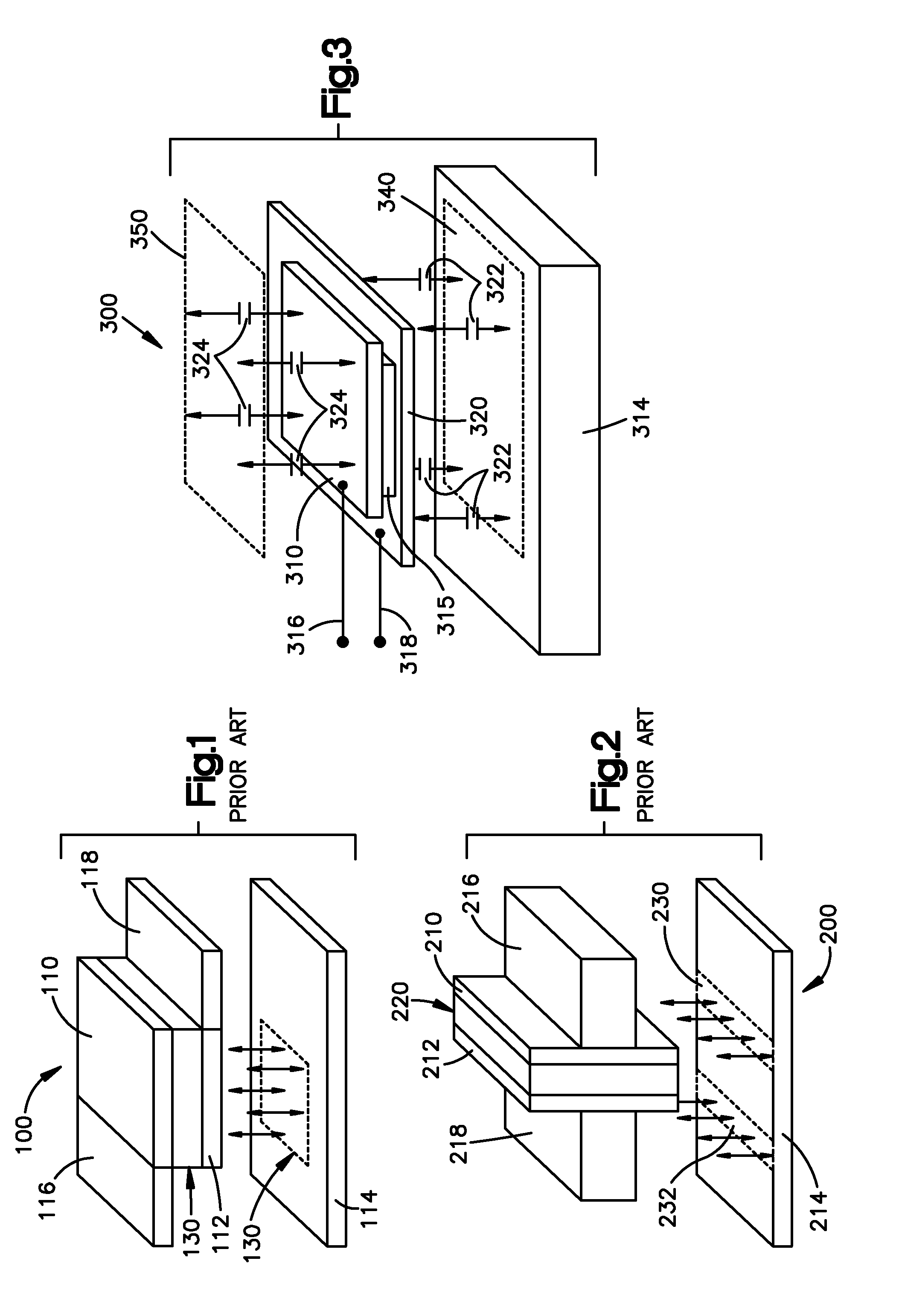

Programmable logic devices with stabilized configuration cells for reduced soft error rates

InactiveUS6876572B2Improved soft error rate performanceReduce the impactSolid-state devicesSemiconductor/solid-state device manufacturingProgrammable logic deviceEngineering

Programmable logic devices are provided having configuration memory cells that exhibit decreased soft error rates. A stabilizing capacitor may be connected between each of the memory cell's input and output terminals. The capacitor may be a metal-insulator-metal capacitor formed using a vertical structure, a horizontal structure, or a hybrid vertical-horizontal structure. The memory cell may have inverter transistors of increased strength to help stabilize the memory cell.

Owner:ALTERA CORP

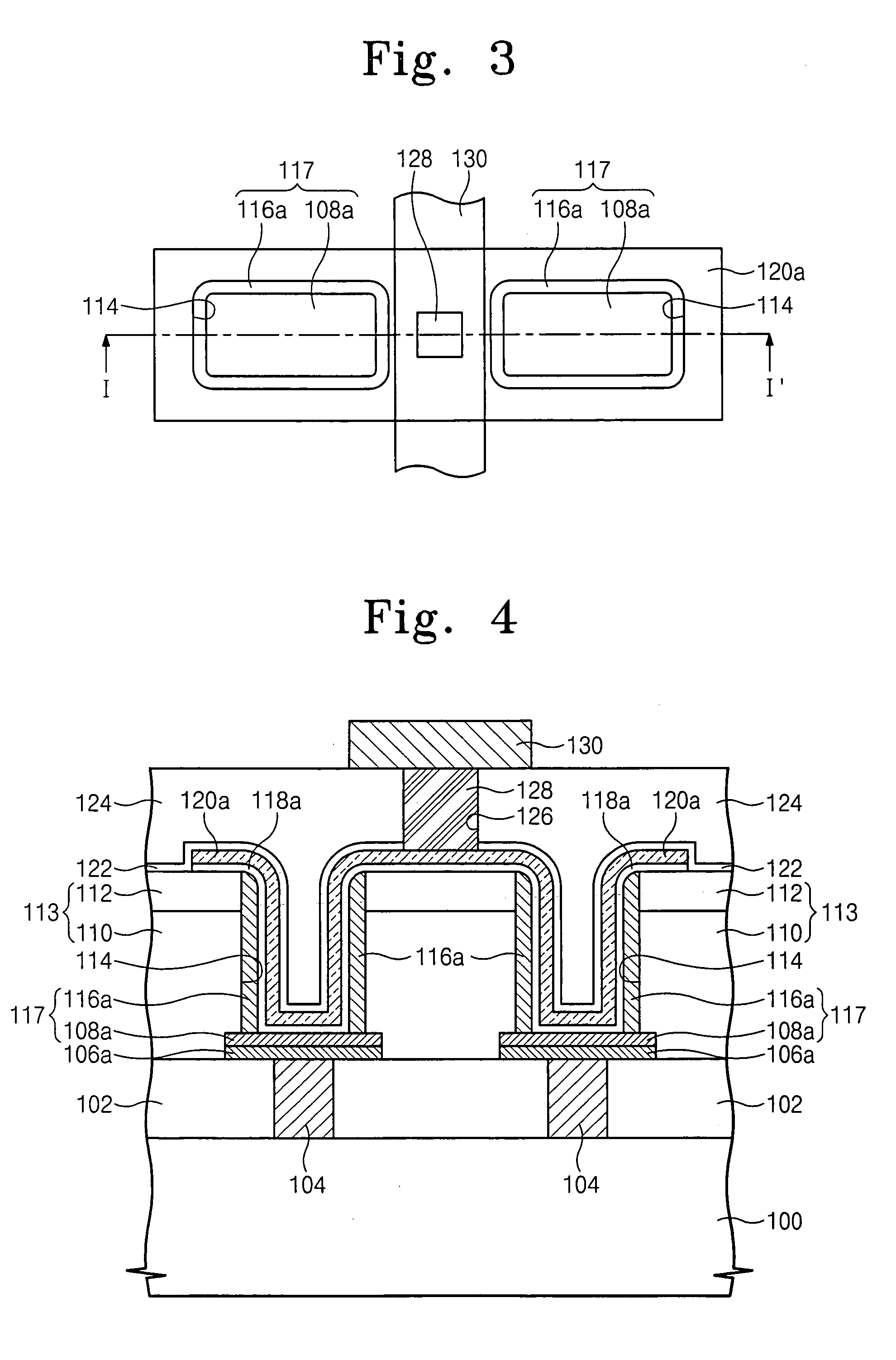

Semiconductor devices having a metal-insulator-metal capacitor and methods of forming the same

A semiconductor device having an MIM capacitor and a method of forming the same are provided. A lower electrode includes a plate electrode and a sidewall electrode. The plate electrode is formed by a patterning process preferably including a plasma anisotropic etching. The sidewall electrode is formed like a spacer on an inner sidewall of an opening exposing the plate electrode by a plasma entire surface anisotropic etching.

Owner:SAMSUNG ELECTRONICS CO LTD

Metal-insulator-metal transformer and method for manufacturing the same

ActiveUS7365627B2Save areaReduce spacingSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsMetal-insulator-metalTransformer

The invention is directed to a method for manufacturing a metal-insulator-metal transformer together with a capacitor. The method comprises steps of providing a substrate having at least a dielectric layer formed thereon and then forming a first metal layer of the metal-insulator-metal capacitor together with a first metal coil of the transformer over the substrate. An insulating layer is formed to cover the substrate, the first metal layer and the first metal coil. A second metal layer of the metal-insulator-metal capacitor is formed together with a second metal coil of the transformer on the insulating layer.

Owner:UNITED MICROELECTRONICS CORP

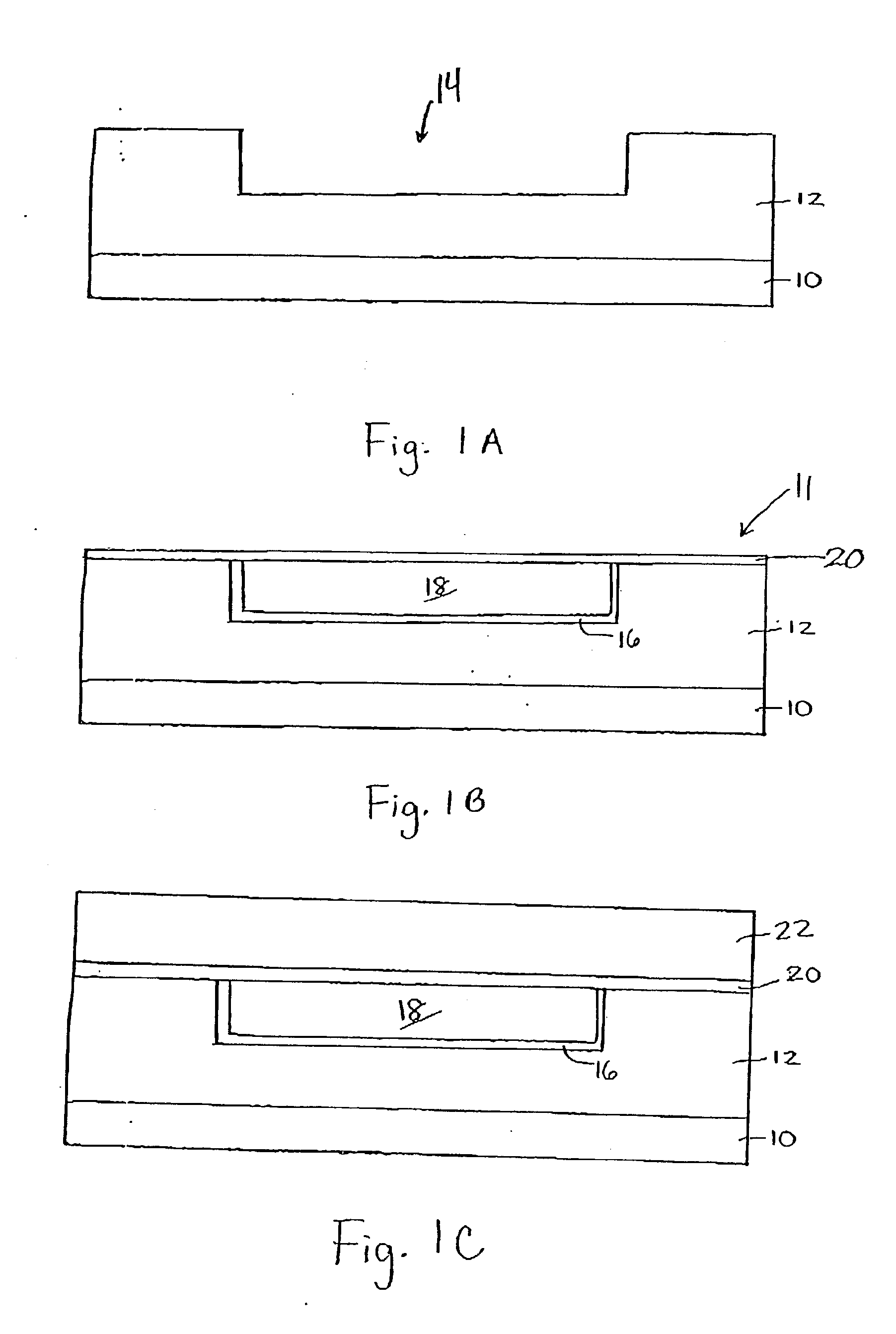

Metal-insulator-metal capacitor and method of fabrication

InactiveUS20050067701A1Semiconductor/solid-state device detailsSolid-state devicesCopperDiffusion barrier

A method and structure for a MIM capacitor, the structure including: an electronic device, comprising: an interlevel dielectric layer formed on a semiconductor substrate; a copper bottom electrode formed in the interlevel dielectric layer, a top surface of the bottom electrode co-planer with a top surface of the interlevel dielectric layer; a conductive diffusion barrier in direct contact with the top surface of the bottom electrode; a MIM dielectric in direct contact with a top surface of the conductive diffusion barrier; and a top electrode in direct contact with a top surface of the MIM dielectric. The conductive diffusion barrier may be recessed into the copper bottom electrode or an additional recessed conductive diffusion barrier provided. Compatible resistor and alignment mark structures are also disclosed.

Owner:GLOBALFOUNDRIES US INC

Metal-insulator-metal capacitor and method of fabrication

A method and structure for a MIM capacitor, the structure including: an electronic device, comprising: an interlevel dielectric layer formed on a semiconductor substrate; a copper bottom electrode formed in the interlevel dielectric layer, a top surface of the bottom electrode co-planer with a top surface of the interlevel dielectric layer; a conductive diffusion barrier in direct contact with the top surface of the bottom electrode; a MIM dielectric in direct contact with a top surface of the conductive diffusion barrier; and a top electrode in direct contact with a top surface of the MIM dielectric. The conductive diffusion barrier may be recessed into the copper bottom electrode or an additional recessed conductive diffusion barrier provided. Compatible resistor and alignment mark structures are also disclosed.

Owner:GLOBALFOUNDRIES U S INC

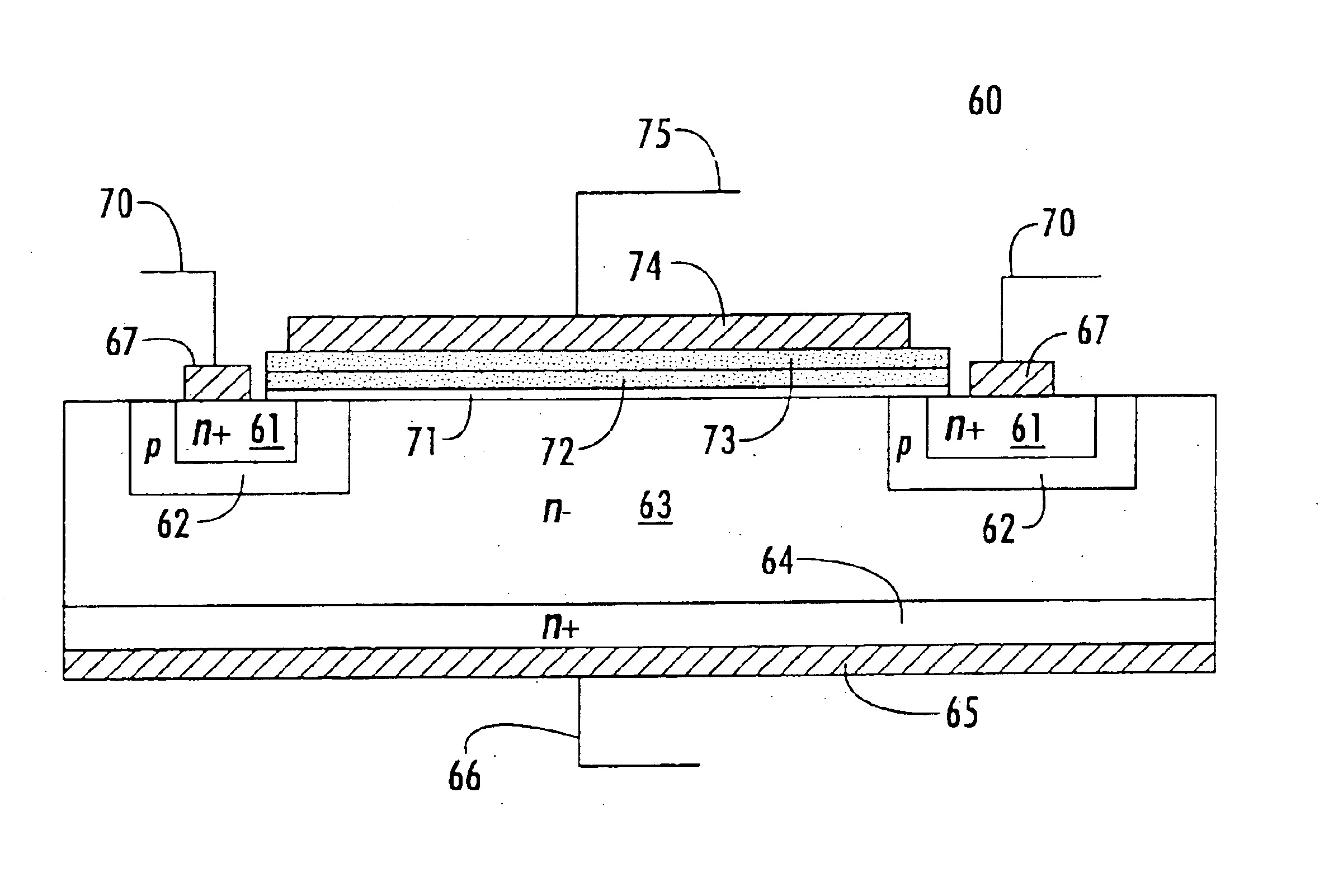

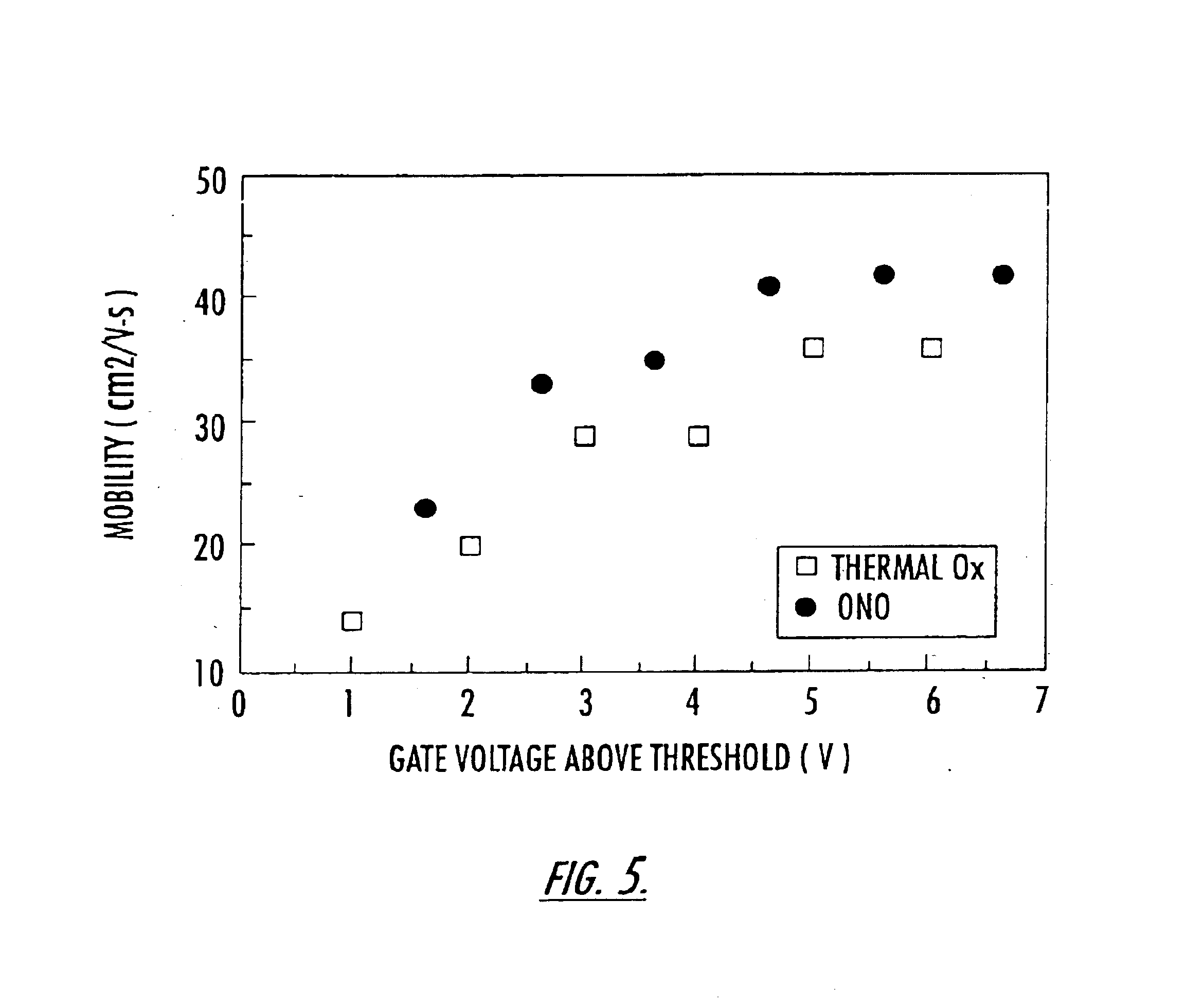

High voltage, high temperature capacitor and interconnection structures

InactiveUS6972436B2High mean time to failureTransistorThin/thick film capacitorInterconnectionHigh pressure

Capacitors and interconnection structures for silicon carbide are provided having an oxide layer, a layer of dielectric material and a second oxide layer on the layer of dielectric material. The thickness of the oxide layers may be from about 0.5 to about 33 percent of the thickness of the oxide layers and the layer of dielectric material. Capacitors and interconnection structures for silicon carbide having silicon oxynitride layer as a dielectric structure are also provided. Such a dielectric structure may be between metal layers to provide a metal-insulator-metal capacitor or may be used as a inter-metal dielectric of an interconnect structure so as to provide devices and structures having improved mean time to failure. Methods of fabricating such capacitors and structures are also provided.

Owner:CREE INC

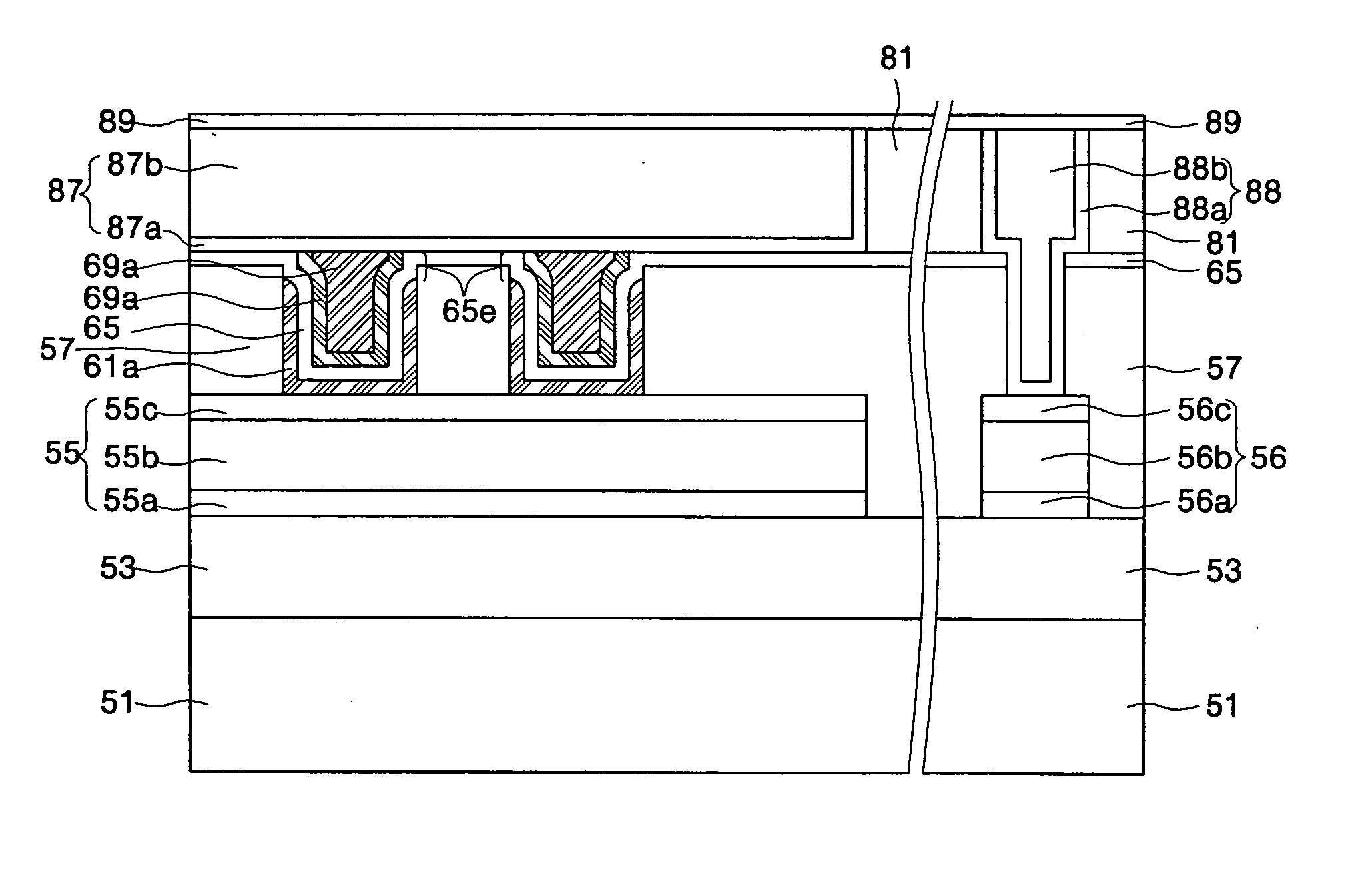

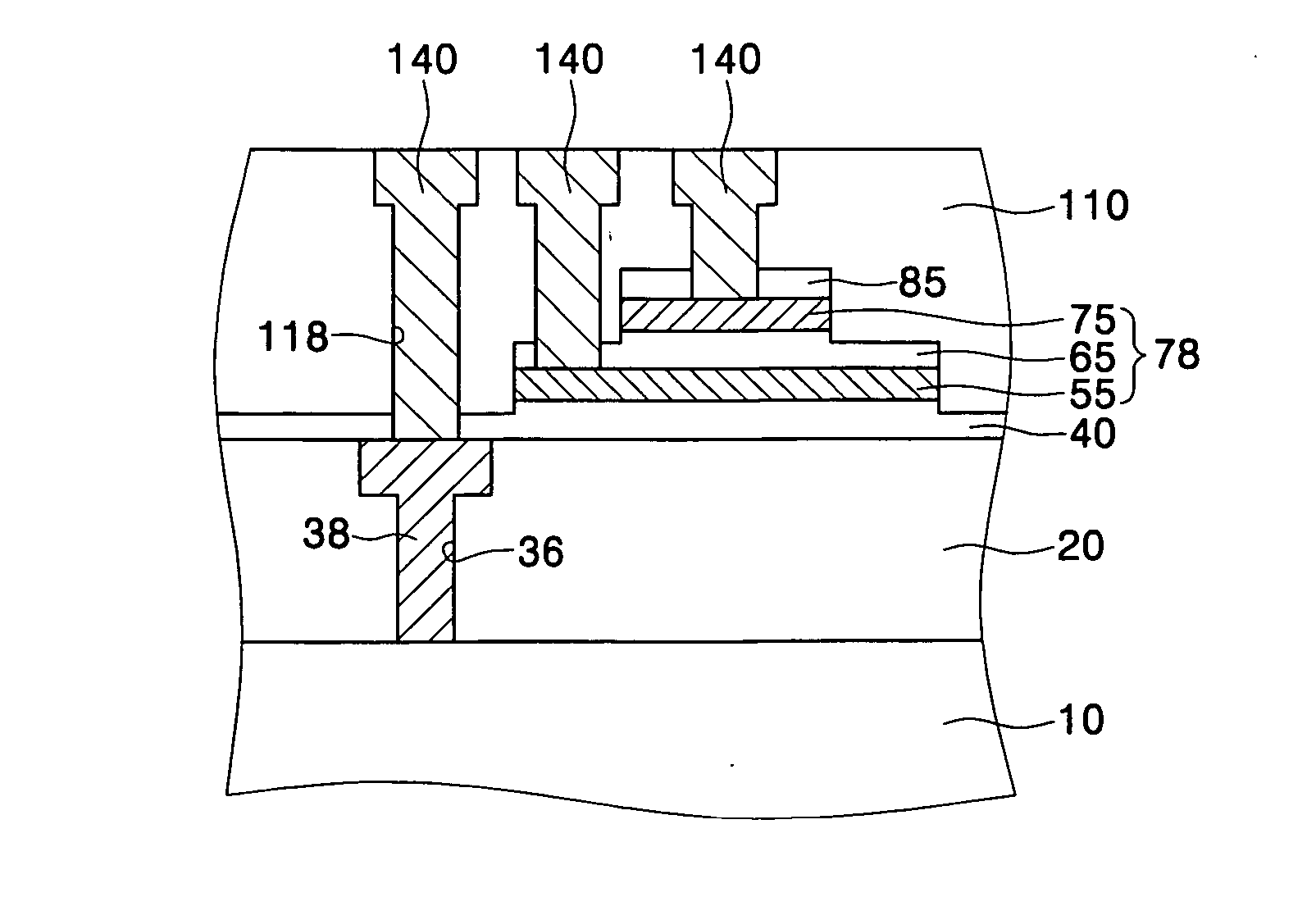

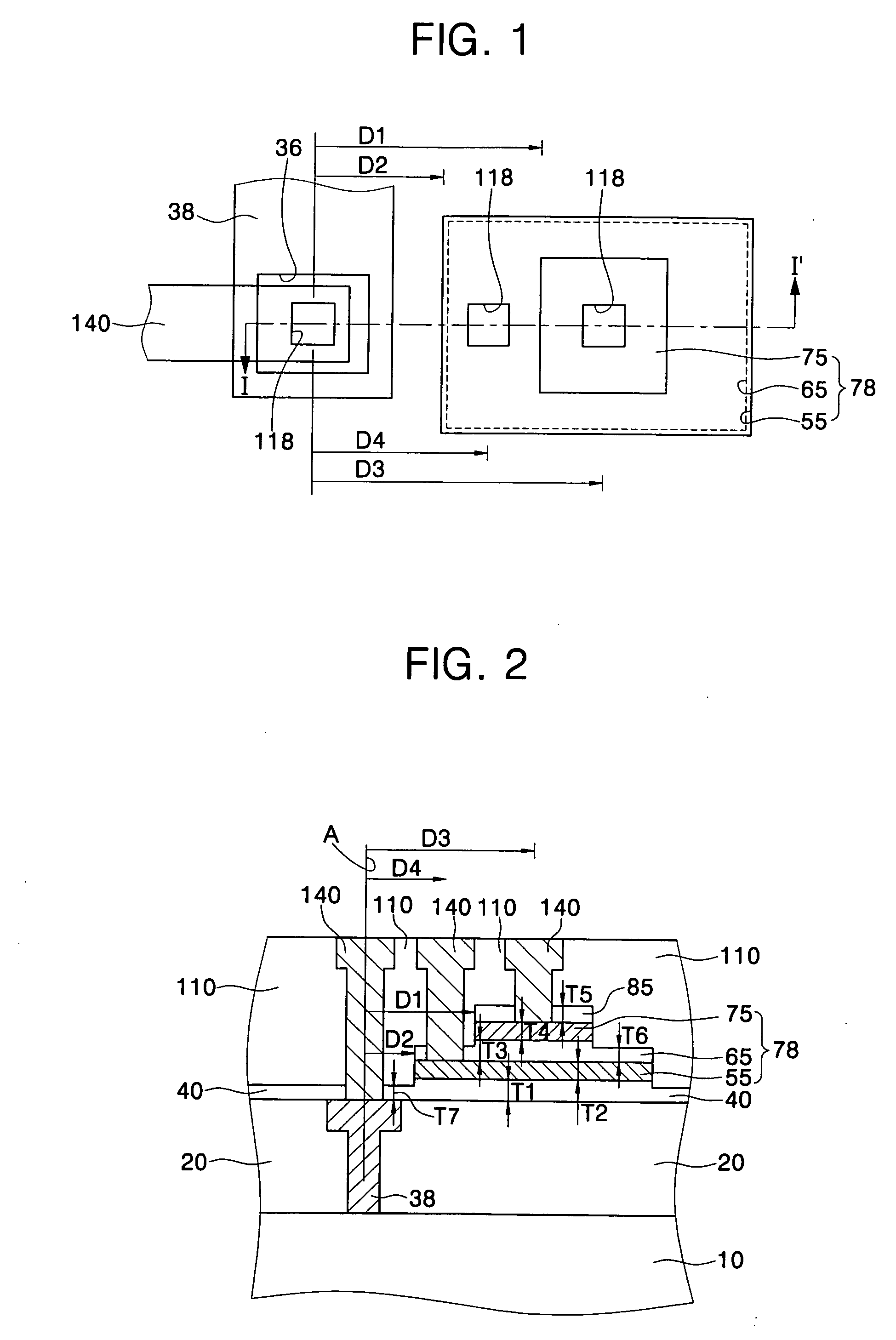

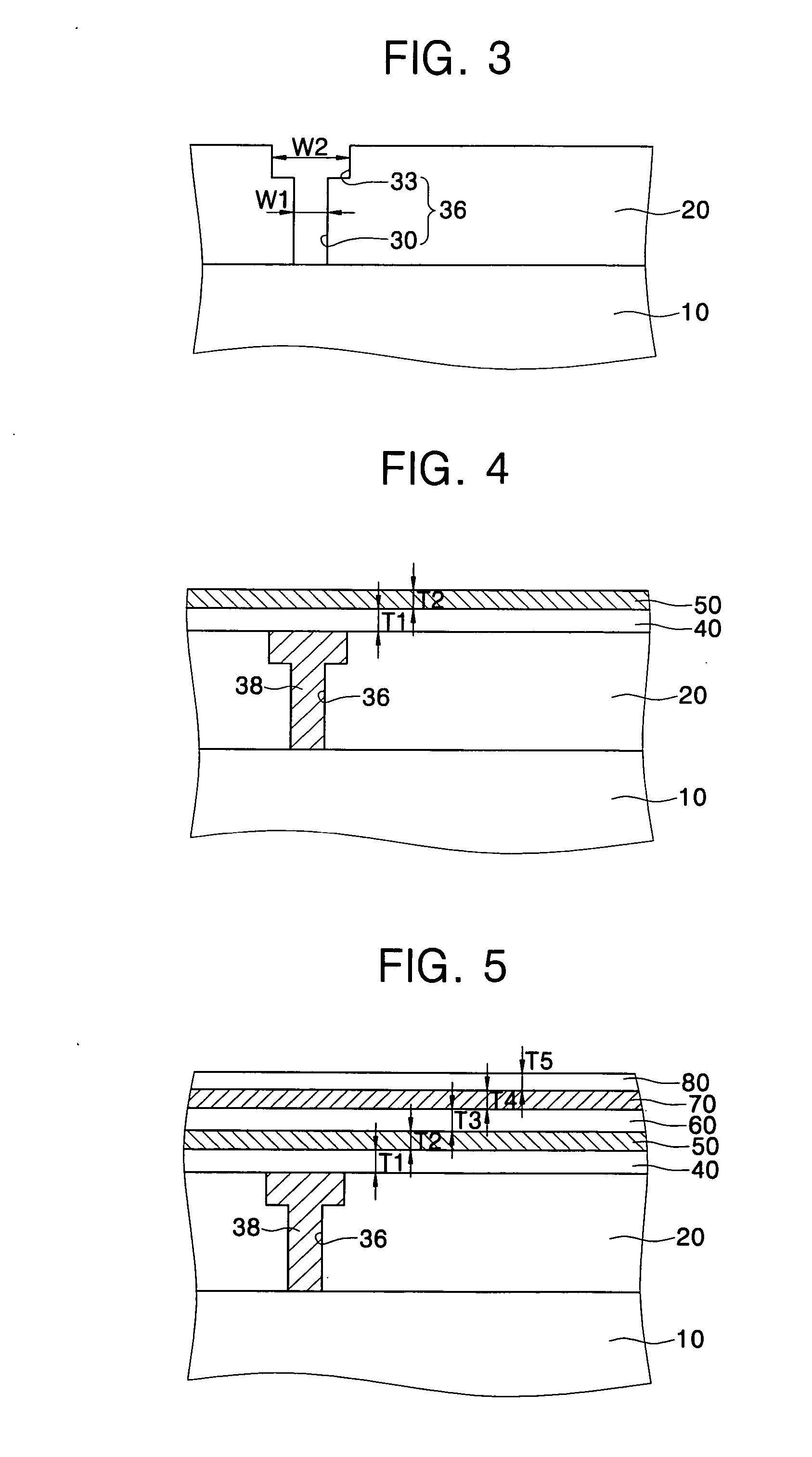

Metal-insulator-metal capacitor and method of manufacturing the same

ActiveUS20080050874A1Highly integratedIncrease capacityTransistorSemiconductor/solid-state device detailsEngineeringElectrode

A metal-insulator-metal capacitor includes a first electrode in a first wiring level, a second electrode above the first wiring level and extending into a first portion of the first electrode that surrounds the second electrode, and a dielectric film separating the first electrode from the second electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

Single lithography-step planar metal-insulator-metal capacitor and resistor

InactiveUS20070080426A1Semiconductor/solid-state device detailsSolid-state devicesDielectricLithographic artist

MIMCAP semiconductor devices and methods for fabrication MIMCAP semiconductor devices that include a grown capacitor dielectric are provided. Exemplary MIMCAP semiconductor devices can include a bottom electrode, a grown capacitor dielectric on the bottom electrode, and a top electrode on the capacitor dielectric. The grown layer can have a k-value greater than 1 and can be formed of, for example, an oxide or nitride that is chemically or thermally grown from the bottom electrode.

Owner:TEXAS INSTR INC

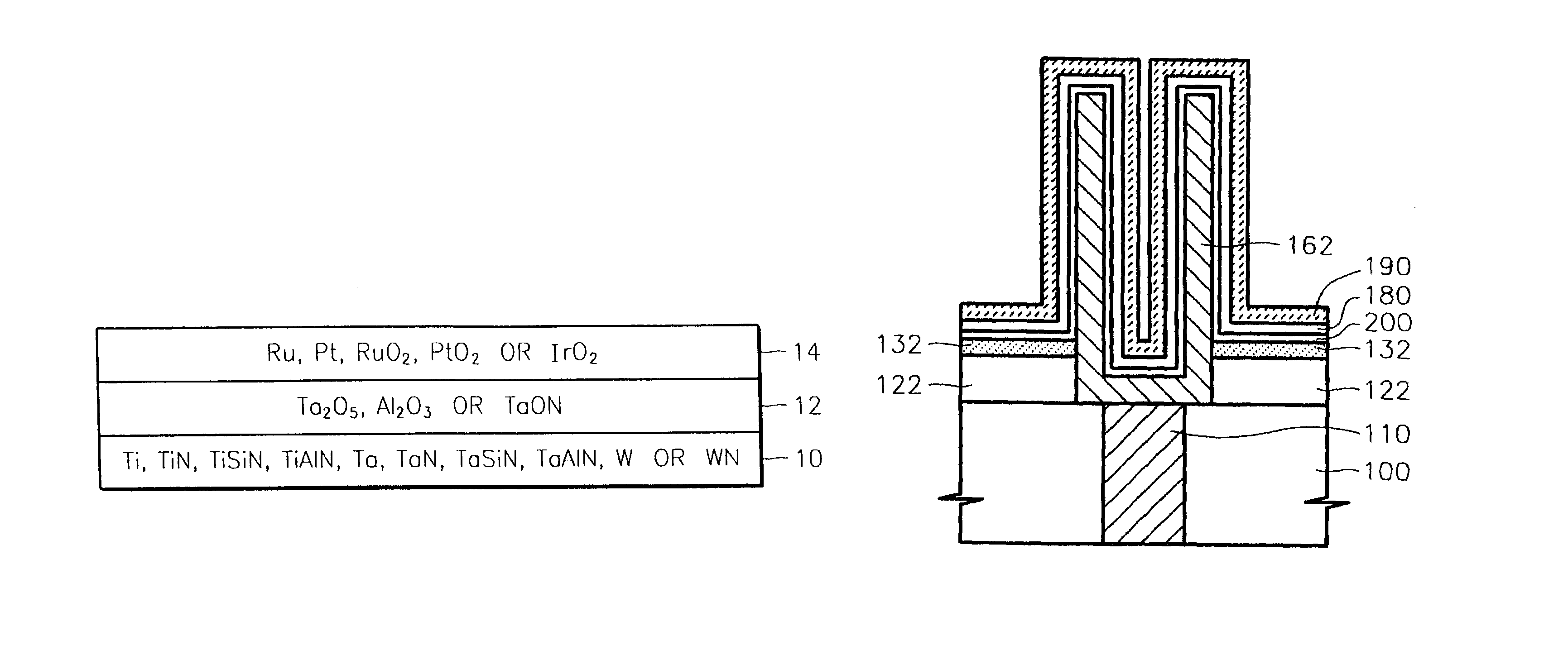

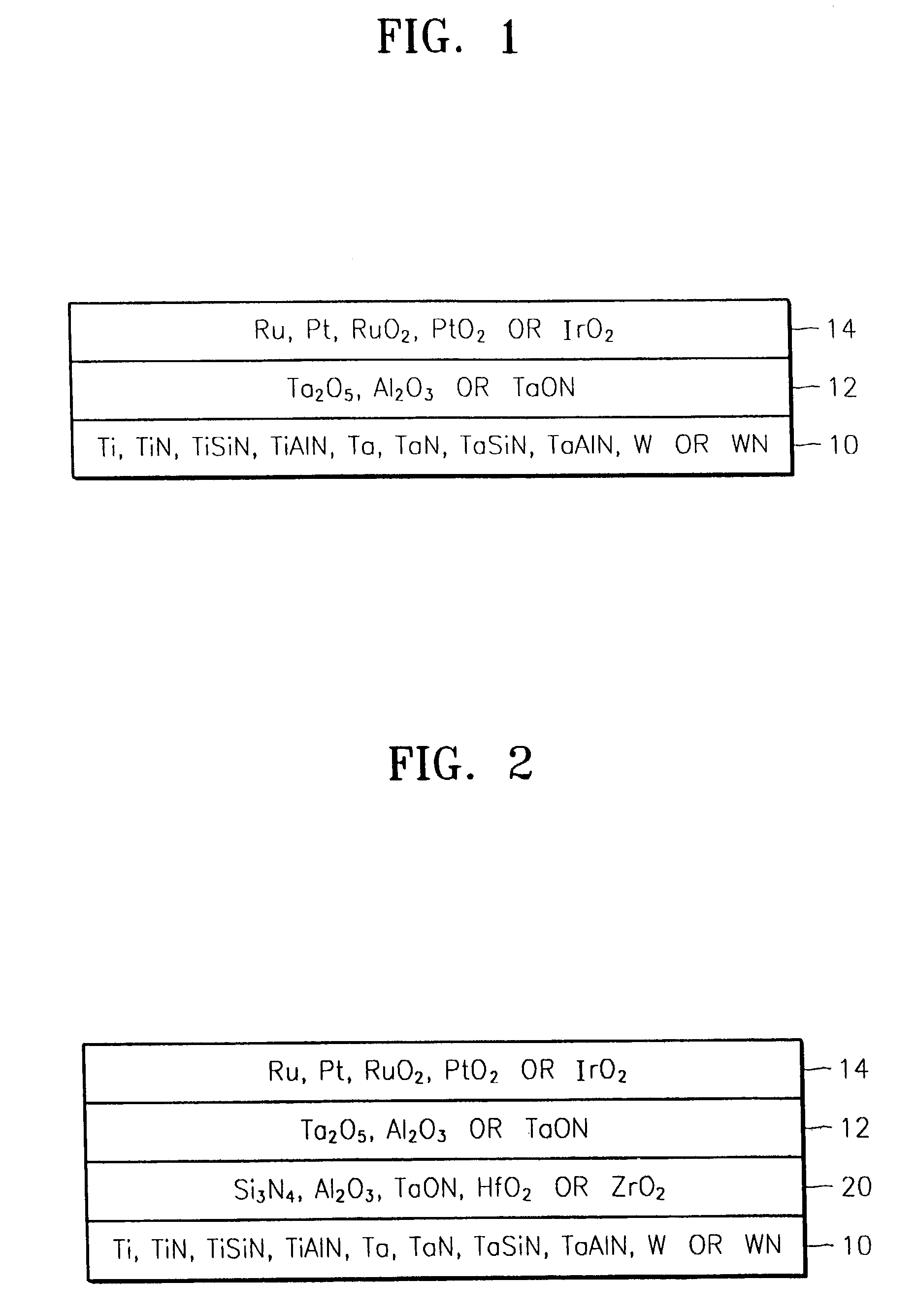

Method of forming a metal-insulator-metal capacitor

InactiveUS7018933B2Excellent electrical propertiesAvoid reactionTransistorSolid-state devicesMetal-insulator-metalPlatinum

A metal-insulator-metal (MIM) capacitor of a semiconductor device, and a manufacturing method thereof, includes a lower electrode formed of a refractory metal or a conductive compound including the refractory metal, a dielectric film formed of a high dielectric material, and an upper electrode formed of a platinum-family metal or a platinum-family metal oxide. Accordingly, the MIM capacitor satisfies the criteria of step coverage, electrical characteristics and manufacturing costs, as compared to a conventional MIM capacitor in which the upper and lower electrodes are formed of the same material such as a platinum-family metal, a refractory metal or a conductive compound including the refractory metal. The capacitor is especially suitable for mass production in semiconductor fabrication processes.

Owner:SAMSUNG ELECTRONICS CO LTD

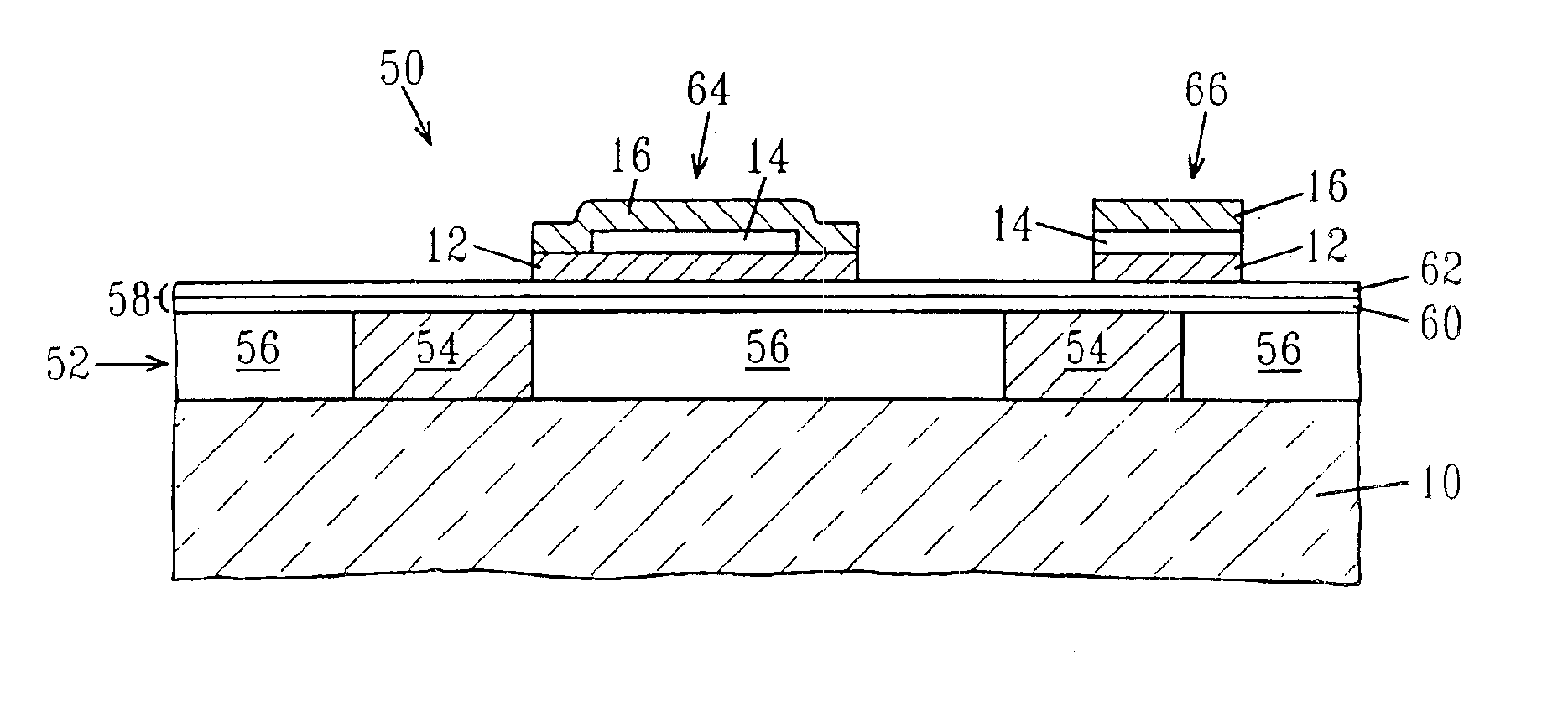

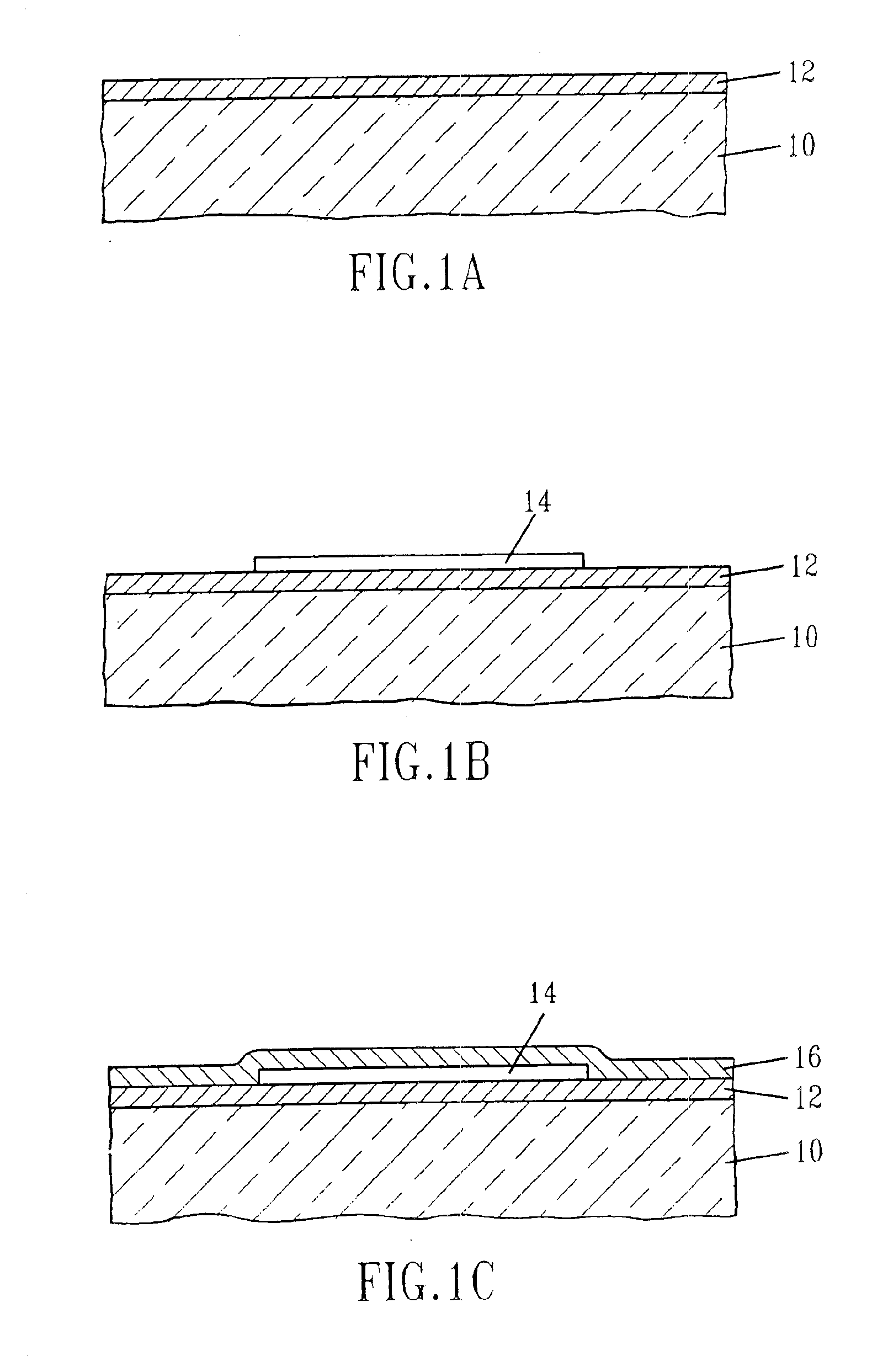

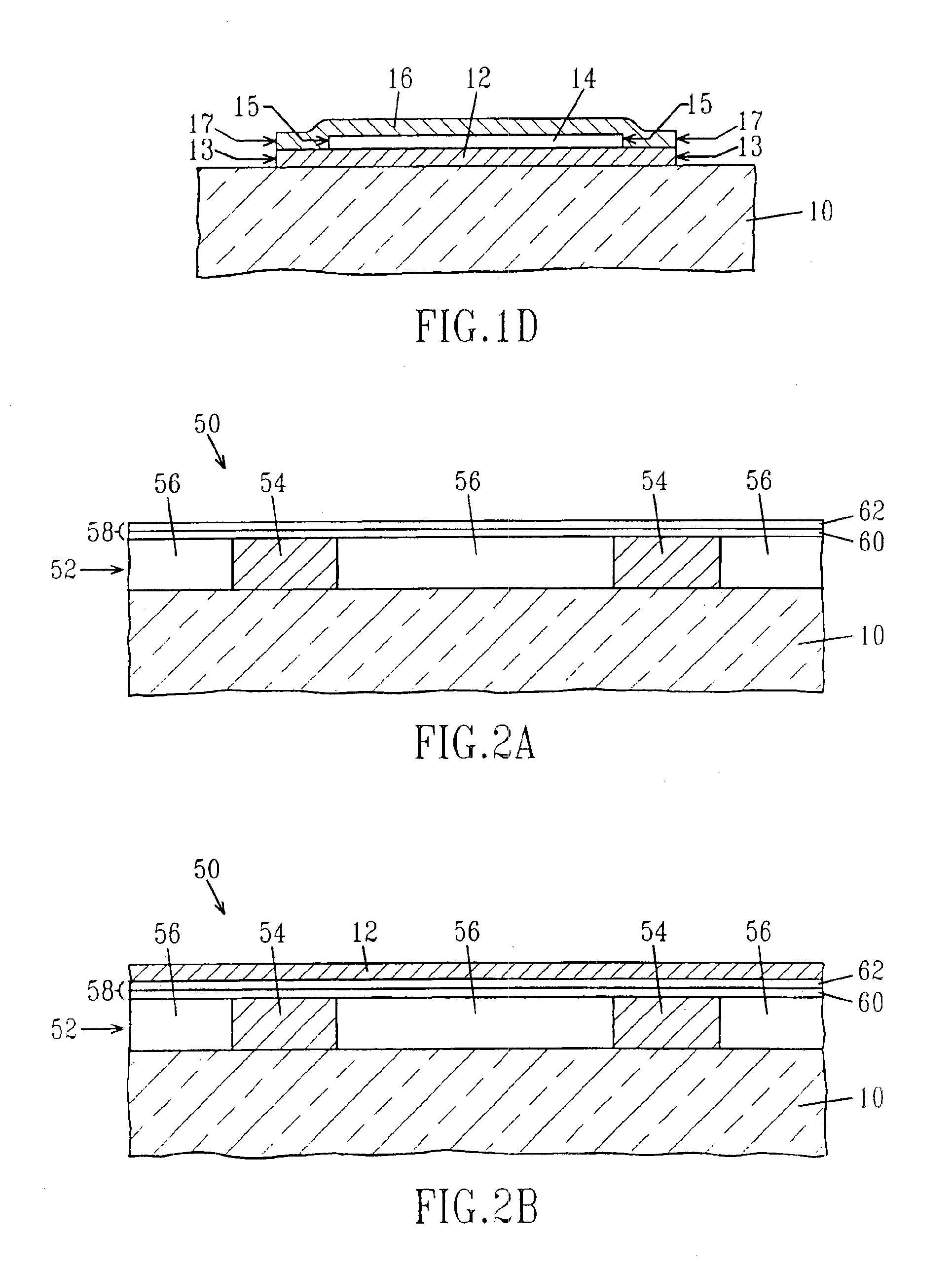

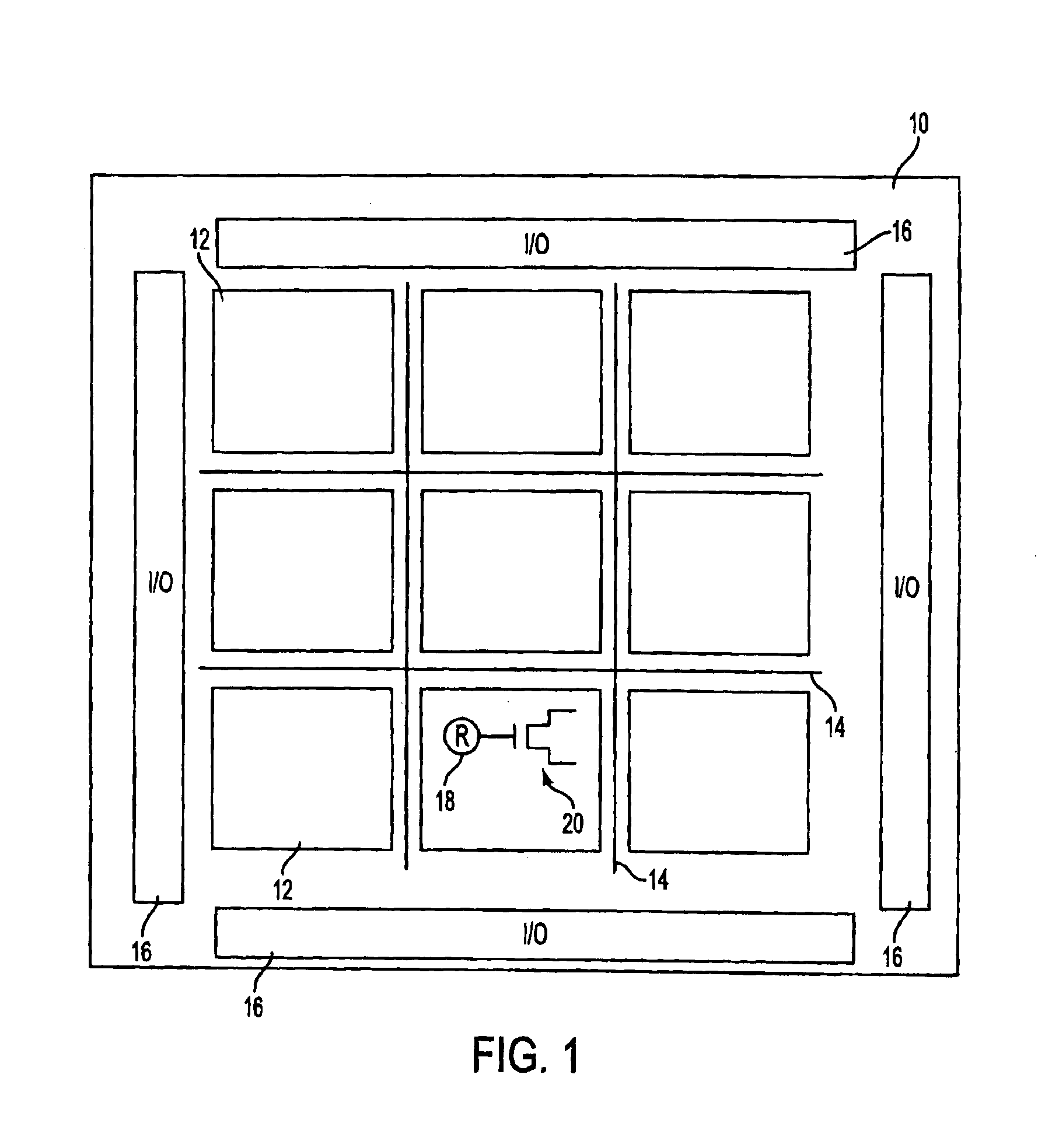

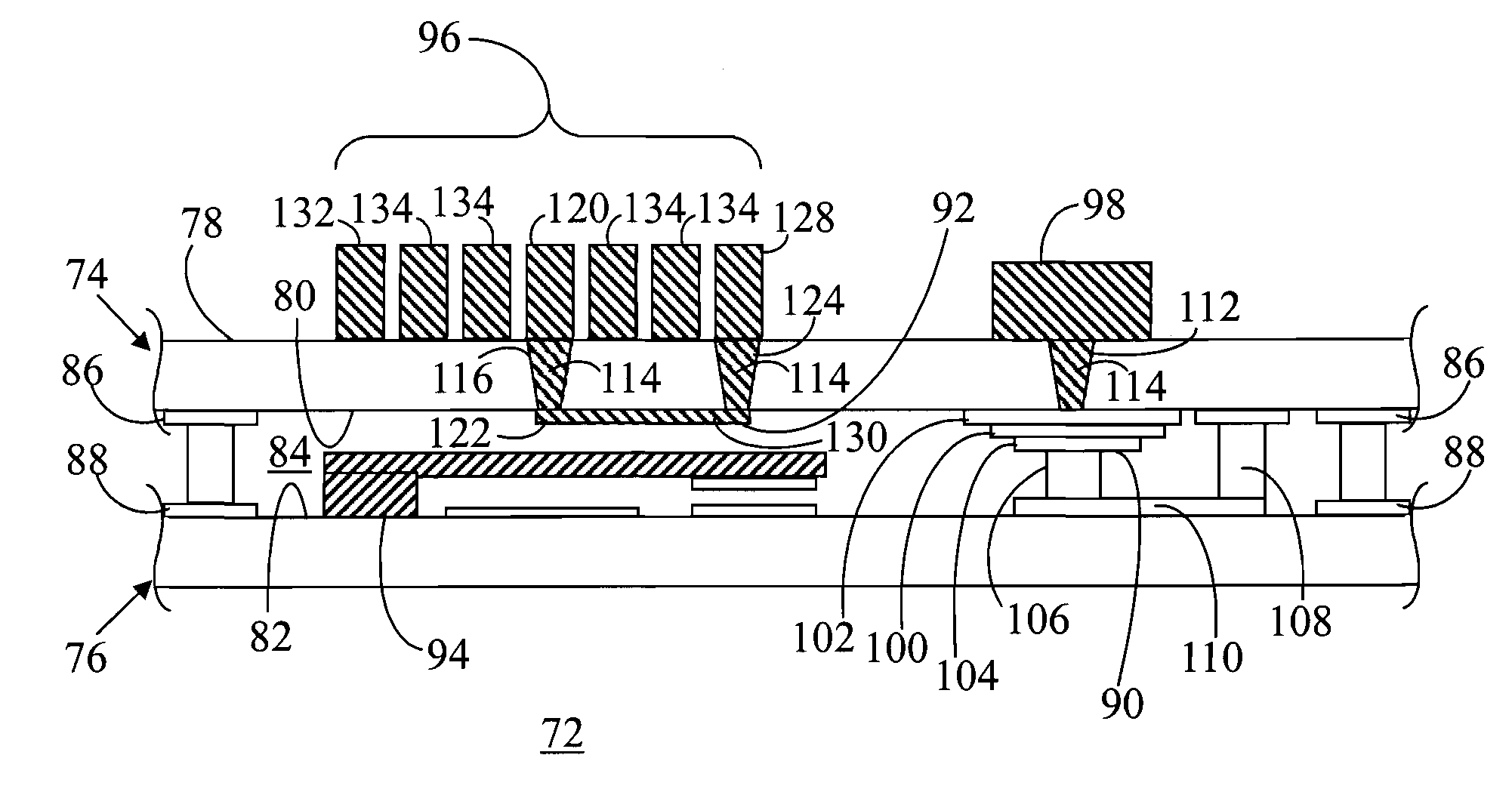

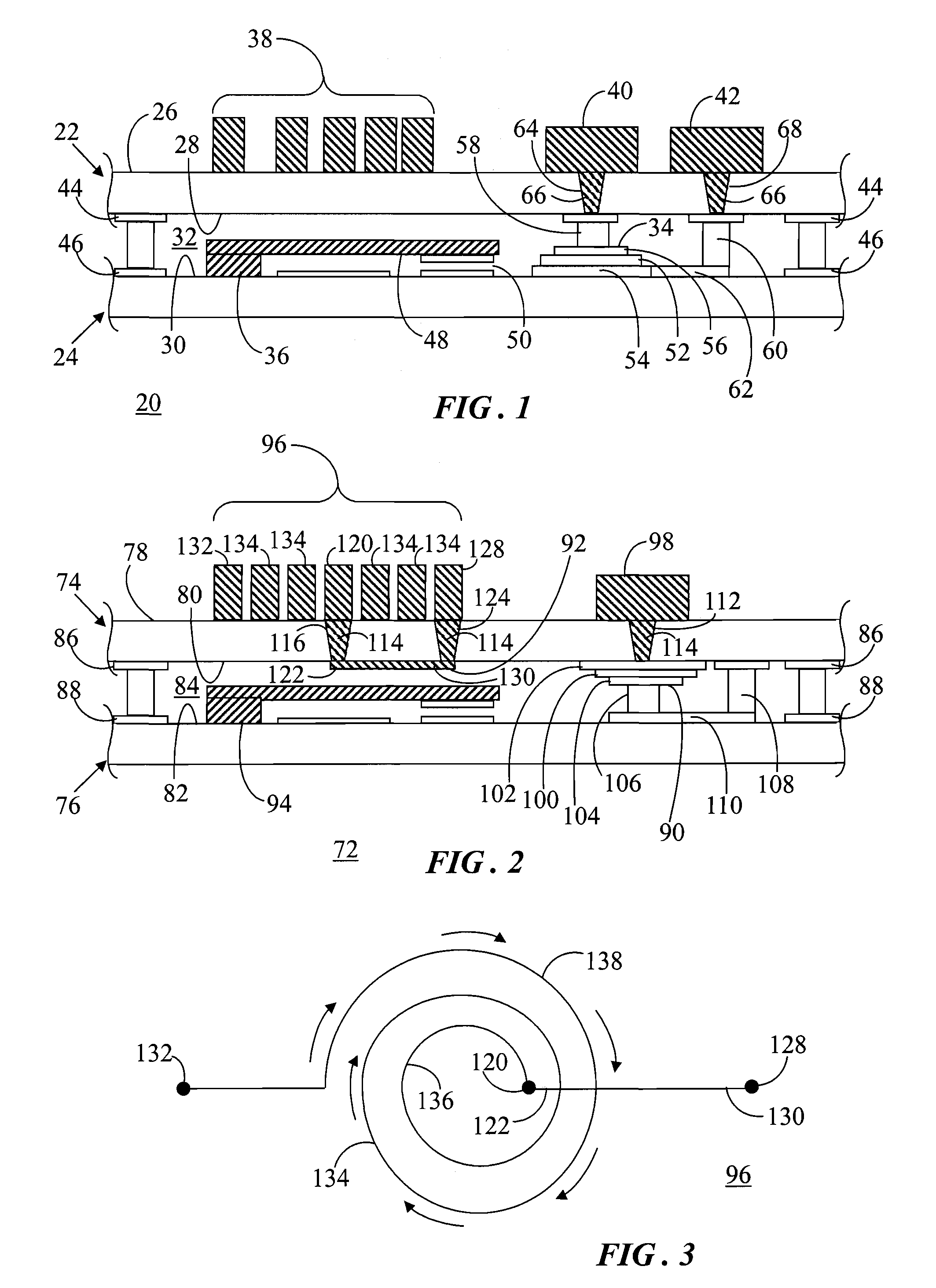

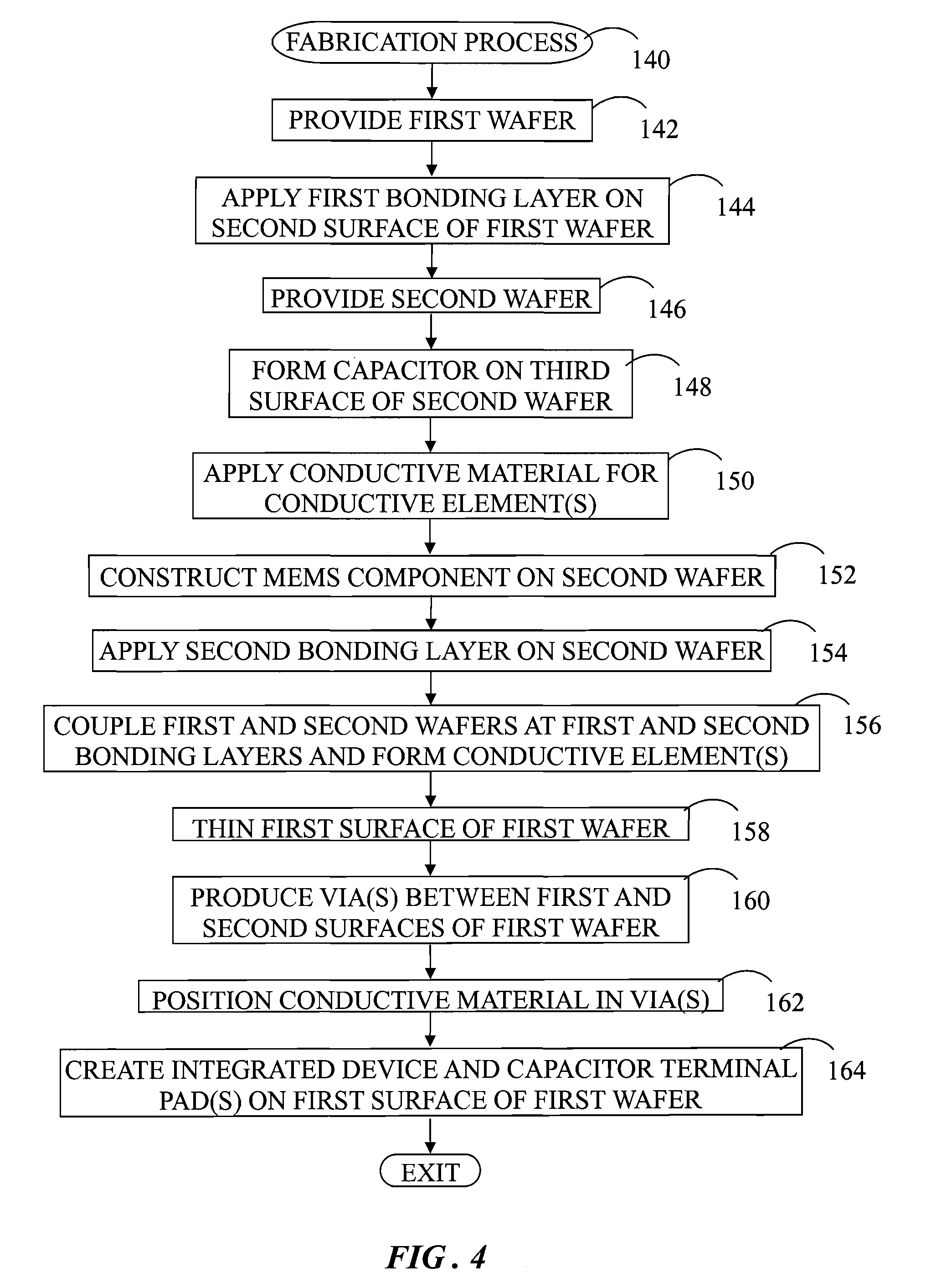

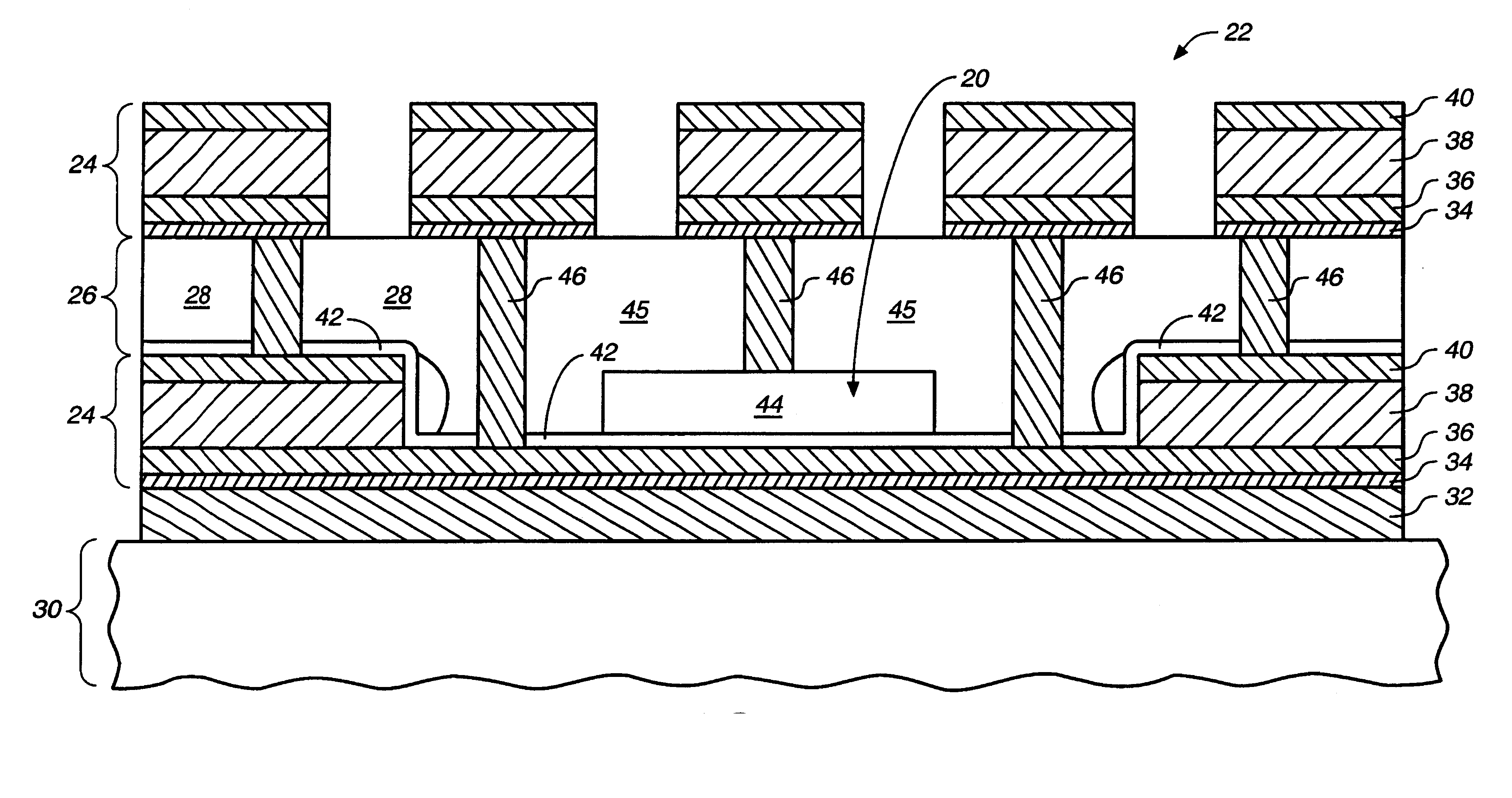

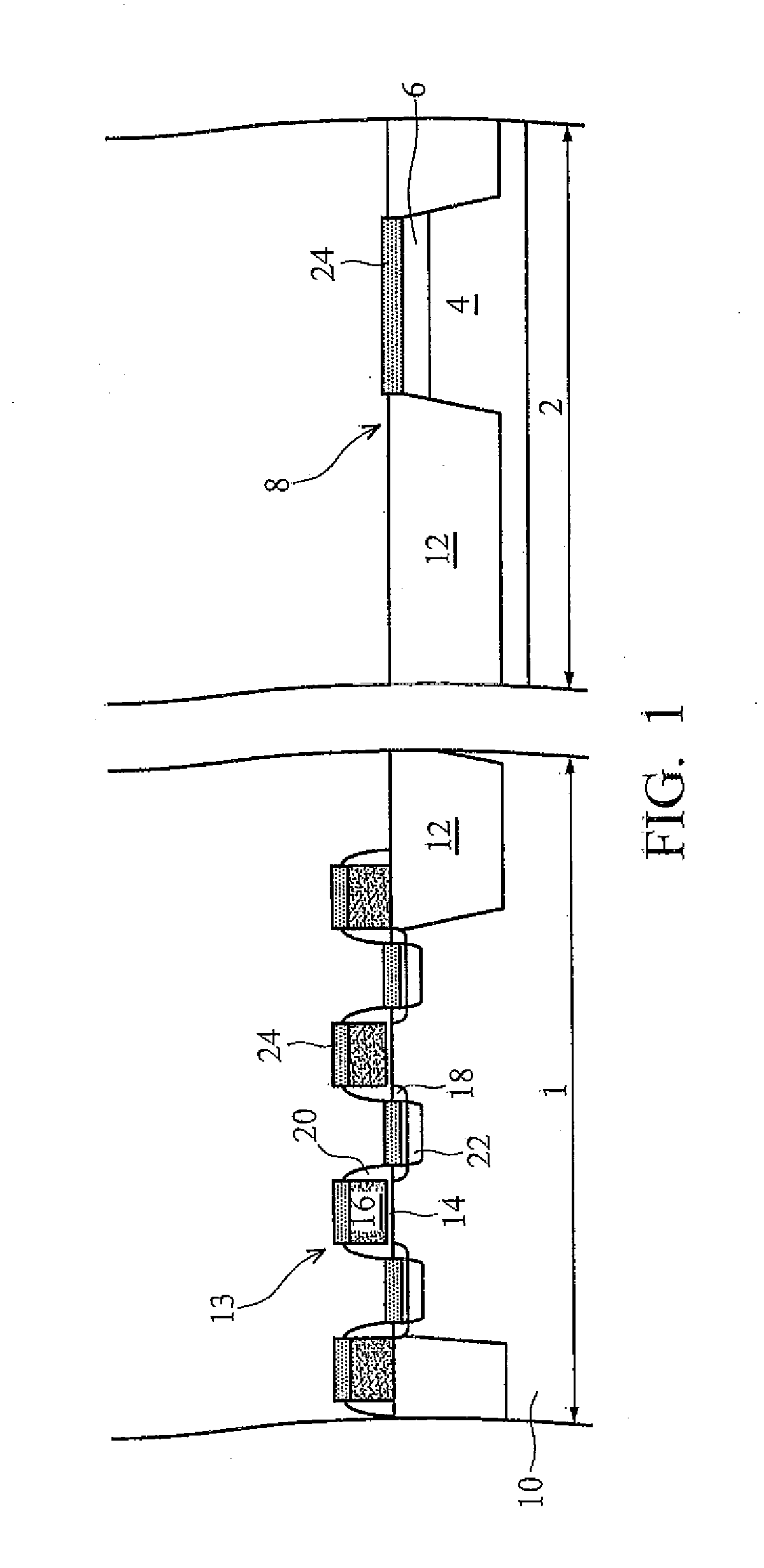

Integrated passive device and method of fabrication

InactiveUS7663196B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated devices

A device 20 includes substrates 22 and 24 coupled to form a volume 32 between the substrates. A surface 28 of the substrate 22 faces a surface 30 of the substrate 24. A metal-insulator-metal capacitor 34 is formed on one of the surfaces 28 and 30. A conductive element 58 spans between a top electrode 56 of the capacitor 34 and the other surface 28 and 30. Vias 64 and 66 extend through the substrate 22 and are electrically interconnected with the conductive element 58 and a bottom electrode 52 of the capacitor 34. Another device 72 includes an underpass transmission line 92 formed on a surface 80 of a substrate 74 within a volume 84 formed between the substrate 74 and another substrate 76. The line 92 underlies an integrated device 96 formed on a surface 78 of the substrate 74.

Owner:FREESCALE SEMICON INC

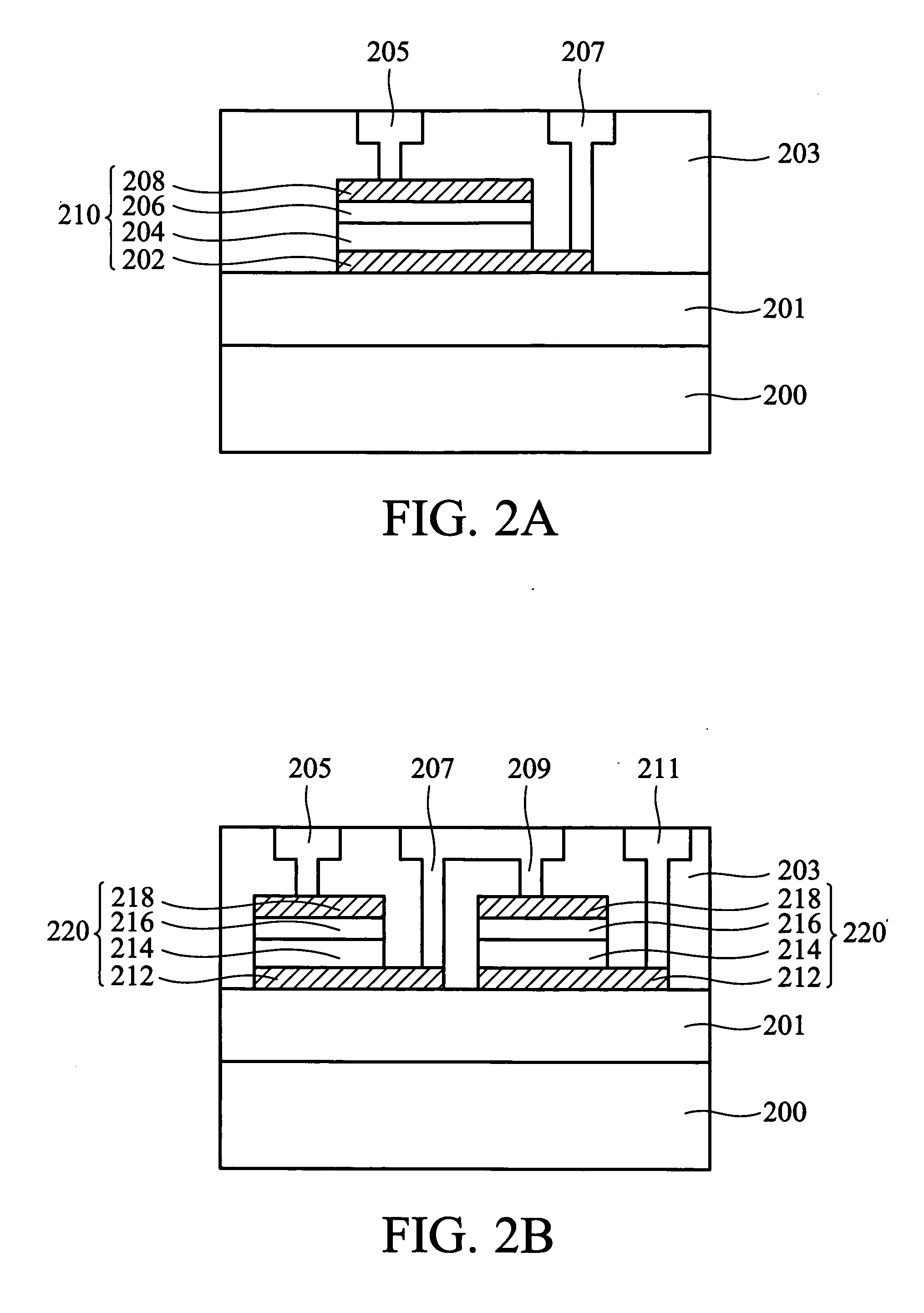

Metal-insulator-metal capacitor having a large capacitance and method of manufacturing the same

InactiveUS20050263848A1Large capacitanceAvoid leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceMetal-insulator-metal

A metal-insulator-metal (MIM) capacitor having a large capacitance, and a method of manufacturing the same, includes forming a lower electrode on a semiconductor substrate, sequentially forming a first dielectric film, an intermediary electrode, and a second dielectric film on an upper surface of the lower electrode, forming an inter-metal insulating layer on an upper surface of the second dielectric film, etching predetermined portions of the inter-metal insulating layer to form an upper electrode region and via hole regions, selectively etching the second dielectric film exposed in a portion of the via hole regions to expose the intermediary electrode, and forming a metal layer on the upper electrode region and the via hole regions, thereby forming an upper electrode and contact plugs.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming a metal-insulator-metal capacitor in an interconnect cavity

InactiveUS7118985B2Reduce the amount requiredUniform thicknessSemiconductor/solid-state device detailsSolid-state devicesMetalIntegrated circuit

A metal-insulator-metal capacitor is embedded in an interconnect layer of an integrated circuit (IC). The interconnect layer has a cavity, and the capacitor is formed in the cavity with one of the plates of the capacitor integral with a conductive layer of the interconnect layer, so the capacitor plate electrically communicates with the interconnect layer. The interconnect layer has multiple conductive layers, including a layer, such as aluminum, that is subject to deformation at certain temperatures during fabrication of the IC, and the cavity extends through this layer. A remaining conductive layer of the interconnect layer defines one of the capacitor plates, and a dielectric layer and another capacitor plate are formed thereon within the cavity. Via interconnects of about the same length electrically connect to the top plate and through the interconnect layer to the bottom plate.

Owner:BELL SEMICON LLC

Structure for protecting metal-insulator-metal capacitor in memory device from charge damage

Owner:TAIWAN SEMICON MFG CO LTD

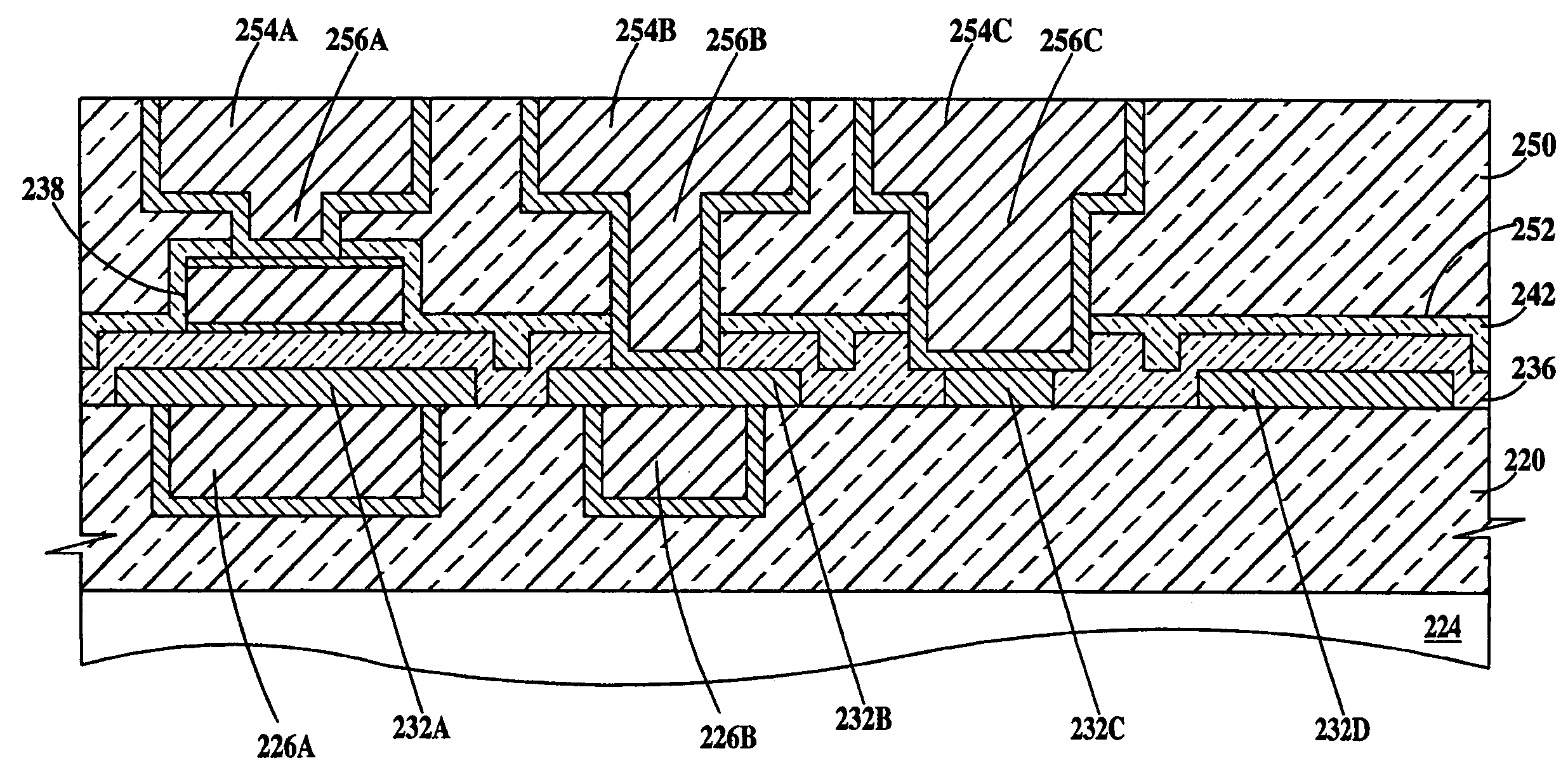

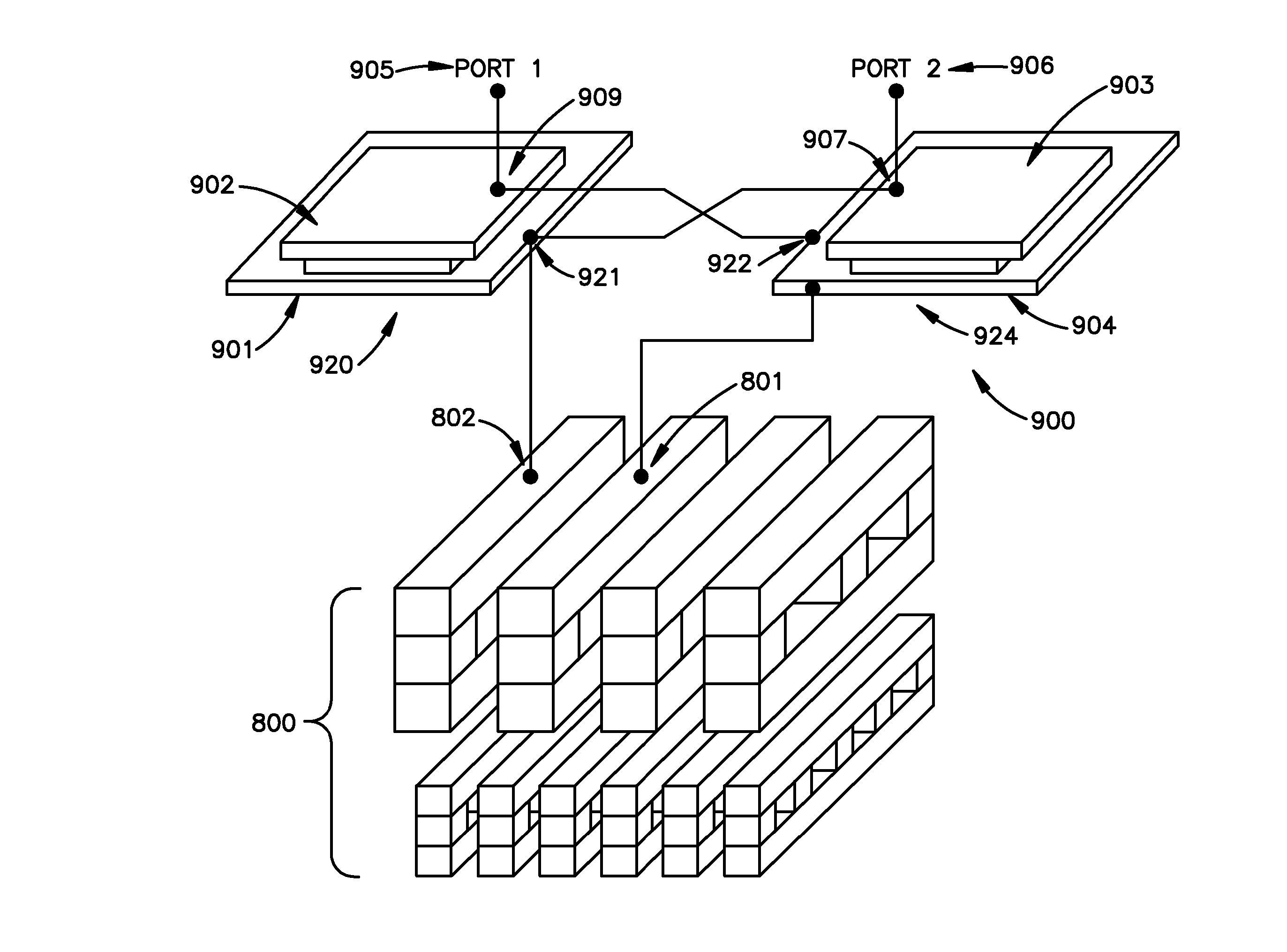

Method, system and design structure for symmetrical capacitor

InactiveUS20080099880A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceMetal-insulator-metal

Methods, articles and design structures for capacitance circuits are provided disposing a lower vertical-native capacitor metal layer above a planar front-end-of-line semiconductor base substrate, planar metal bottom plates spaced a bottom plate distance from the base and top plates above the bottom plates spaced a top plate distance from the base defining metal-insulator-metal capacitors, top plate footprints disposed above the base substrate smaller than bottom plate footprints and exposing bottom plate remainder upper lateral connector surfaces; disposing parallel positive port and negative port upper vertical-native capacitor metal layers over and each connected to top plate and bottom plate upper remainder lateral connector surface. Moreover, electrical connecting of the first top plate and the second bottom plate to the positive port metal layer and of the second top plate and the first bottom to the negative port metal layer impart equal total negative port and positive port metal-insulator-metal capacitor extrinsic capacitance.

Owner:TAIWAN SEMICON MFG CO LTD

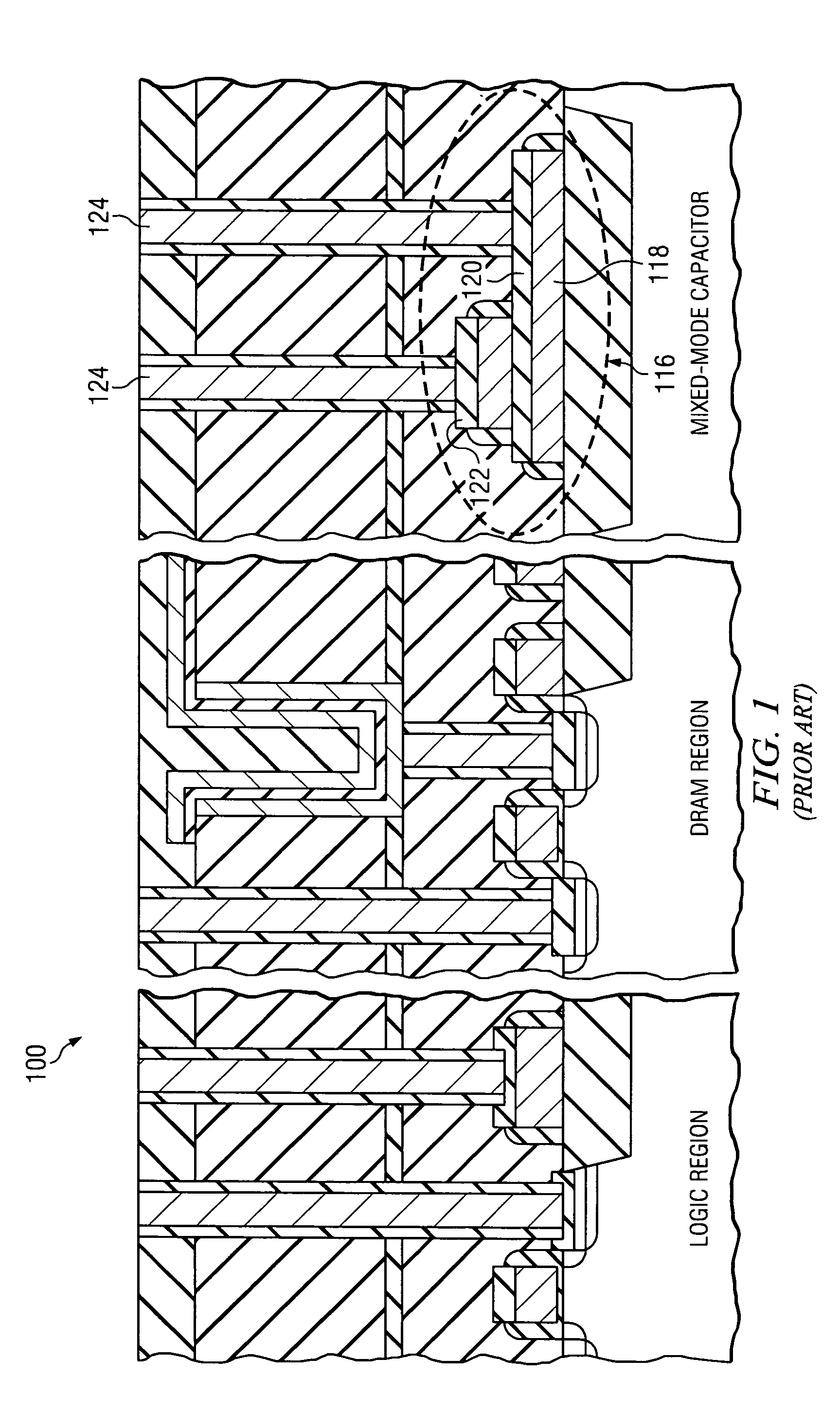

Integrated metal-insulator-metal capacitor and metal gate transistor

InactiveUS6787836B2Reduces void and surface irregularityTransistorSolid-state devicesEngineeringSemiconductor

An integrated circuit structure is disclosed that comprises a pair of capacitors, each having metal plates separated by an insulator, and metal gate semiconductor transistors electrically connected to the capacitors. The metal gate of the transistors and one of the metal plates of each of the capacitors comprise the same metal level in the integrated circuit structure. More specifically, each of the capacitors comprise a vertical capacitor having an upper metal plate vertically over a lower metal plate and each metal gate of the transistors and each upper metal plate of the capacitors comprise the same metal level in the integrated circuit structure.

Owner:INT BUSINESS MASCH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com