Method of forming a metal-insulator-metal capacitor in an interconnect cavity

a metal-insulator and interconnect layer technology, applied in capacitors, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of reducing the capacitance value, reducing the thermal expansion mismatch between aluminum layer components of the interconnect layer, and ic early failure, so as to reduce the number of fabrication steps, reduce the amount of planarization, and simplify the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

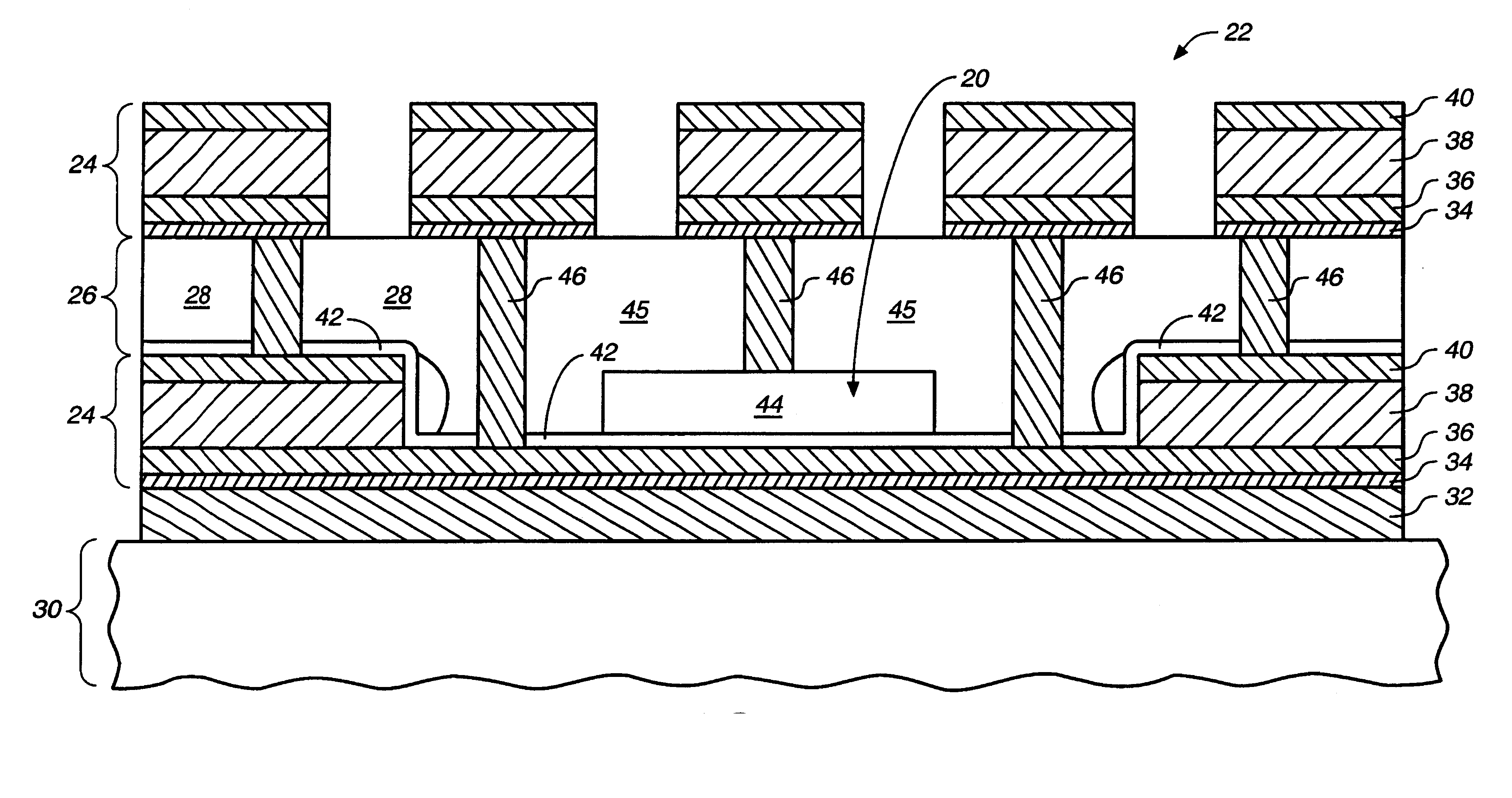

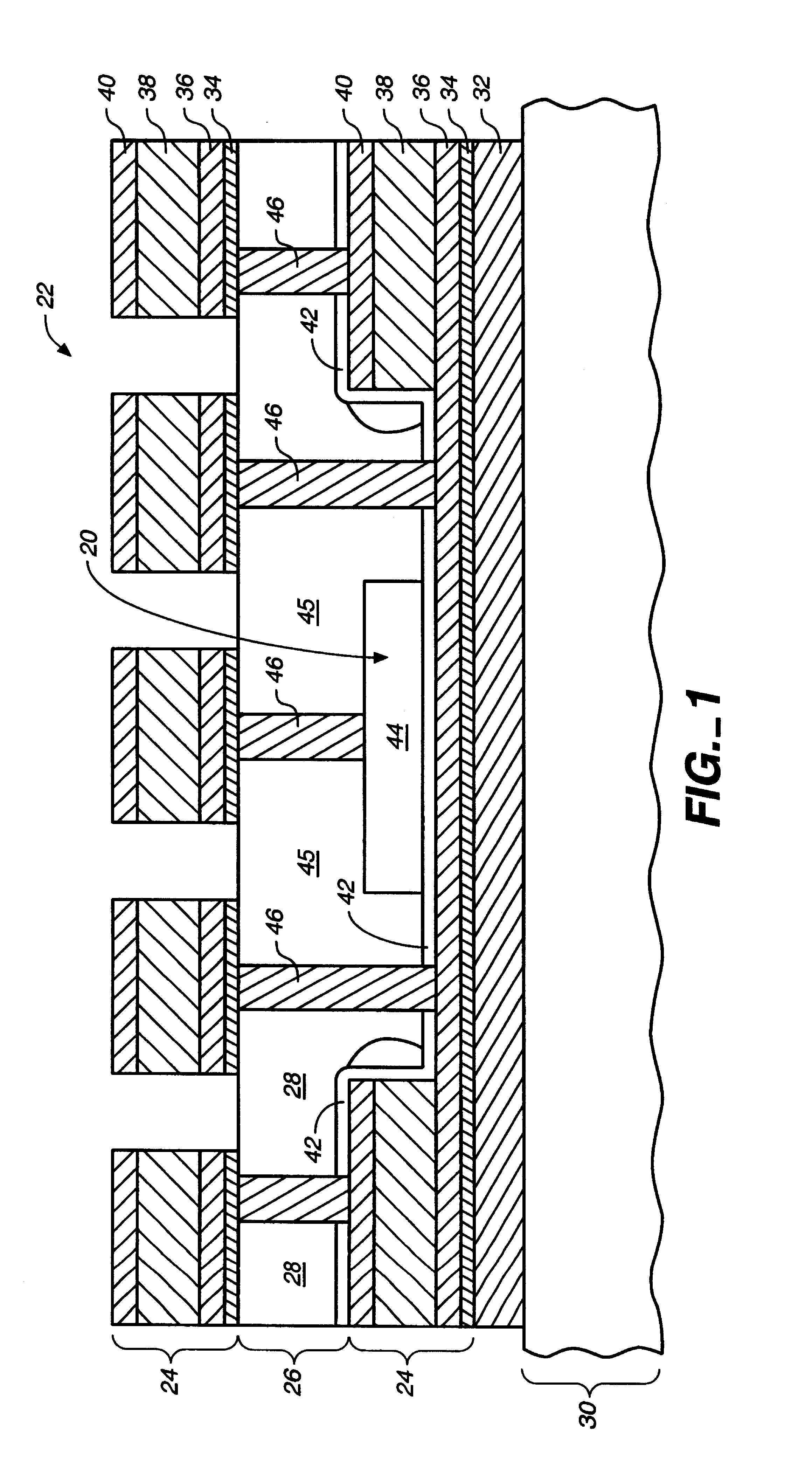

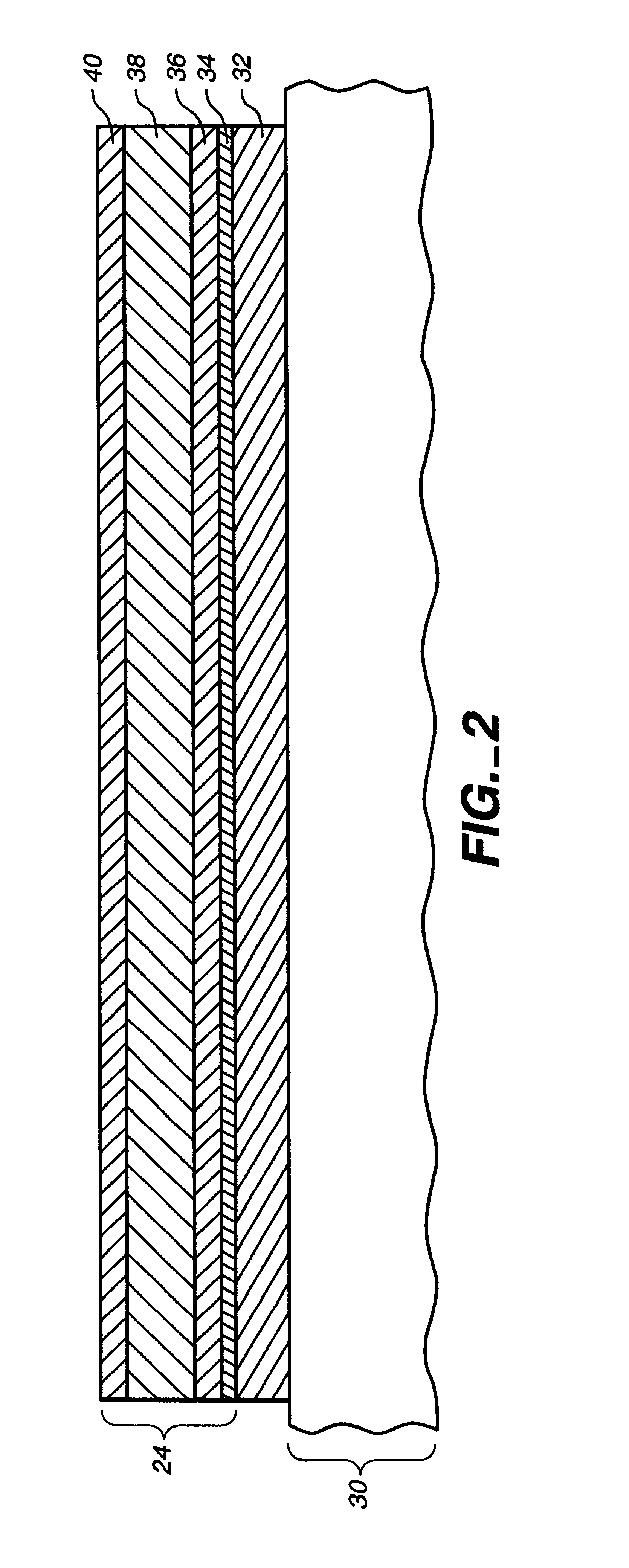

[0019]A capacitor 20 which embodies the present invention is incorporated in an integrated circuit (IC) 22 such as is shown in FIG. 1. The IC 22 is of the type having multiple layers 24 of electrical conductors known as interconnects. The electrical conductors of each interconnect layer 24 extend between and connect to the other functional components (not shown) of the IC 22. Each interconnect layer 24 is separated by a relatively thick layer 26 of interlayer dielectric (ILD) or intermetal dielectric (IMD) insulating material 28. The insulating material28 of each IMD layer 26 electrically insulates the conductors of the interconnect layers 24 from one another and electrically insulates the other components within the IC 22 from one another.

[0020]The multiple interconnect layers 24 and IMD layers 26 are built or layered above one another and overlying a substrate 30 of the IC 22. The substrate 30 serves as the foundation for the IC and its functional components formed in and on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More