Separation grid flash element and manufacture method thereof

A technology of split gate and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve problems affecting the yield and performance of split-gate flash components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Some of the following examples of the present invention will not describe well-known structures and processes to avoid unnecessary confusion. The preferred embodiments of the present invention will be described in detail below with accompanying drawings.

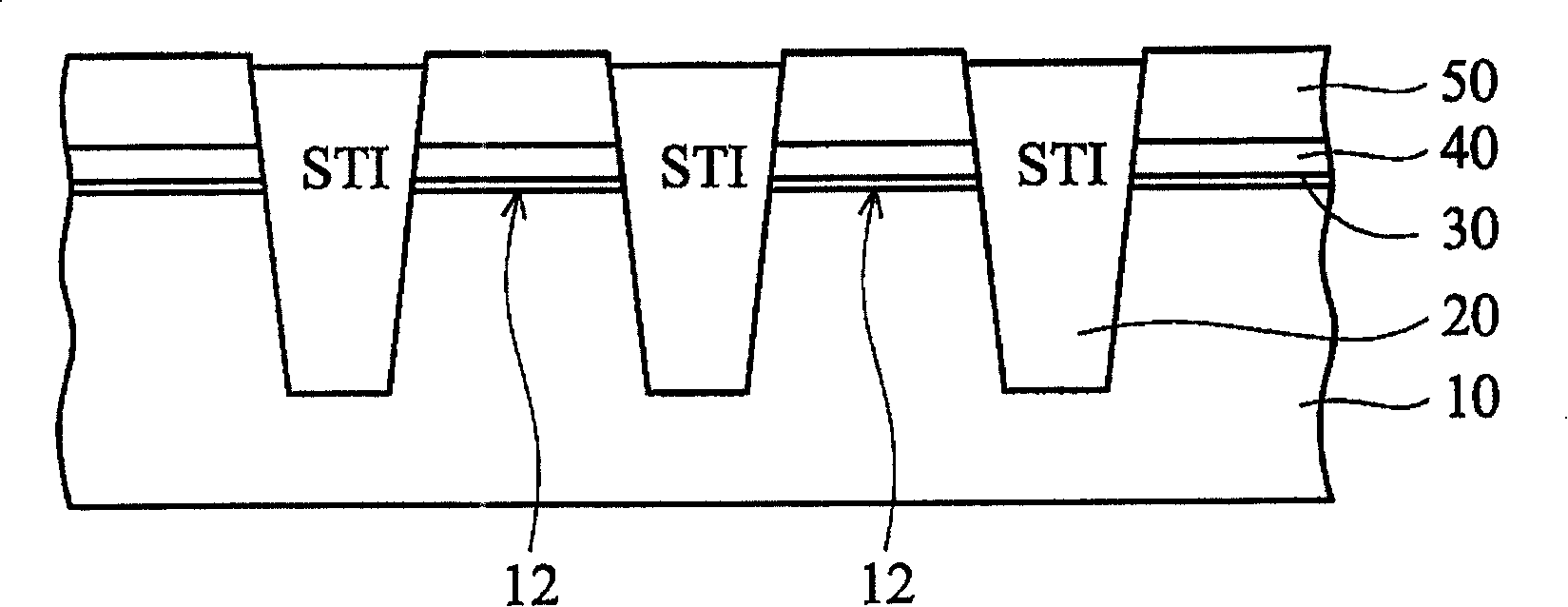

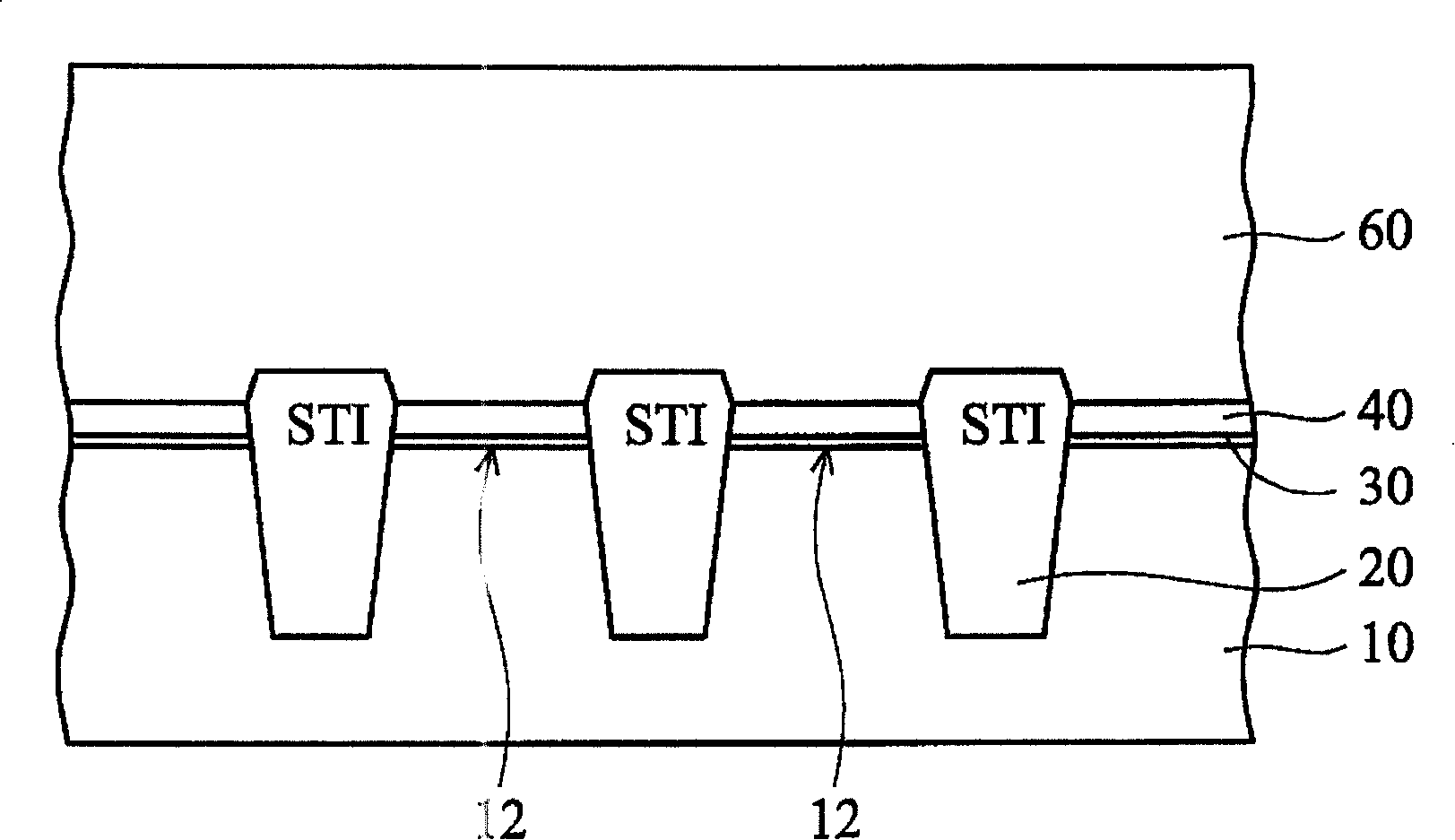

[0039] Figure 11 It is a cross-sectional view along the section line "2" in an embodiment of the present invention, and it is a split gate flash device before trenches are formed. Substrate 10 comprises any suitable semiconductor material or combination of materials, such as single crystal silicon or silicon-on-insulator (SOI). The dielectric layer 30 on the substrate 10 is a floating gate dielectric layer, which may include any dielectric material with a suitable dielectric constant and breakdown capacitance, preferably an oxide material, or silicon oxide thermally grown on the substrate 10 More preferably, the thickness is about 40 angstroms to 150 angstroms.

[0040] A conductive layer 40 is then formed on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More