Memory data processing method of cache failure processor

A cache invalidation and instruction processing technology, applied in the field of processor access instruction processing where cache access fails, can solve problems such as pipeline blocking, Cache pollution, sacrificing storage bandwidth, etc., to avoid Cache pollution, reduce frequency, The effect of saving memory access bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The specific implementation process is explained below in conjunction with the drawings and embodiments, and the present invention is further described in detail.

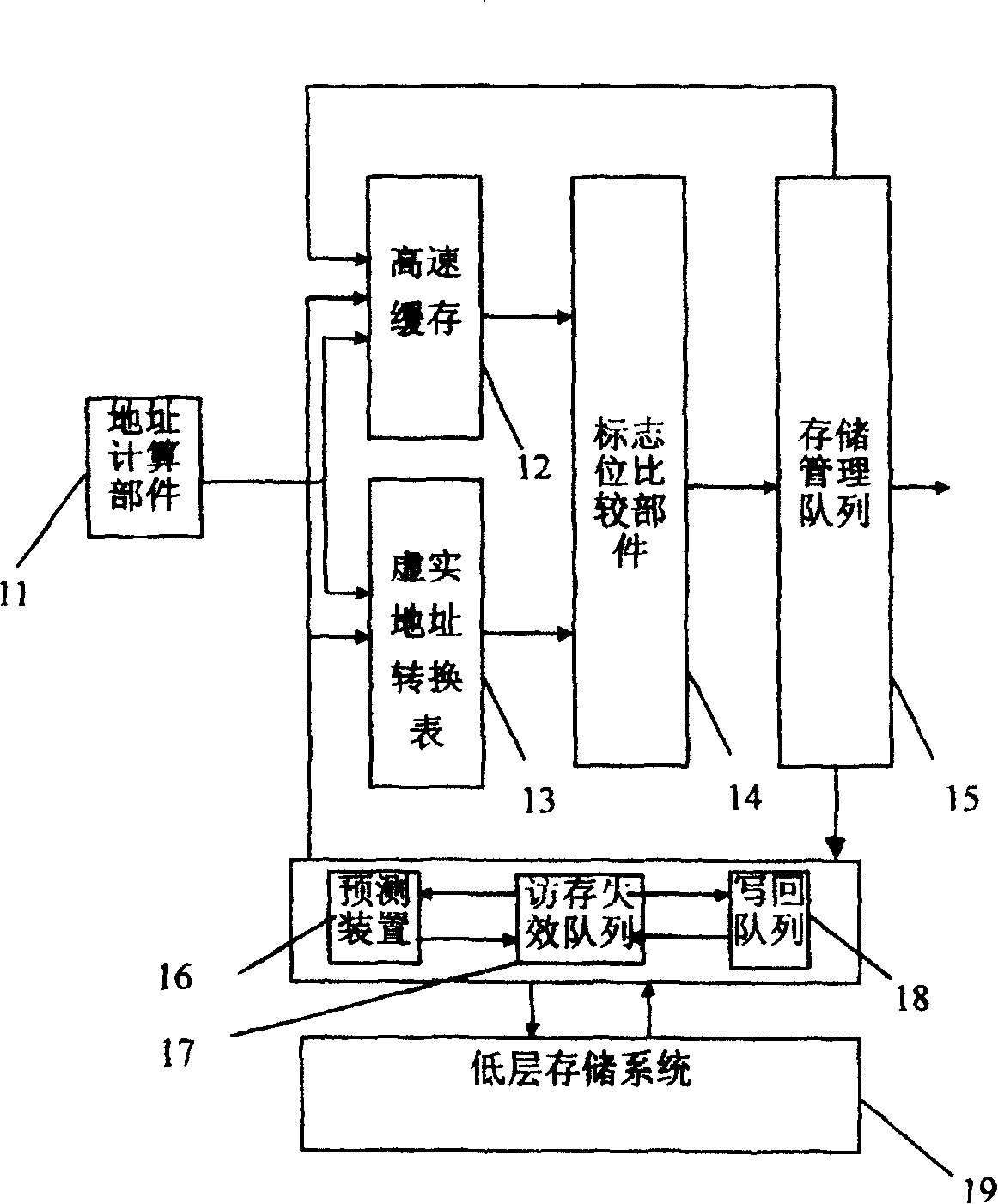

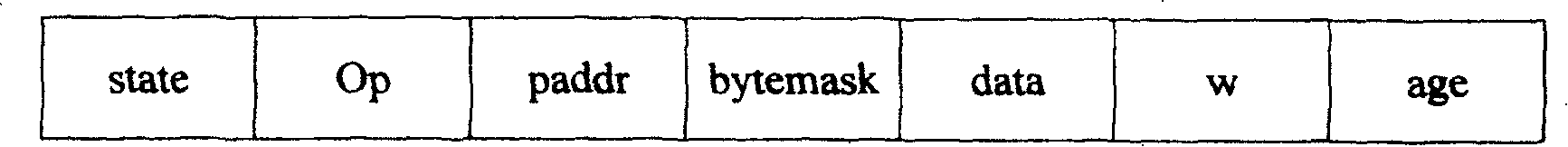

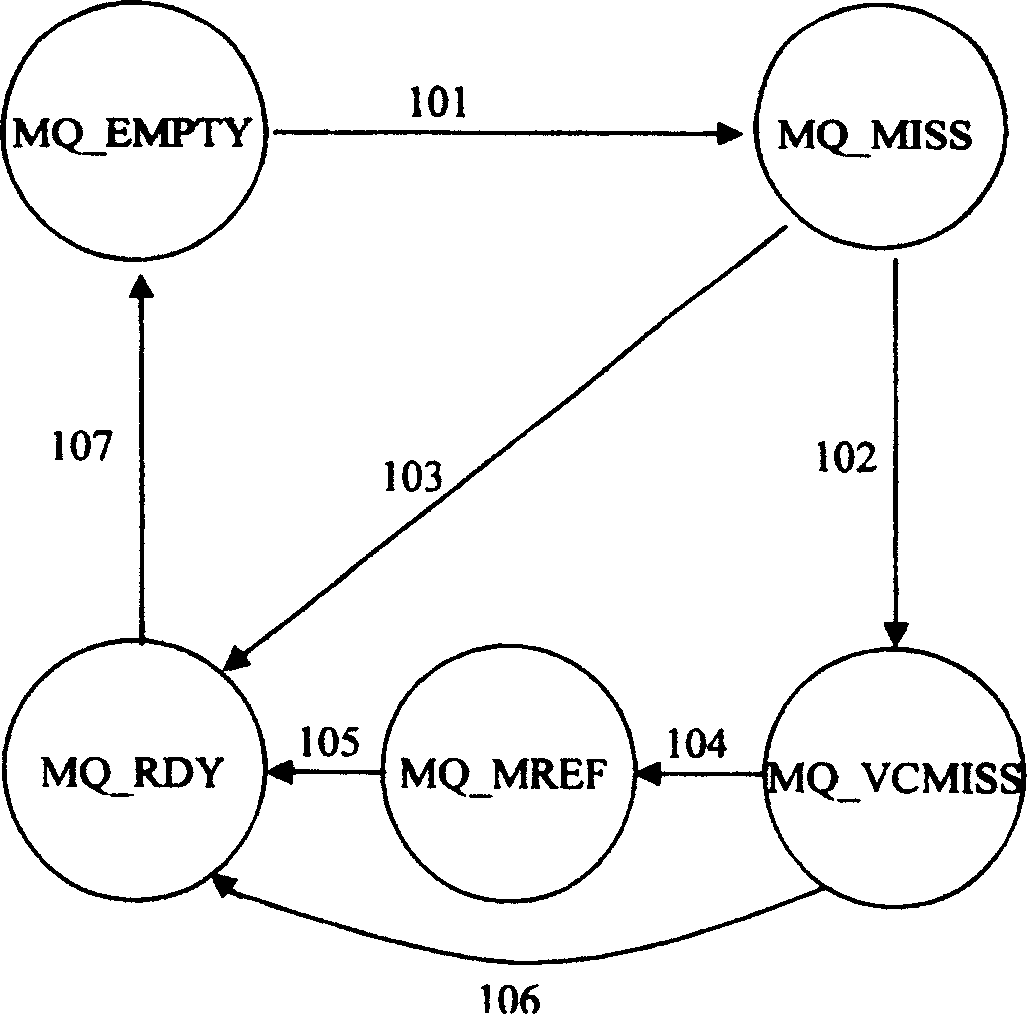

[0046] Such as Figure 1 Shown is a schematic diagram of the microarchitecture of the memory access module of the present invention. The address calculation component (MEM AddressCalculate) 11 is used to calculate the address of the memory fetch instruction; the cache (Cache) 12 is used to cache the most recently used data; the virtual address conversion table (TLB) 13 is used to access the virtual address of the memory fetch instruction Converted into a physical address; the tag bit comparison component (Tag Compare) 14 performs tag bit comparison to determine whether the cache is hit or not; the Load Store Queue 15 records the information about whether the cache is hit or not, and manages memory access instructions; The memory invalidation queue (Miss Queue) 17 handles the memory access instructions for cache ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More