Method for checking software edition in programmable logic element

A software version and programming logic technology, applied in the field of electronics or communication, can solve the problems of software version can not be verified, low reliability, etc., to achieve software version verification and upgrade, reduce dependencies, and improve verification reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

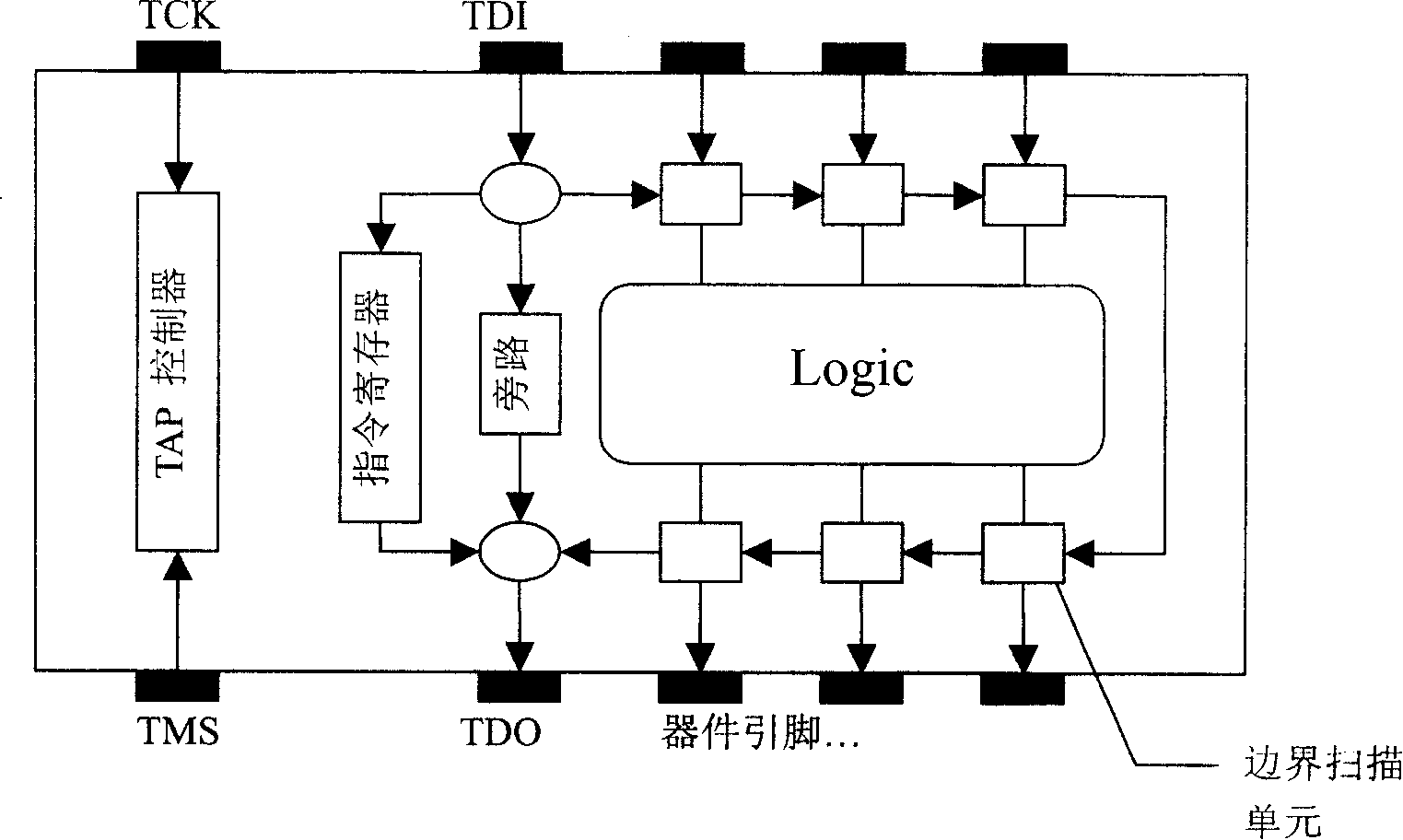

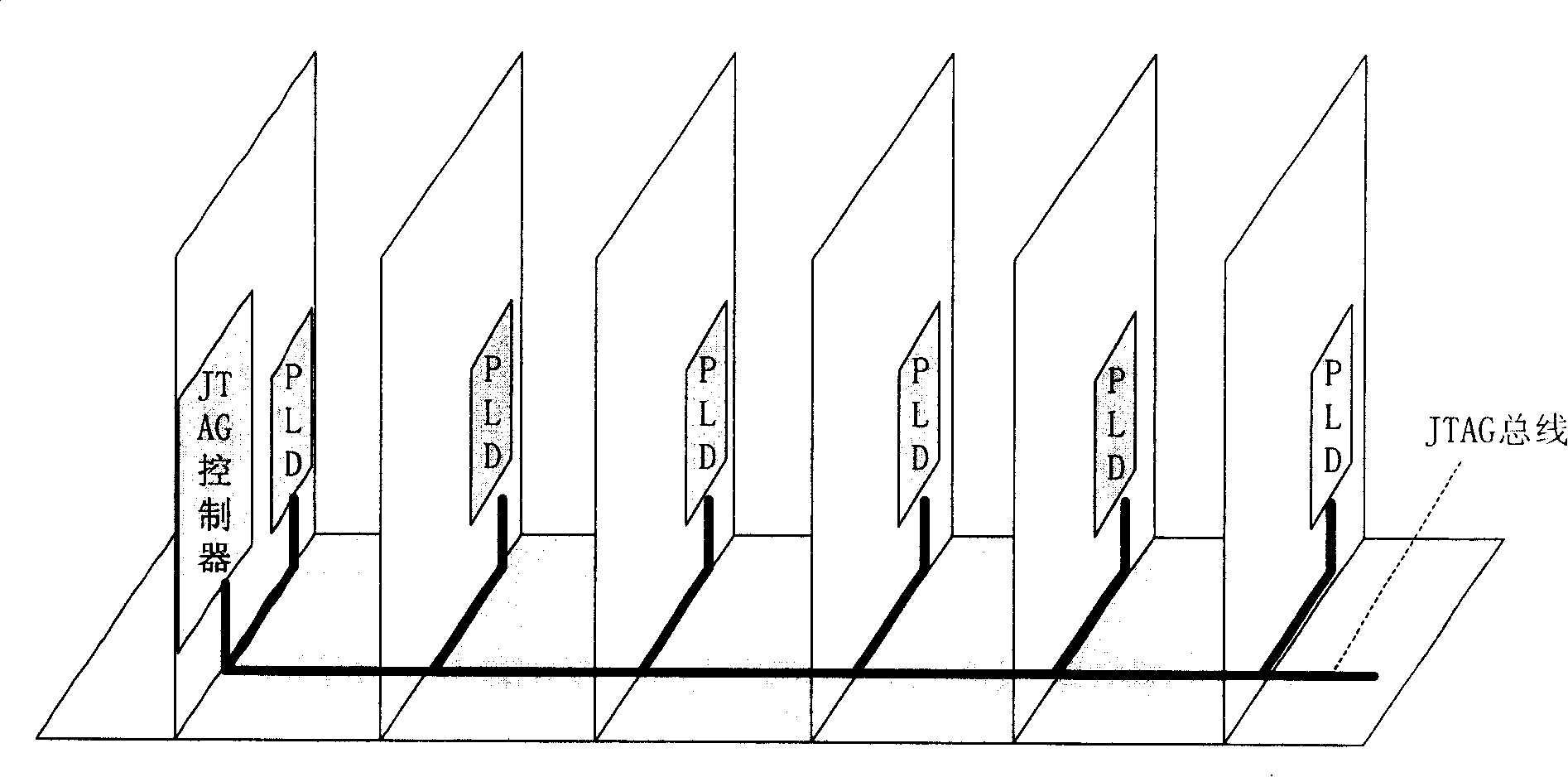

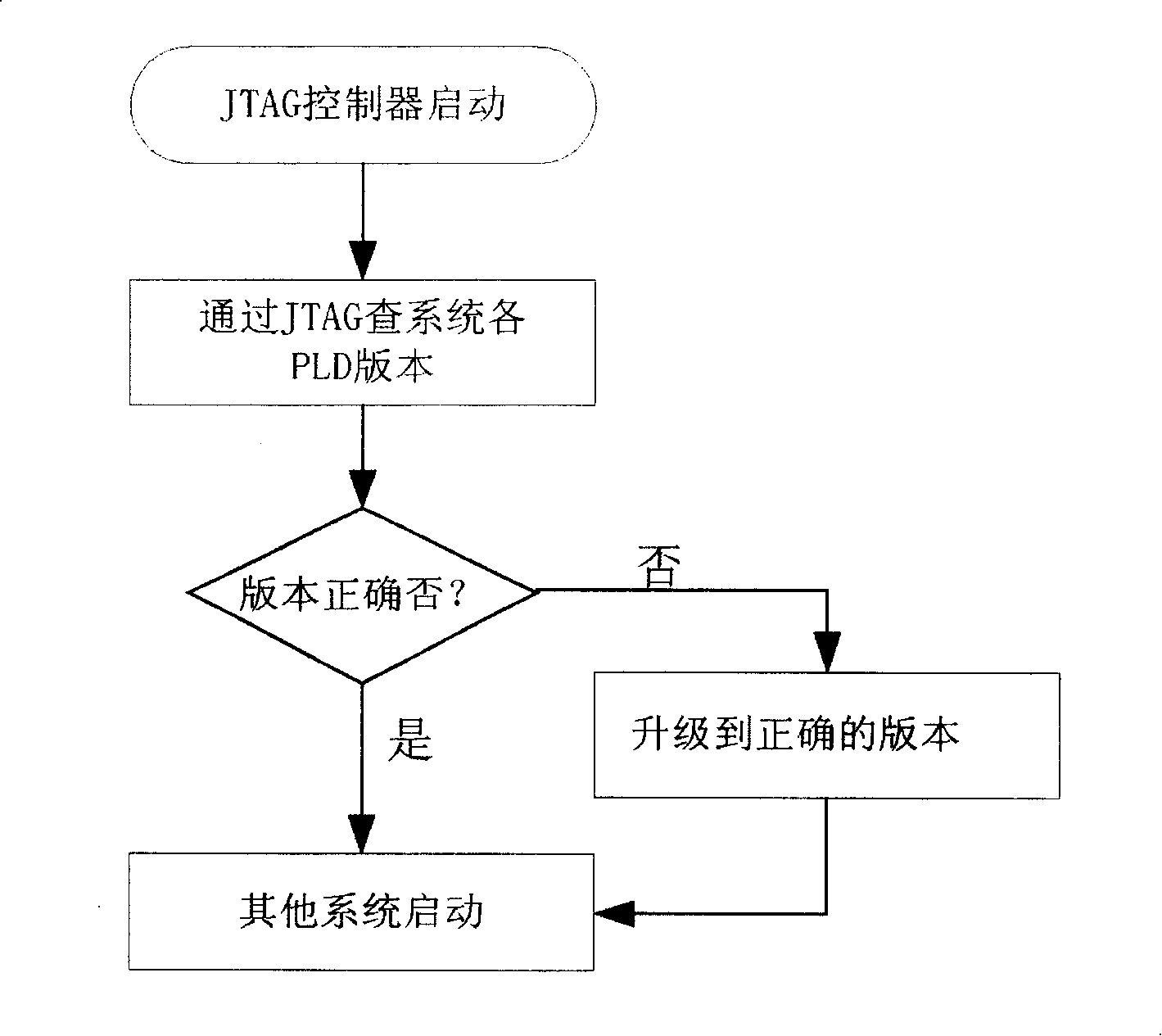

[0026] Boundary-scan testing technology was developed based on the JTAG (Joint Test Action Group) interface as a solution to the PCB physical access problem caused by the increasing crowding of board assemblies due to new packaging technologies. In 1988, some companies in North America jointly established the Joint Test Action Group (JTAG: Joint Test Action Group), which standardized the initial Boundary Scan technology. In 1990, IEEE (Institute of Electrical and Electronic Engineers) accepted the specification as standard 1149.1. Boundary-scan embeds test circuitry at the chip level to form a comprehensive board-level test protocol. Using the boundary-scan industry standard IEEE 1149.1, complex assemblies can be tested, debugged, programmed in-system devices, and hardware problems diagnosed. With access to scan path I / O, the need for physical test points on the board can be eliminated or greatly reduced. In addition to board testing, boundary scan testing allows programming...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More