Fault-tolerant directory cache controller

A directory cache and controller technology, applied in memory systems, instruments, electrical digital data processing, etc., can solve problems such as poor fault tolerance, low reliability, and inability to meet the space environment or complex electromagnetic environment of the directory cache

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0095] Embodiments of the present invention will be described below through specific examples.

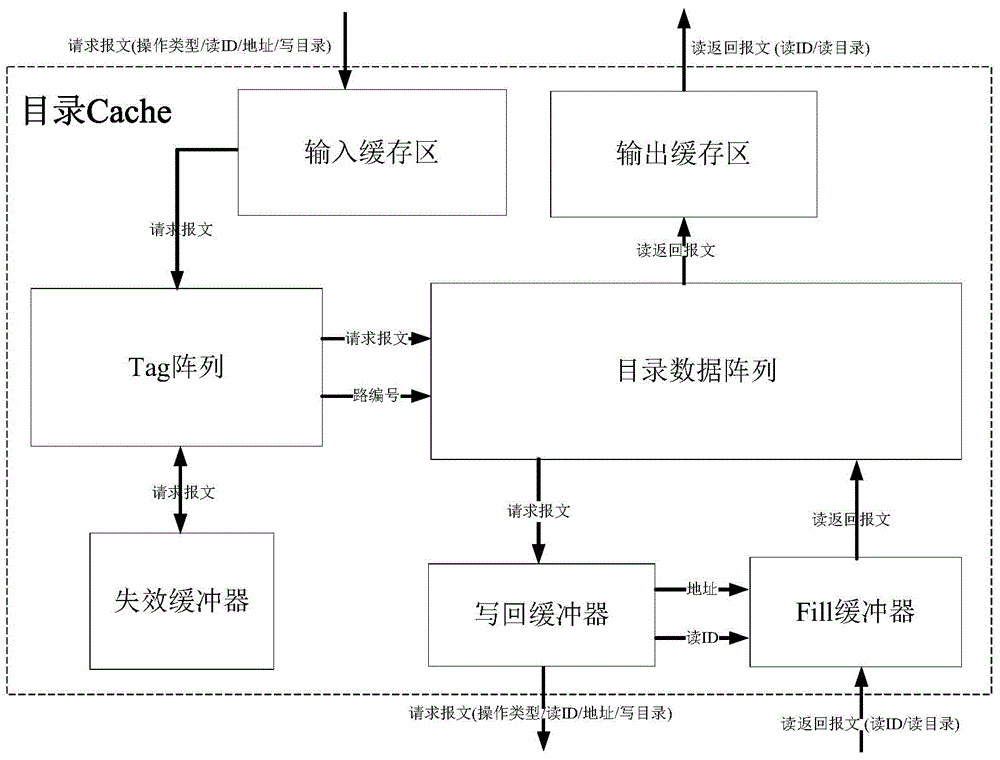

[0096] Such as Figure 4 As shown, the fault-tolerant directory Cache controller of the present invention consists of 4 identical DCB modules, 1 directory access bypass DAP module, 1 directory access crossbar DAX module, 1 memory access crossbar MAX module and 1 configuration register constitute. The four directory cache bodies are respectively recorded as the zeroth directory cache body DCB 0 , the first directory cache body DCB 1 , the second directory cache body DCB 2 and third directory cache body DCB 3 , the internal structure and connection relationship of the four directory cache bodies are exactly the same. The connection relationship between each component is: the directory access cross switch DAX is connected to the external interface through the request message signal and the read return message signal, and the DCB 0 、DCB 1 、DCB 2 、DCB 3 , DAP is co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More