Semiconductor device

A semiconductor and connection device technology, which is applied in the manufacture of semiconductor devices, hoisting devices, semiconductor/solid-state devices, etc., can solve the problems of hindering high-speed operation, delaying the export of carriers, etc., and achieve the goal of seeking high speed and suppressing the extraction time The effect of deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

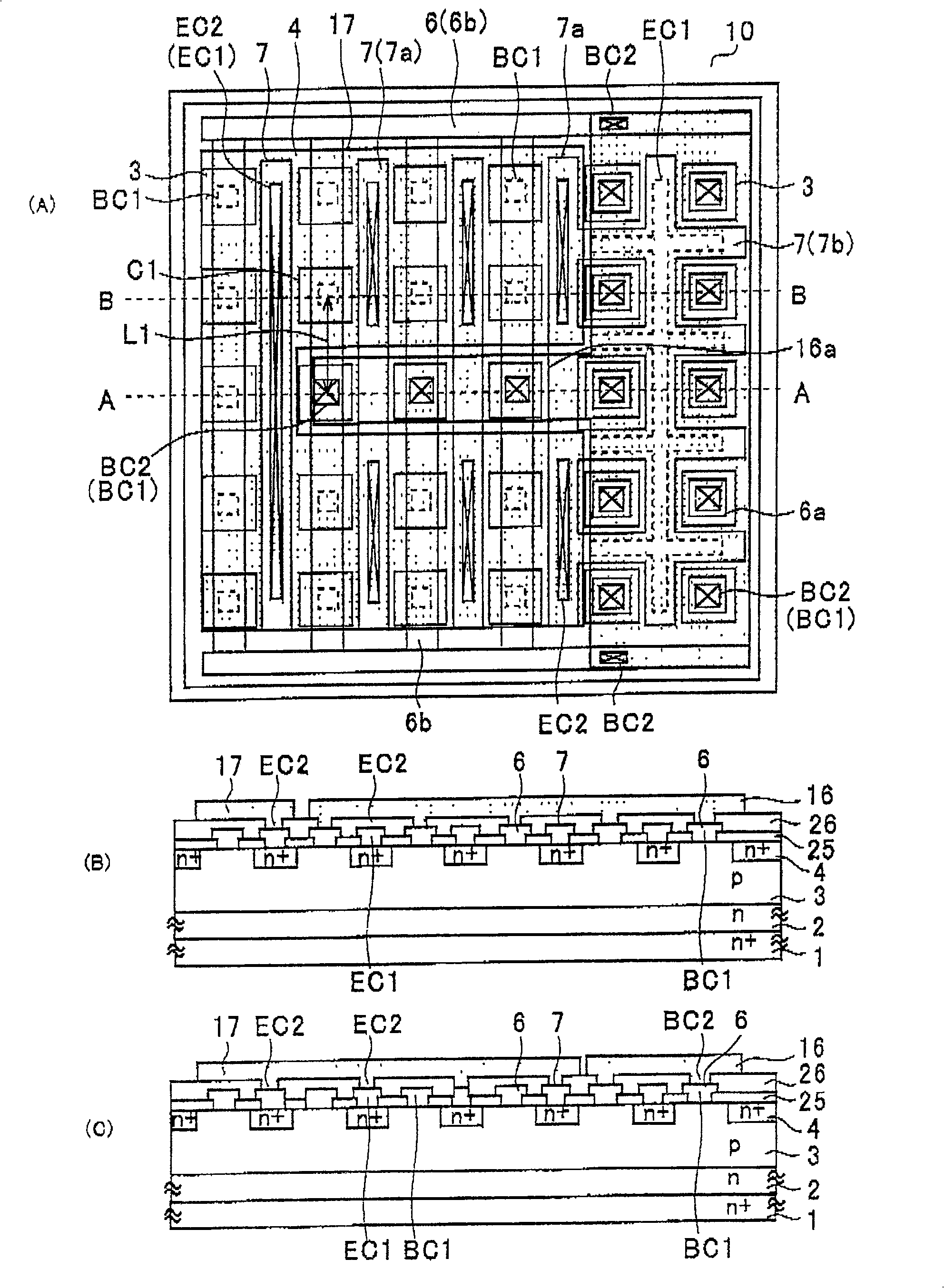

[0068] refer to Figure 1 ~ Figure 3 , taking an npn type bipolar transistor as an example to describe the embodiment of the present invention in detail.

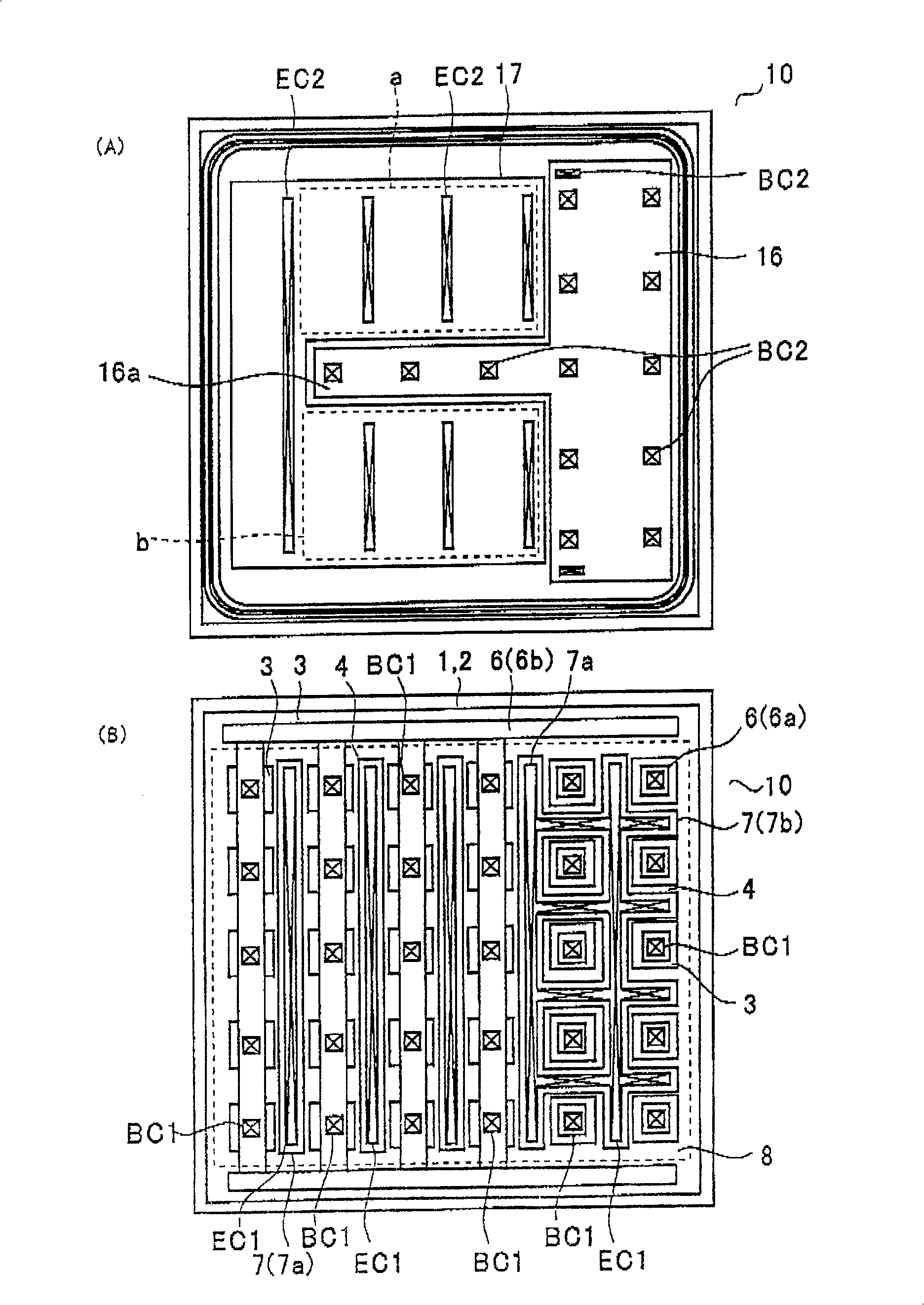

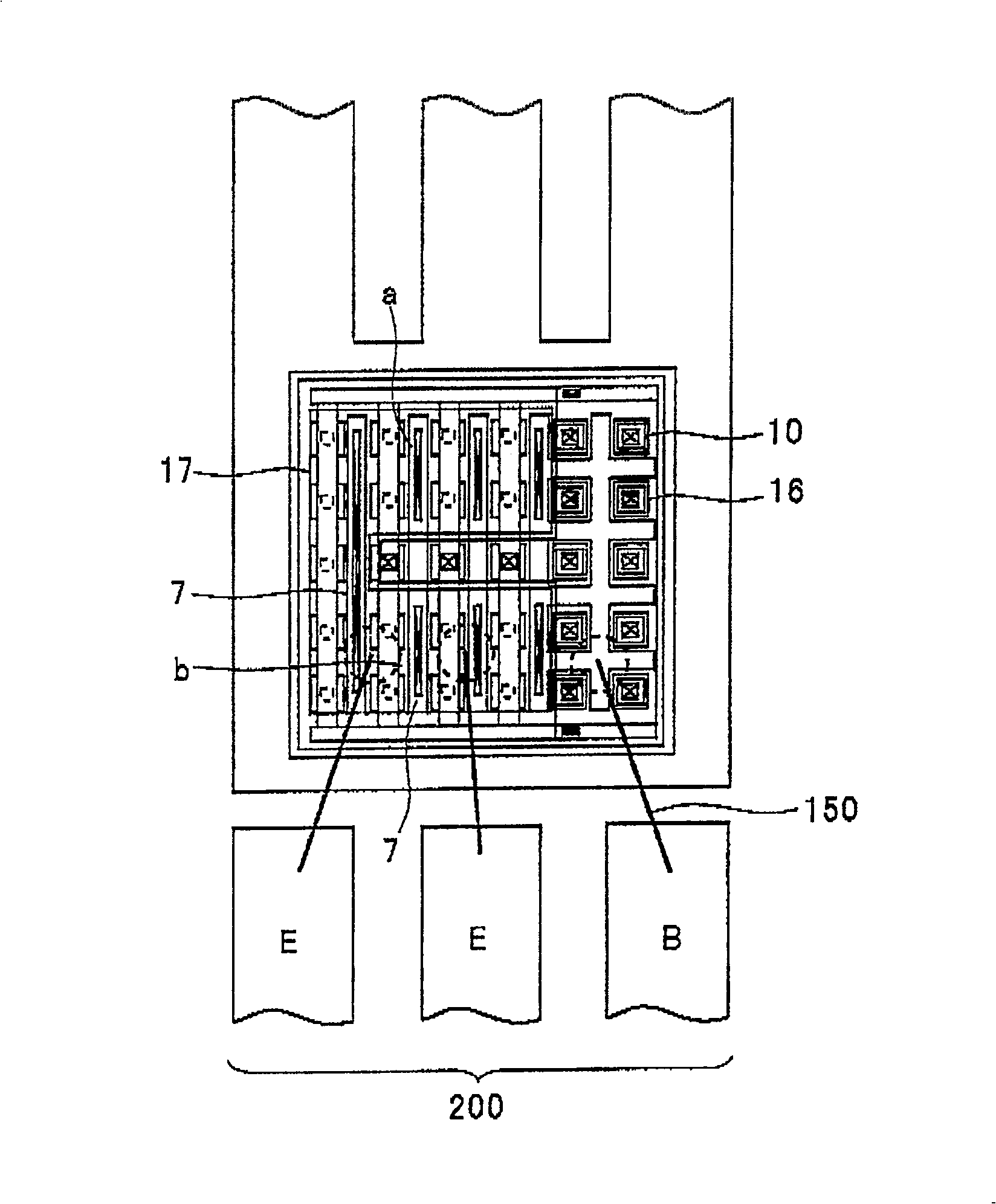

[0069] figure 1 The structure of the semiconductor device 10 as an embodiment of the present invention is shown. figure 1 (A) is a plan view showing the second layer electrode structure, figure 1 (B) is a plan view showing the electrode structure of the first layer and the diffusion region.

[0070] The npn-type bipolar transistor 10 of this embodiment consists of a collector region 2, a base region 3, an emitter region 4, a first base electrode 6, a first emitter electrode 7, a second base electrode 16, a second emitter pole electrode 17 and the protruding portion 16a of the second base electrode.

[0071] The semiconductor substrate 1 is a high-concentration n + -type semiconductor substrate on which, for example, an n-type epitaxial layer or the like is grown to provide a collector region 2 .

[0072] The base re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More