Level shift circuit and semiconductor integrated circuit having the same

A technology for converting circuits and levels, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, electrical components, etc., which can solve problems such as reliability degradation and achieve power consumption reduction and power saving The effect of consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

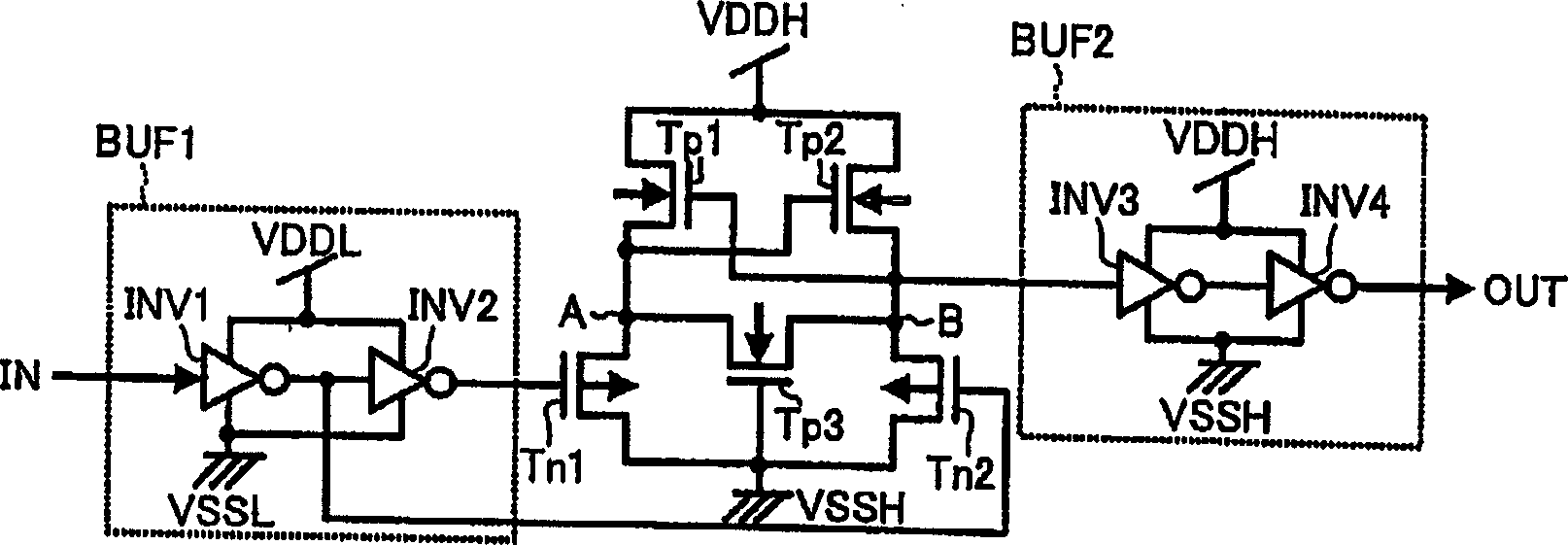

[0041] figure 1 is a configuration diagram showing a level conversion circuit according to Embodiment 1 of the present invention.

[0042] exist figure 1 Among them, BUF1 is a buffer on the input side of the inverters INV1, INV2 that operates at a low supply voltage VDDL and ground (0V) VSSL for this voltage; BUF2 is a buffer that operates at a high supply voltage VDDH and includes inverters Buffers on the output side of phasers INV3 and INV4. The circuit configuration of these buffers BUF1 and BUF2 is only required to have a buffer function, and does not need to be a circuit in which a multistage inverter is connected.

[0043] In addition, in figure 1 Among them, Tn1 and Tn2 are the first and second Nch MOS transistors. Its source is connected to the ground (0V) VSSH for the above-mentioned high-voltage power supply VSSH. Tp1 and Tp2 are the first and second P-channel Pch MOS transistors, the sources of which are connected to the above-mentioned high-voltage power su...

Embodiment 2

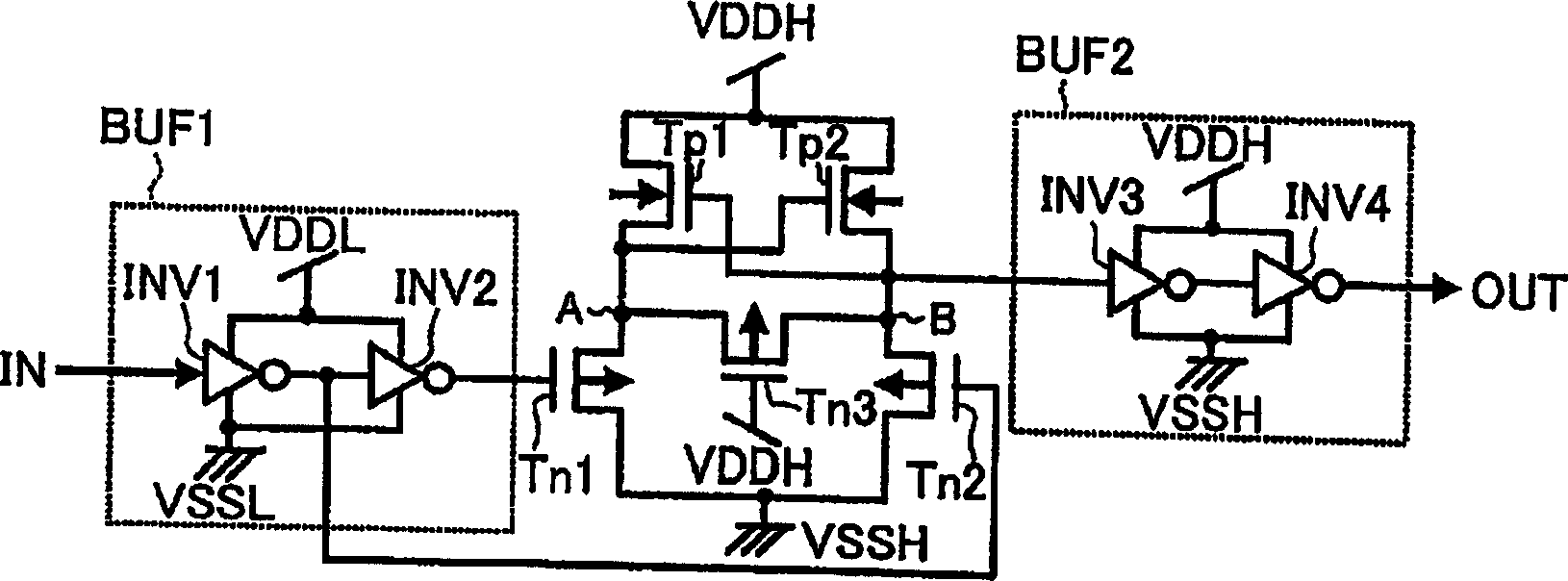

[0057] Next, a level conversion circuit according to Embodiment 2 of the present invention will be described.

[0058] figure 2 The configuration of the level conversion circuit of the second embodiment is shown. figure 2 The level-shifting circuit shown with the figure 1 The level shifting circuit differs in that the figure 1 The transistor constituting the resistor is a Pch MOS transistor Tp3, and in this embodiment, it is composed of an Nch MOS transistor Tn3. Specifically, the source of the Nch MOS transistor (resistor) Tn3 is connected to the node A, the drain is connected to the node B, the gate is connected to the high-voltage power supply VDDH, and is always on.

[0059] Therefore, also in this embodiment, the same effect as that of the above-mentioned embodiment 1 is obtained.

Embodiment 3

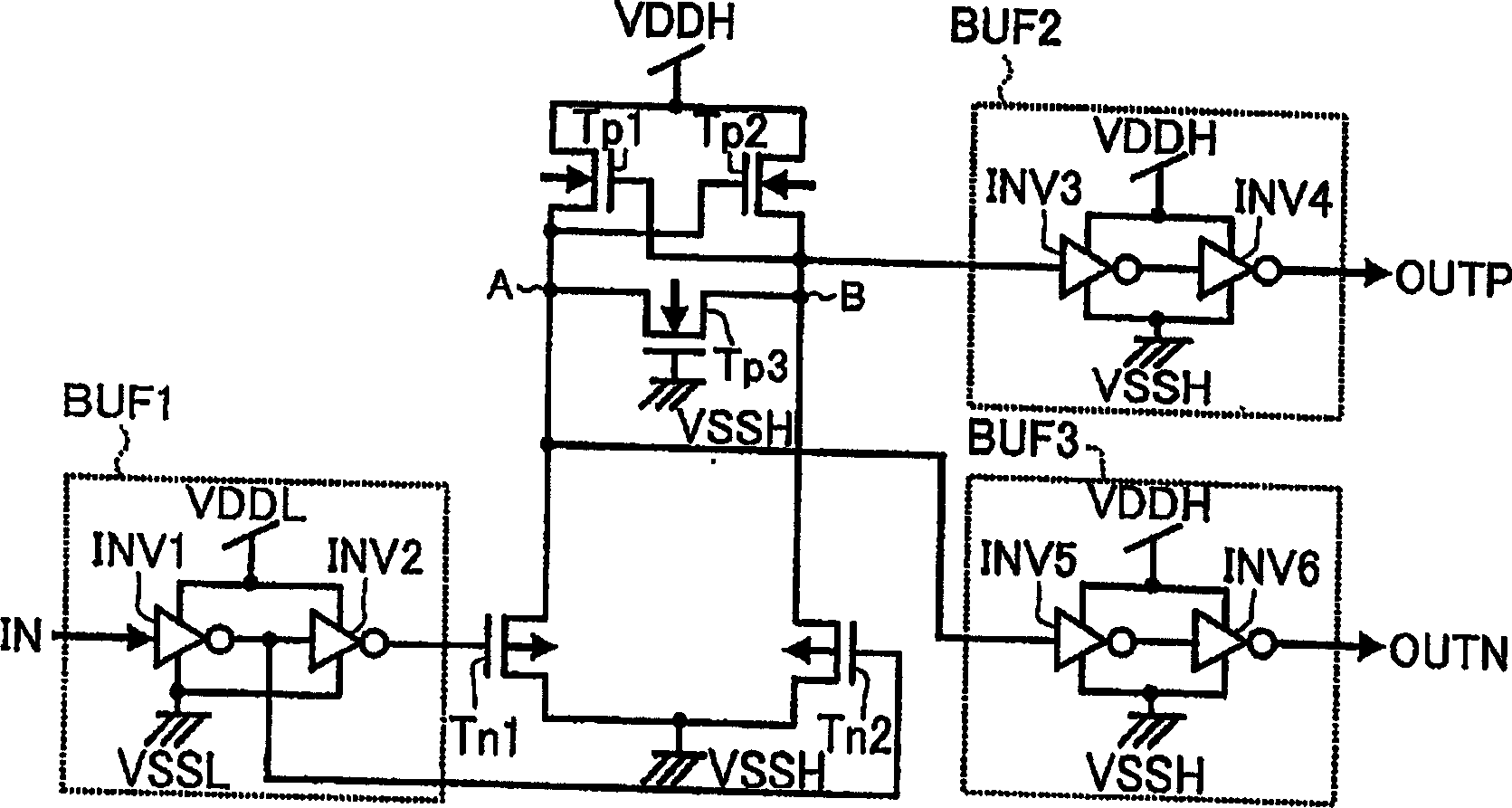

[0061] Next, a level conversion circuit according to Embodiment 3 of the present invention will be described.

[0062] image 3 The configuration of the level conversion circuit of the third embodiment is shown. image 3 The level-shifting circuit shown makes the output signal a differential output signal, with figure 1 The level shifting circuit differs in that, compared to the figure 1 The level conversion circuit is further configured with a buffer BUF3 on the output side.

[0063] The buffer BUF3 on the output side includes two inverters INV5 and INV6 that operate under the high power supply voltage VDDH and the corresponding low power supply voltage VSSH, and the previous stage inverter INV5 is connected to the node A. The output sides of the two buffers BUF2 and BUF3 on the output side are respectively connected to the output terminal OUTP that outputs a signal that is in phase with the input signal IN, and the output terminal OUTN that outputs a signal that is inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More