Electronic carrier board

A carrier board and electronic technology, which is applied in the direction of electrical components, electrical components, printed circuits, etc., can solve the problems of unequal wetted areas, inability to use, and low resolution of photosensitive solder mask, so as to avoid different pad areas Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

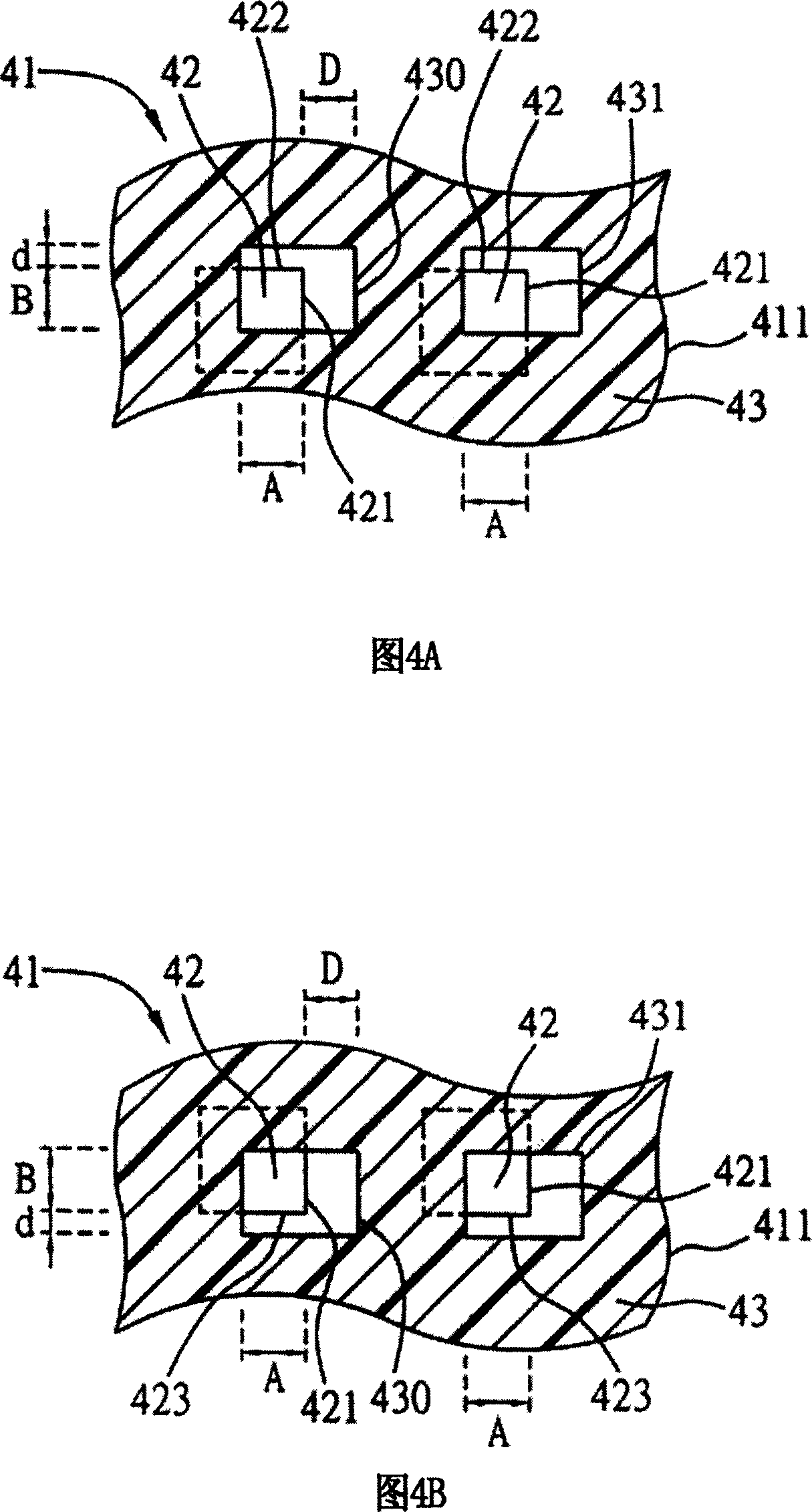

[0051] Please refer to FIG. 4A and FIG. 4B , which are schematic plan views of Embodiment 1 of the electronic carrier board of the present invention.

[0052] The electronic carrier board of the present invention comprises: a main body 411; at least two welding pads 42 arranged in pairs on the surface of the main body 411; and a protective layer 43 for covering the surface of the main body, the protective layer 43 corresponding to the two Openings 430 and 431 are formed at the position of the first welding pad 42. The openings 430 and 431 are in the same direction as each other and expose two identical first side walls 421 of the second welding pad 42 with a width of B and the first side wall 421 of the width A. The two side walls 422 (or the third side wall 423) form a pair of welding pads whose exposed area is A*B. The first side wall 421 of the welding pad is arranged vertically to the pair of welding pads 42. The direction of the second side wall 422 (or the third side wal...

Embodiment 2

[0058] Please refer to FIG. 5 , which is a schematic plan view of Embodiment 2 of the electronic carrier board of the present invention.

[0059] The electronic carrier board of Embodiment 2 of the present invention is substantially the same as the above-mentioned Embodiment 1, the main difference is that the protective layer 43 on the electronic carrier board 41 is corresponding to at least two openings 430 and 431 formed between the welding pads 42 arranged in pairs, The openings 430 and 431 are in the same direction as each other and expose three identical first sidewalls 421, second sidewalls 422 and third sidewalls 423 of the two welding pads 42. The first sidewalls 421 of the welding pads are vertical. The direction in which the pair of welding pads 42 are arranged, the second sidewall 422 and the third sidewall 423 are parallel to the direction in which the pair of welding pads 42 are arranged, and the distance D between the first sidewall 421 and the openings 430 and 43...

Embodiment 3

[0063] Please refer to FIG. 6A , which is a schematic plan view of Embodiment 3 of the electronic carrier board of the present invention.

[0064] The electronic carrier board of Embodiment 3 of the present invention is substantially the same as the above-mentioned Embodiment 1, the main difference is that the protective layer 43 on the electronic carrier board 41 is corresponding to at least two openings 430 and 431 formed between the welding pads 42 arranged in pairs, The openings 430 and 431 are in the same direction as each other and fully expose the same first sidewall 421, second sidewall 422, third sidewall 423 and fourth sidewall 424 of the two pads 42, wherein the first, second sidewall 423 and fourth sidewall 424 are identical. The fourth sidewalls 421, 424 are perpendicular to the direction in which the pair of welding pads 42 are arranged, the second and third sidewalls 422, 423 are parallel to the direction in which the pair of welding pads 42 are arranged, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More