Debug in a multicore architecture

A thread and debugger technology, which is used in the field of debugging multi-threaded programs and systems executed in a multi-core architecture, and can solve problems such as poor portability and hardware-specific applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

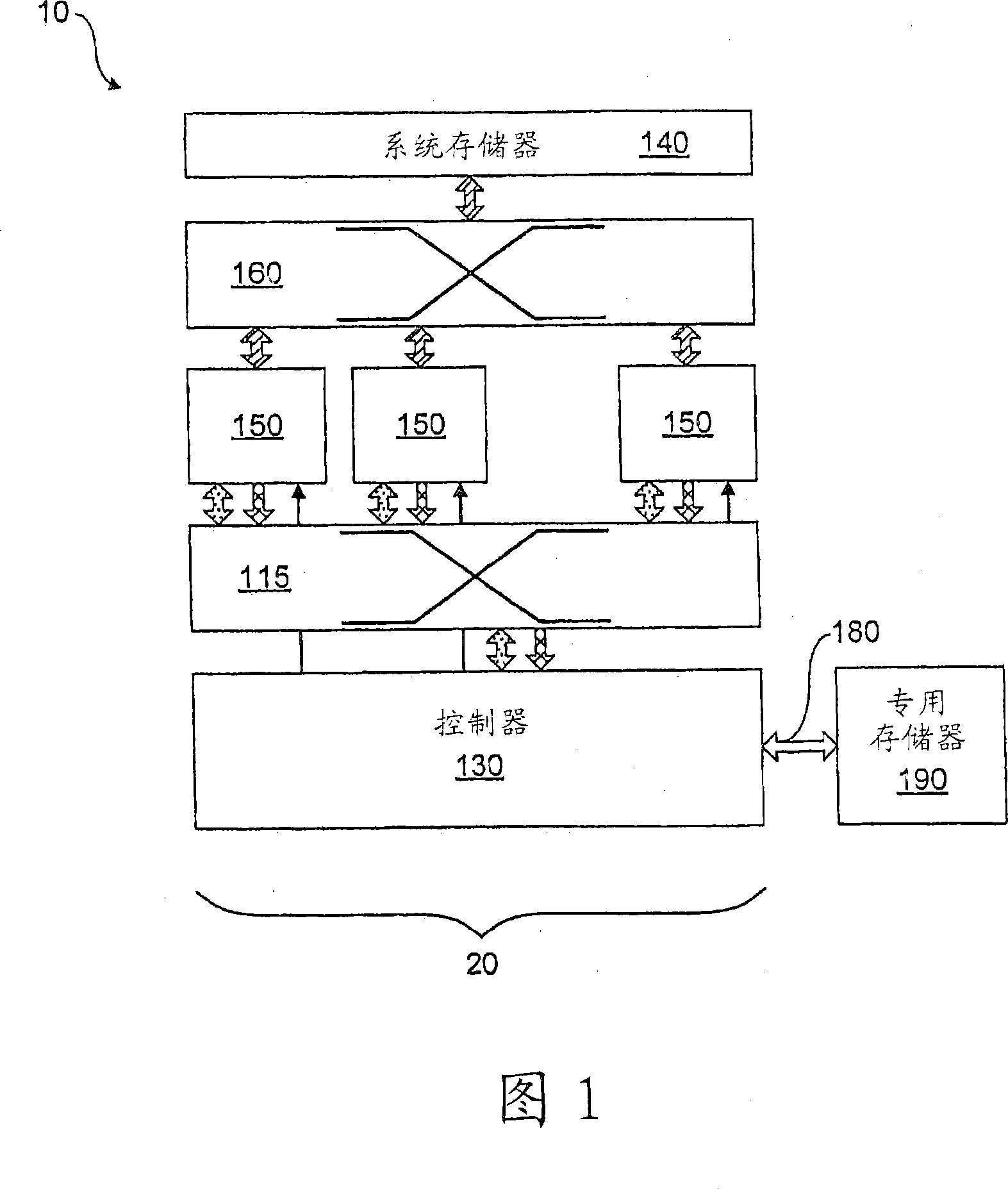

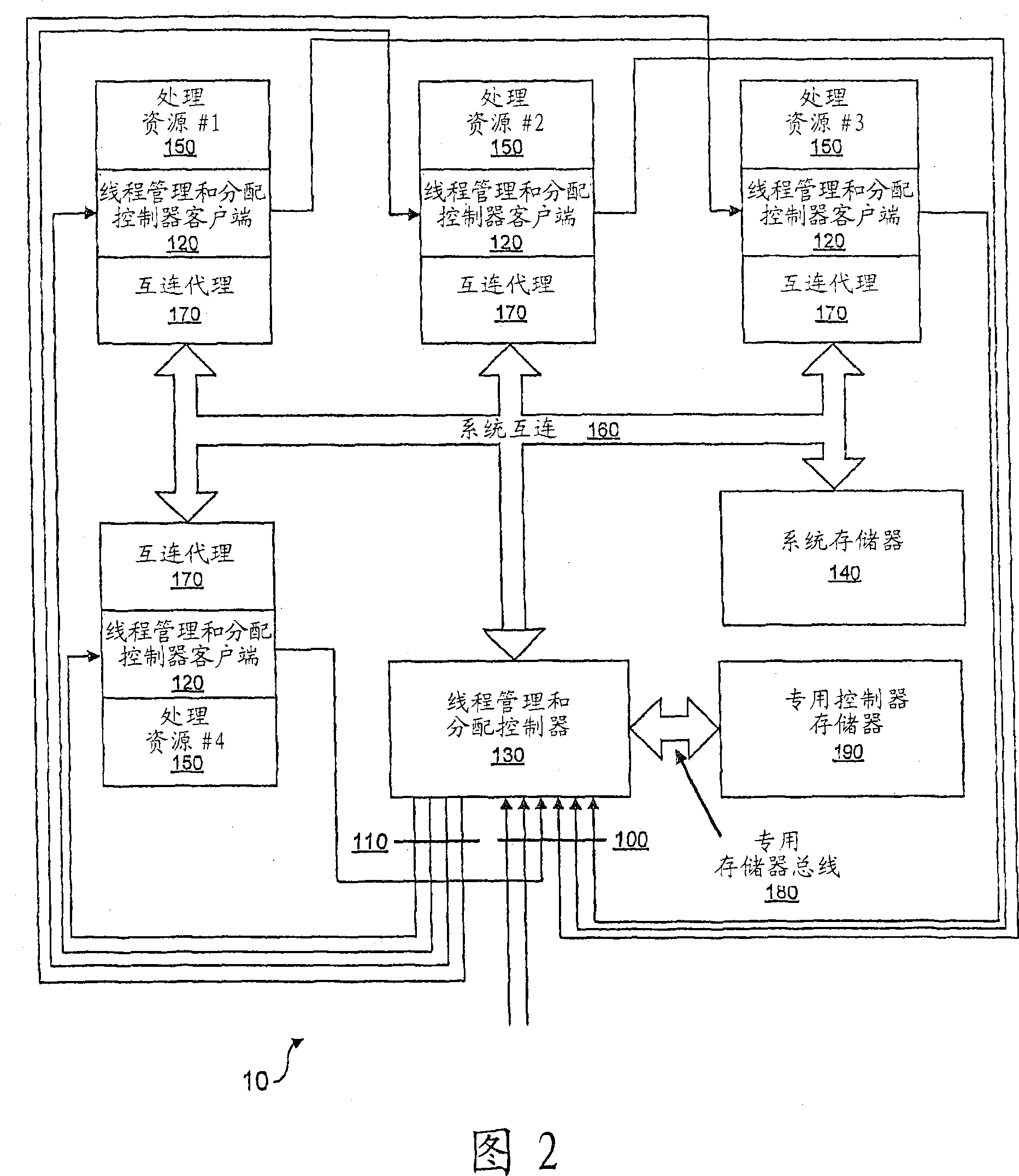

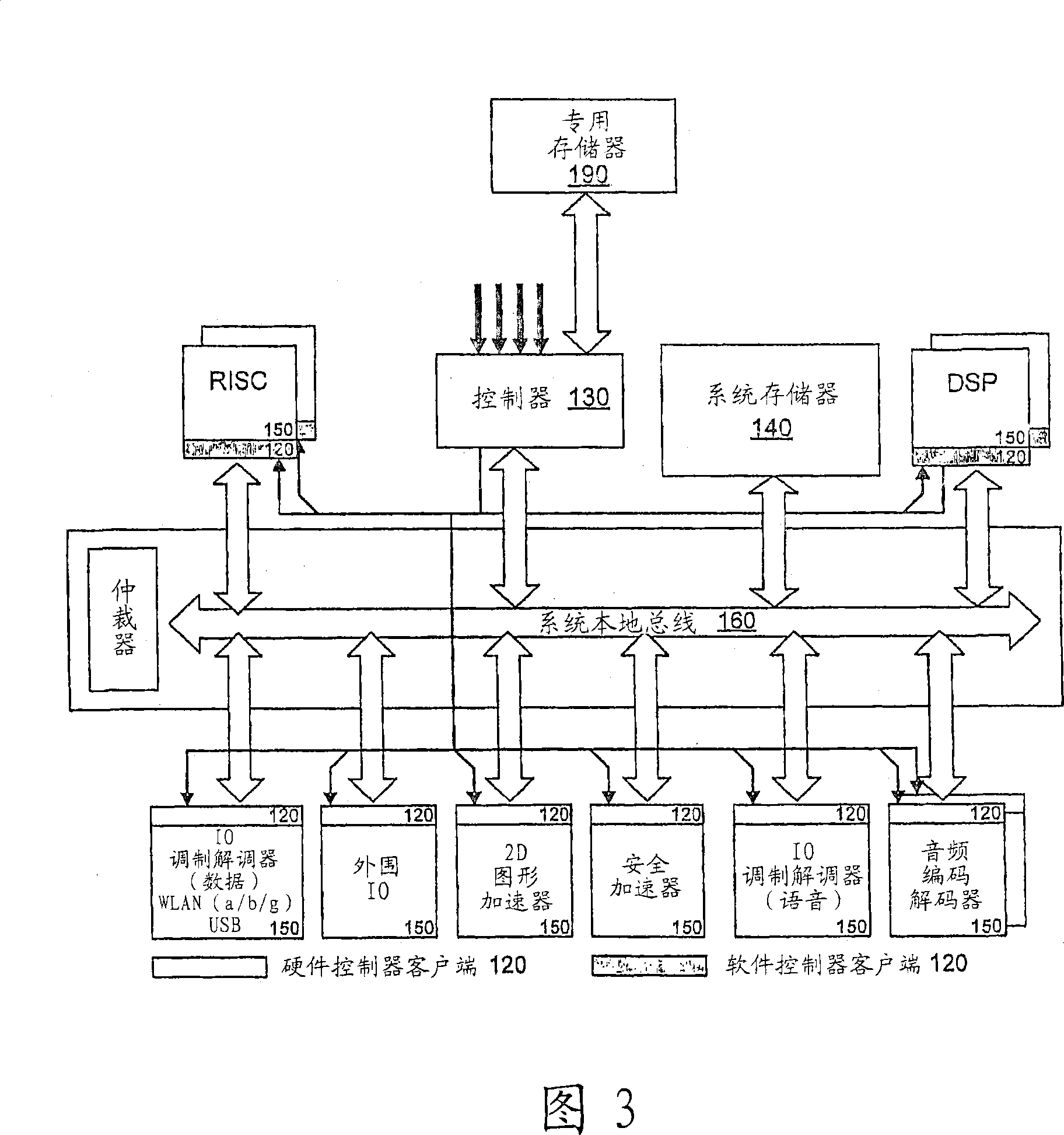

[0034] Figure 1 shows a logical view of the system framework of an example of a typical multi-core processor architecture. The framework includes a plurality of processing resources 150, each of which may or may not be similar to other processing resources 150 in the multi-core architecture. The processing resource 150 may be any form of hardware or its equivalent capable of executing instructions, and thus may include a general-purpose processing resource 150, or a processing resource 150 with an effectively restricted instruction set, such as an input-output device.

[0035] The system framework also includes a centralized thread management and allocation system comprising a thread management and allocation controller 130 and a dedicated tightly coupled memory 190 connected to the controller via a memory interface 180 . Each processing resource 150 can access controller 130 through interconnect 115 . It should be understood that implementation of the architecture of FIG. 1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More