Testing structure for MOS capacitor and location method for failure point

A technology of capacitance testing and positioning method, which is applied in the direction of electronic circuit testing, non-contact circuit testing, semiconductor/solid-state device testing/measurement, etc., can solve the problems of labor-intensive, cost-increased, time-consuming, etc., and achieve simple manufacturing process and increase Production cost, the effect of avoiding repeated cutting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

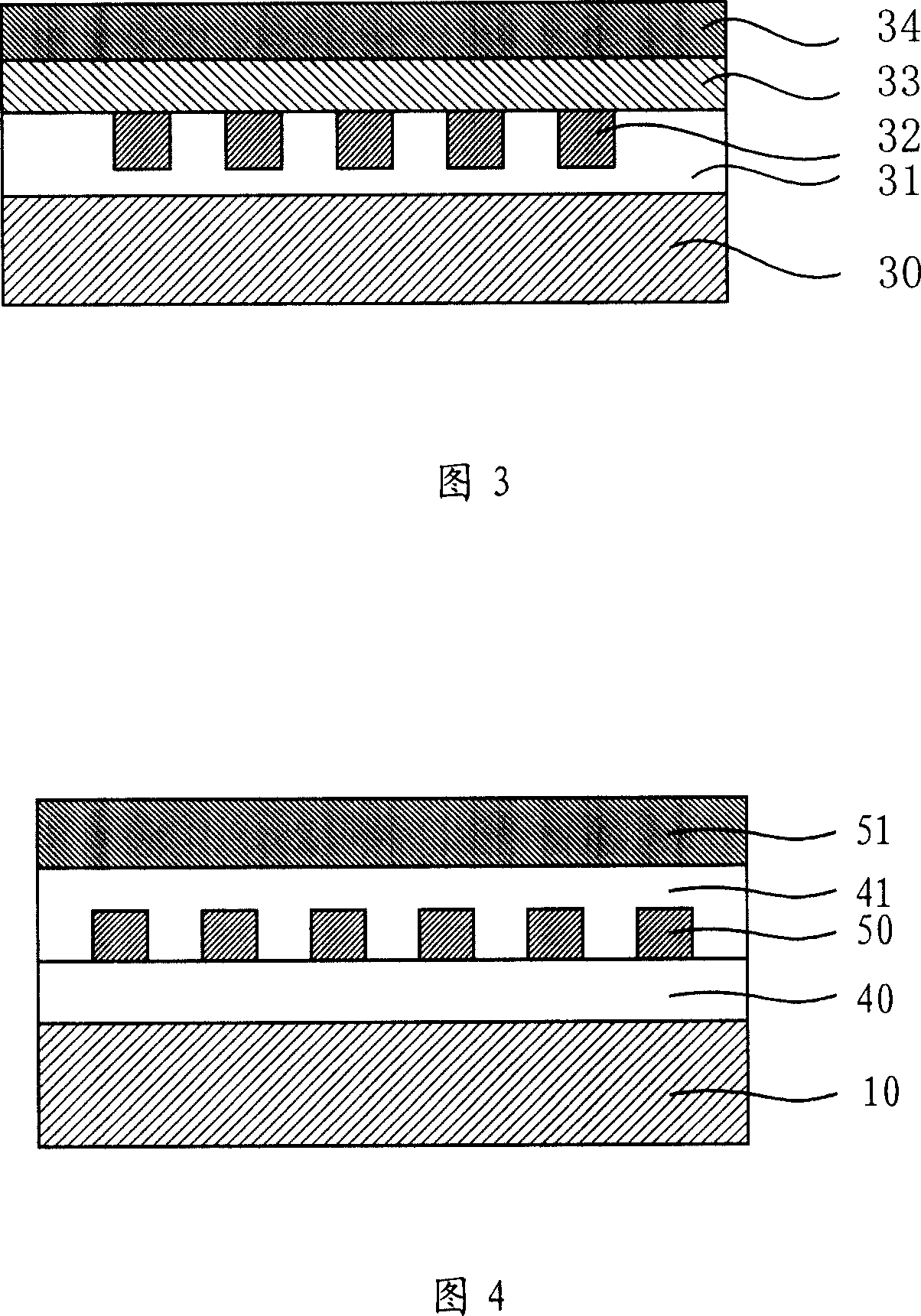

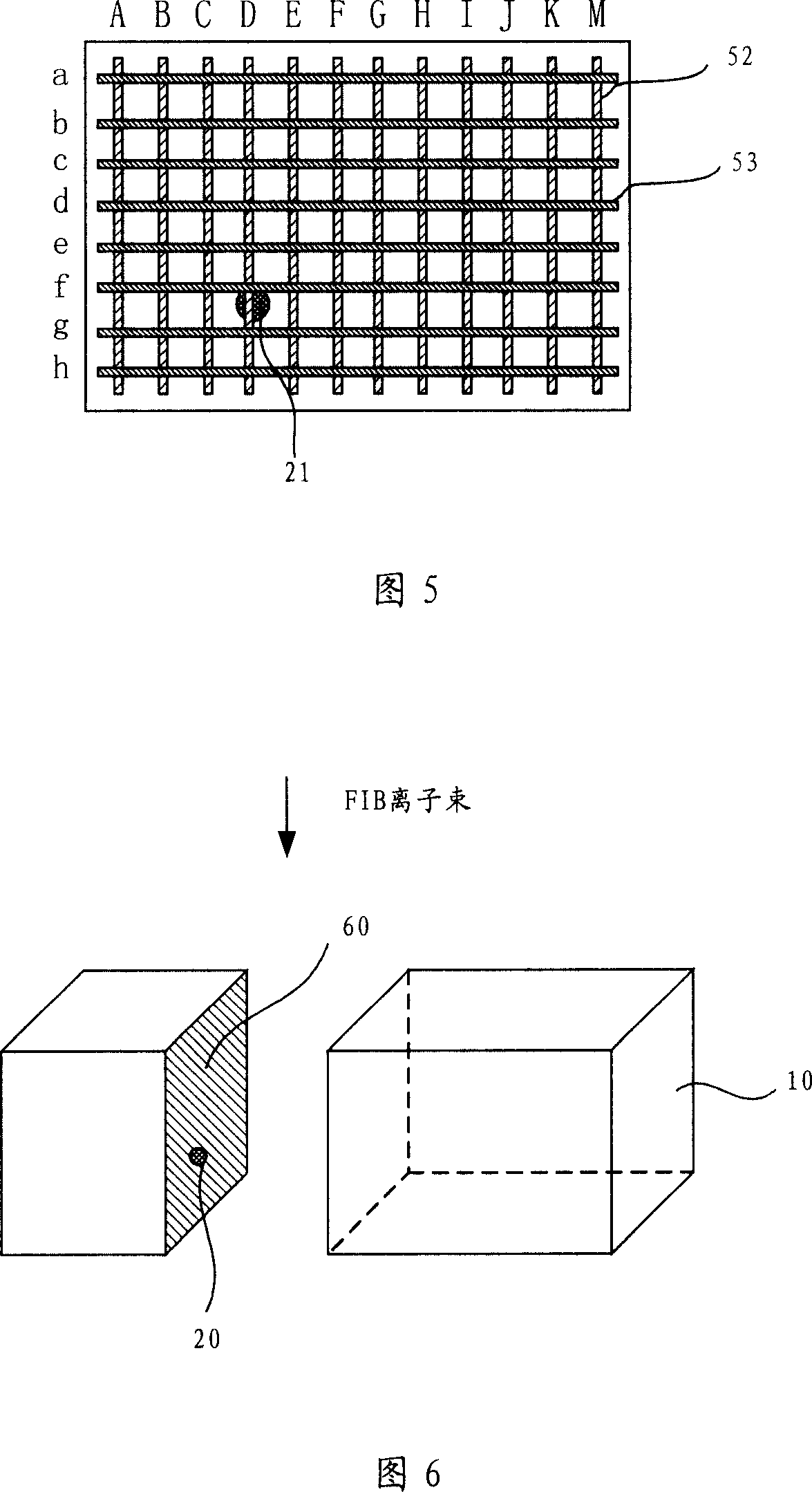

[0044] As the first embodiment illustrating the method of the present invention, the specific implementation steps of applying the method of the present invention to locate the failure point and perform failure analysis are:

[0045] First, a test MOS capacitor is formed.

[0046] The test MOS capacitor is formed simultaneously with the normal product and has the same structure; the test MOS capacitor is formed on the dicing line in the wafer; for the convenience of failure point detection, the test MOS capacitor grid size can be designed to be large enough, as the method of the present invention In an embodiment, the gate size of the test MOS capacitor is selected as: 50 microns*50 microns.

[0047] Admittedly, the determination of the gate size of the test MOS capacitor is a special choice made for the convenience of describing the specific embodiments of the present invention, and should not be used as a limitation to the implementation of the method of the present inventio...

no. 2 example

[0064] As the second embodiment of the present invention, the specific implementation steps of applying the method of the present invention to locate the failure point and perform failure analysis are as follows:

[0065] First, a test MOS capacitor is formed.

[0066] The test MOS capacitor is formed simultaneously with the normal product and has the same structure; the test MOS capacitor is formed on the dicing line in the wafer; for the convenience of failure point detection, the test MOS capacitor grid size can be designed to be large enough, as the method of the present invention In an embodiment, the gate size of the test MOS capacitor is selected as: 50 microns*50 microns.

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap