Methods of manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as damaged devices, wafer damage, process loss, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In order to make the above and other objects, features, and advantages of the present invention more comprehensible, the preferred embodiments are listed below, together with the accompanying drawings, and are described in detail as follows:

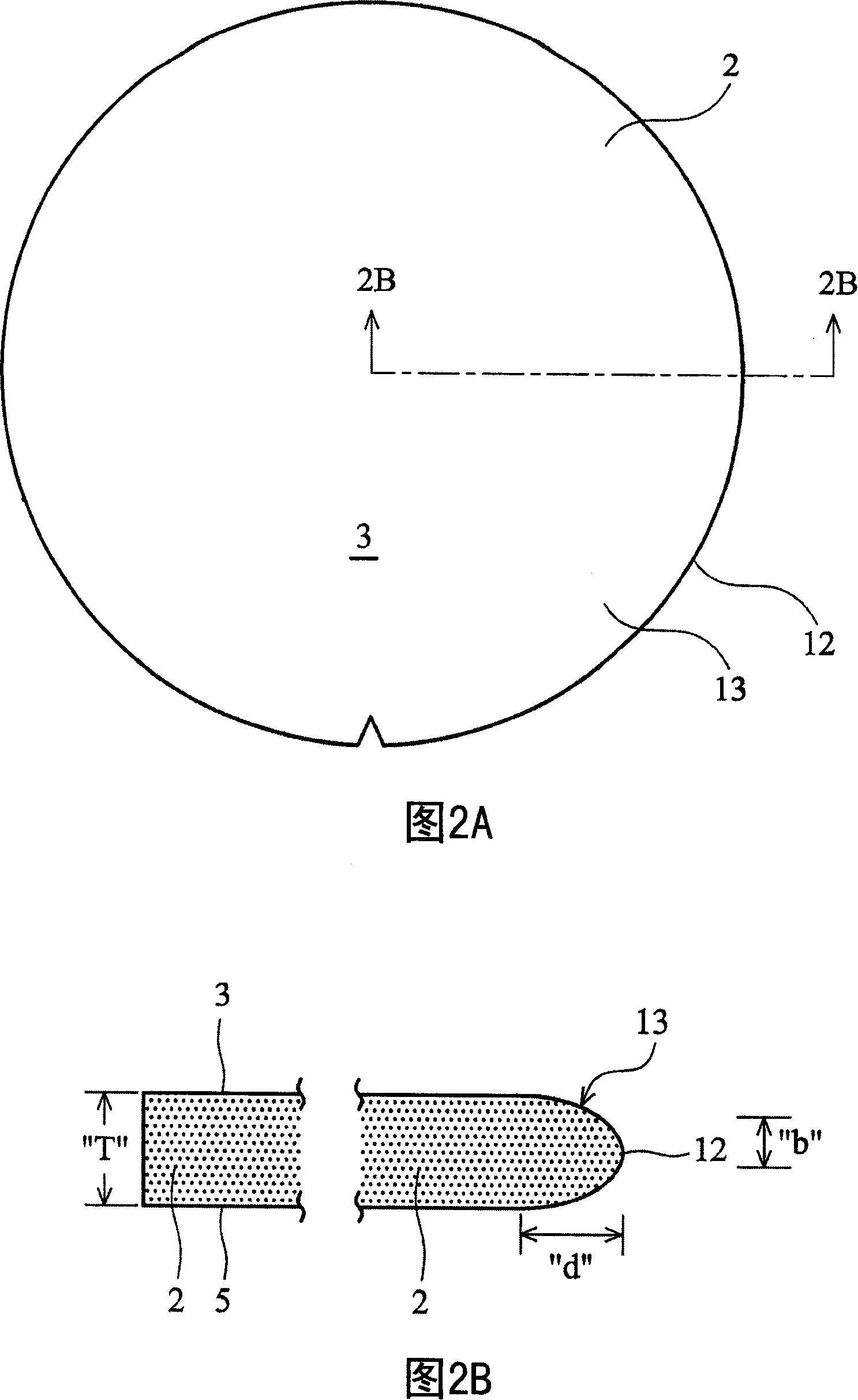

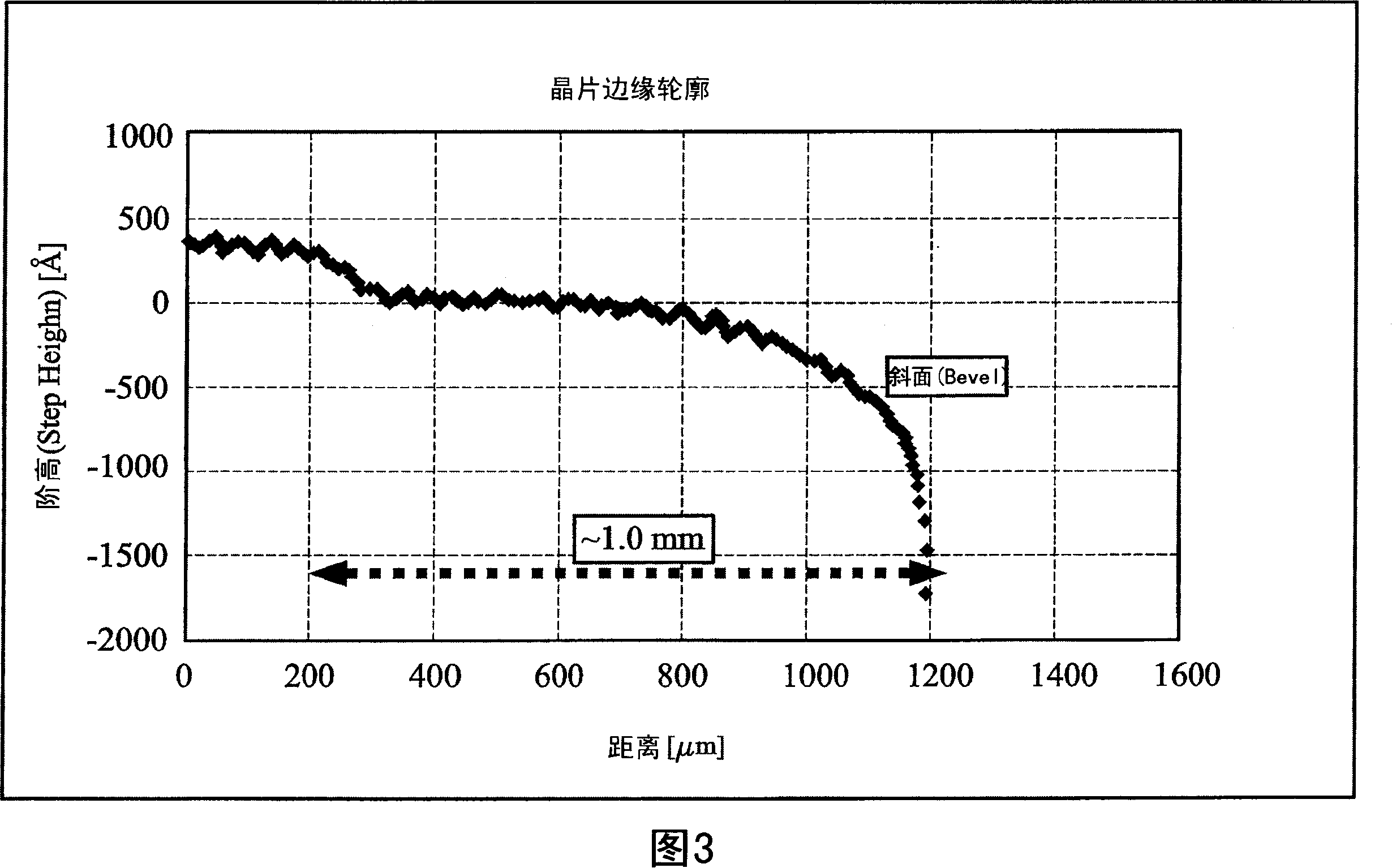

[0051]In an embodiment of the present invention, a process method is disclosed, which can reduce the problem of semiconductor wafer chipping caused by the step of wafer thinning in the process of back photosensitive CMOS device. Specifically, the first embodiment discloses trimming the edge portion of the wafer circumference before the wafer thinning process, and the trimming process can be performed before or after the wafer is connected to a carrier substrate.

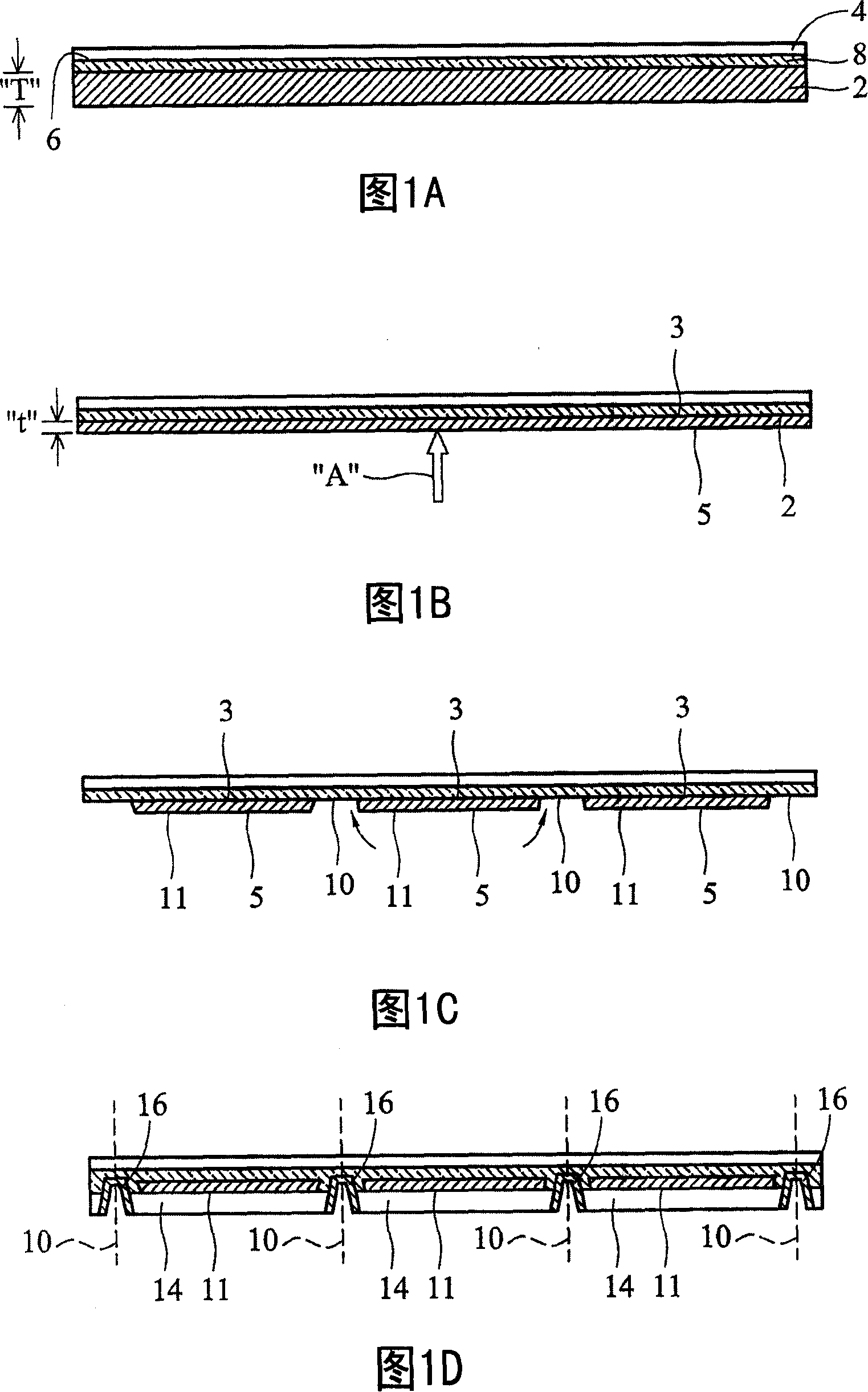

[0052] Please refer to FIGS. 1A-1D , which are a series of schematic cross-sectional views showing a series of exemplary process steps for manufacturing a backside photosensitive CMOS image chip. Figure 1A shows a silicon wafer (semiconductor wafer or CMOS wafer) 2 conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More