Method and device for performing demodulation to digital signal using synchronous clock signal

A technology for synchronizing clock signals and digital signals. It is used in synchronization/start-stop systems, automatic power control, instruments, etc. It can solve problems such as large synchronization clock jitter, poor clock accuracy, and synchronization loop loss, and achieve increased frequency locking. The effect of range, jitter reduction, and effective recovery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

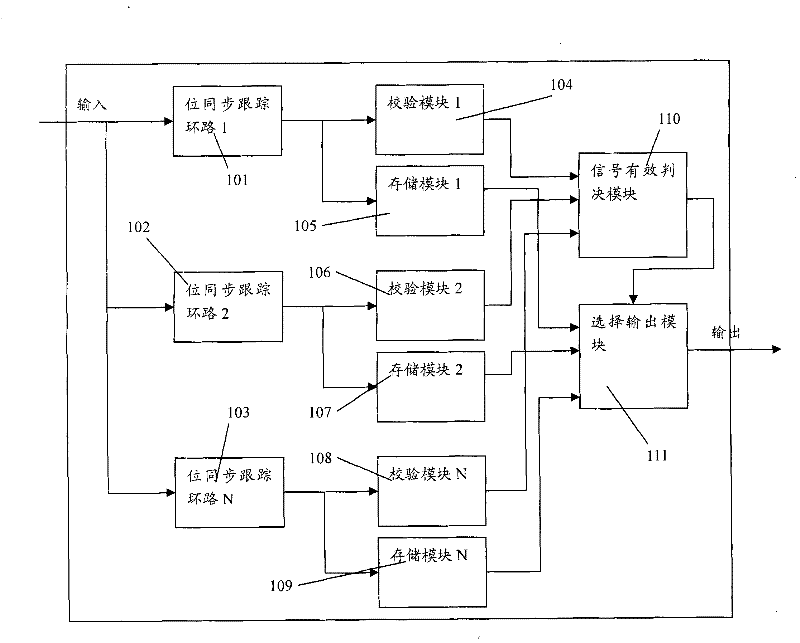

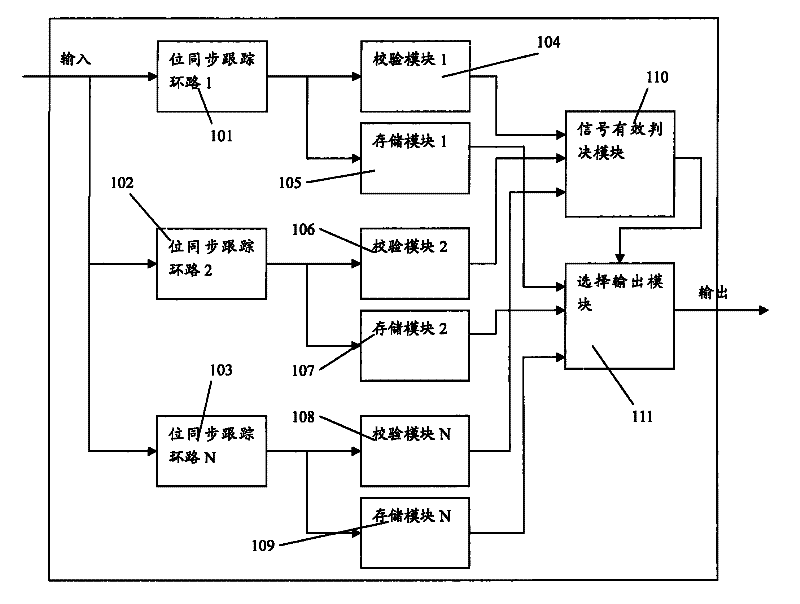

[0029] see figure 1 , which is a structural diagram of a preferred embodiment of a device for demodulating digital signals using a synchronous clock signal in a digital communication system according to the present invention. It can be applied to the bit synchronization recovery of the electronic tag to the reader signal in the RFID system, and can also be applied to other digital communication systems that need bit synchronization recovery.

[0030] As shown in the figure: the device consists of bit synchronous tracking loops 101, 102, 103, verification modules 104, 106, 108, signal valid judgment module 110, and storage modules 105, 107, 109 storing the current transmission of the synchronous tracking loop output The data and selection output module 111 is composed. The functions and connections of each module are:

[0031] N parallel bit synchronous tracking loops 101, 102, 103, they respectively work on overlapping locked frequency ranges to recover bit synchronously fro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More