Method for model building based on changes of integrated circuit manufacture process performance

An integrated circuit and performance technology, which is applied in the field of building models based on changes in integrated circuit process performance, can solve problems such as large errors, inability to accurately reflect changes in process performance, and low efficiency. High mold efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

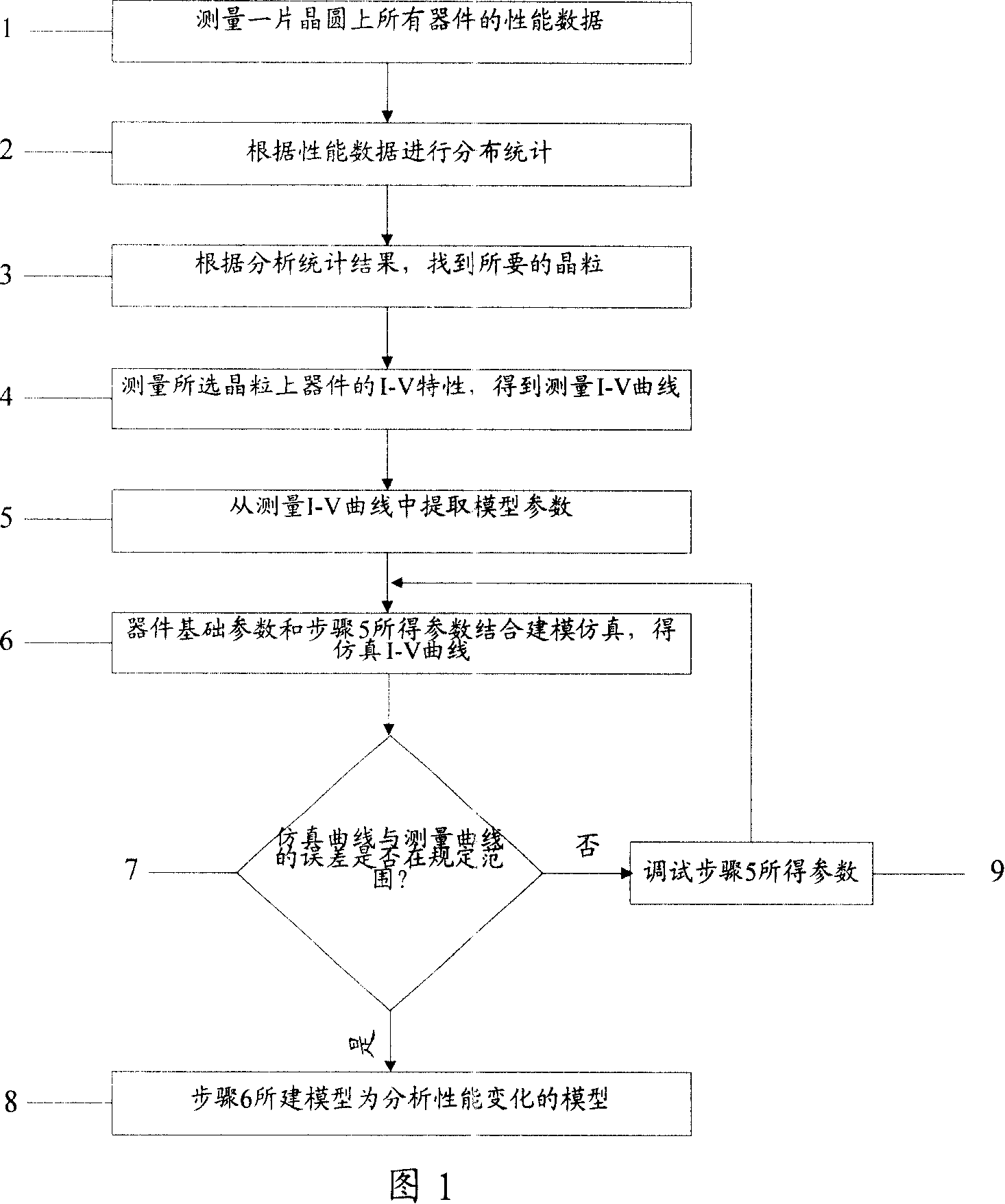

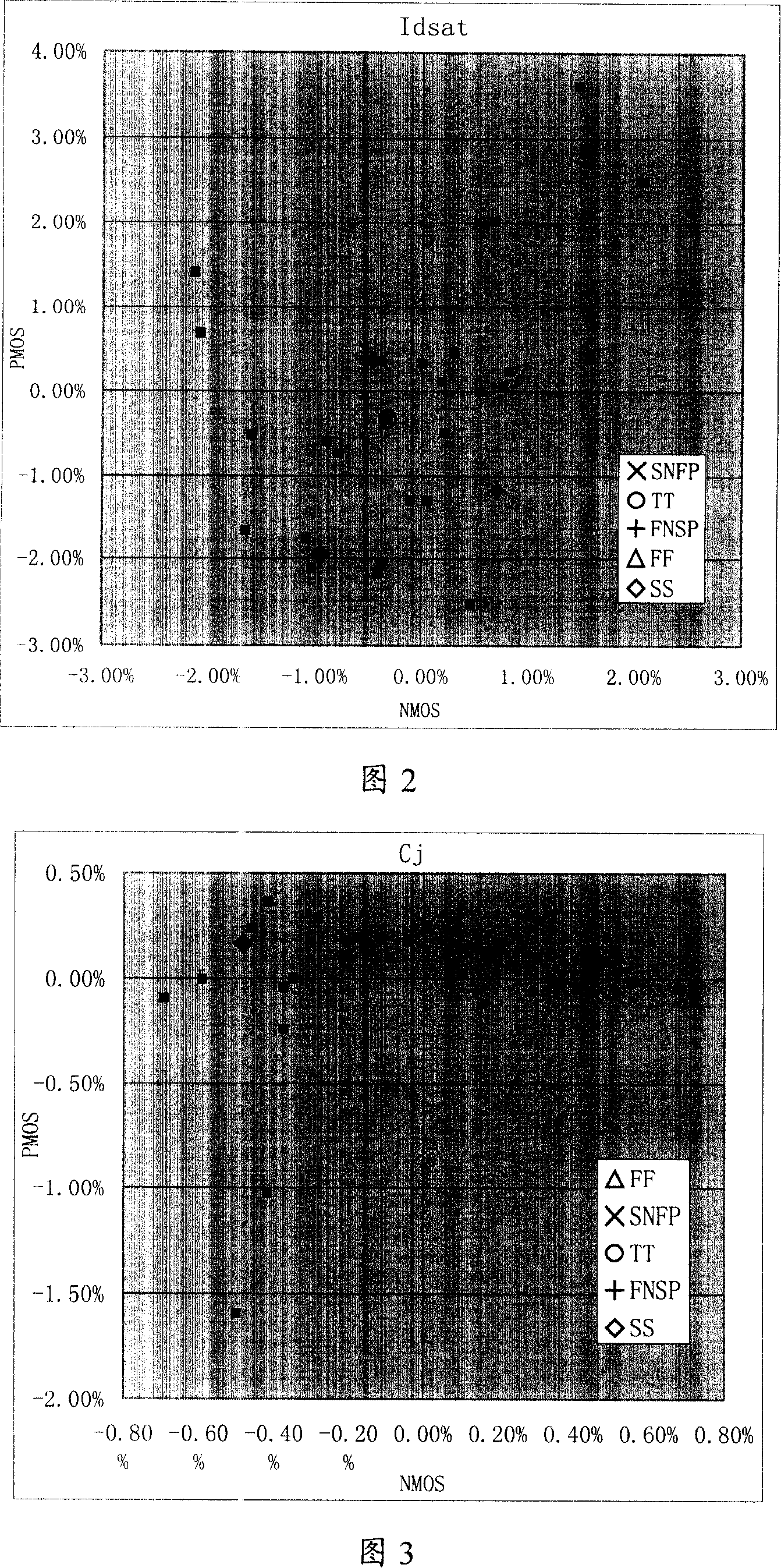

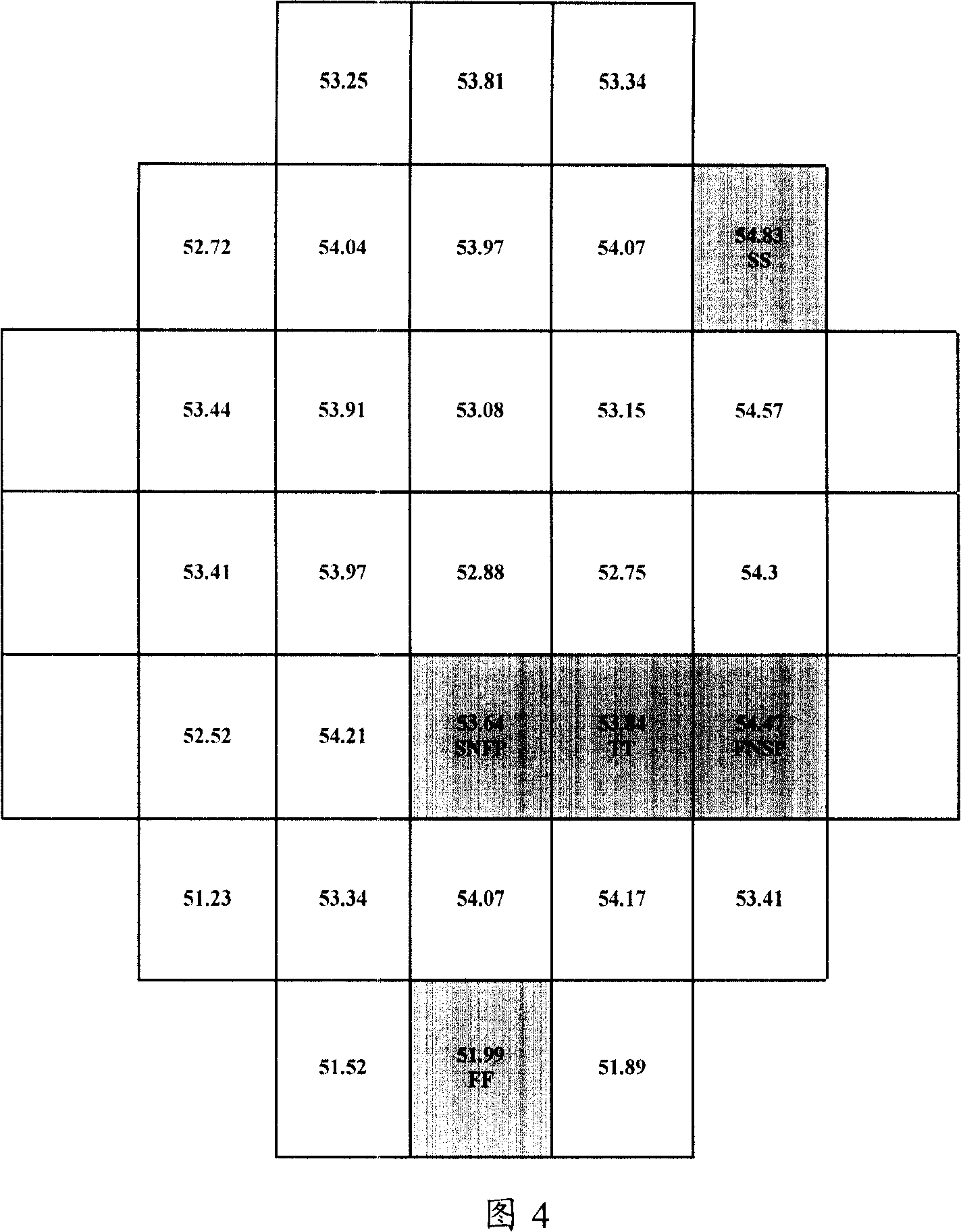

[0015] This embodiment is modeled by the modeling method disclosed in the present invention: measure the performance data of all transistors on the wafer, perform distribution statistics on the performance data to obtain the grains where some of the largest discrete points are located, and measure the I-V of all transistors in the selected grains The characteristics are measured I-V curves, model parameters are extracted from the measured I-V curves, the model parameters are combined with the transistor basic parameters and input into the simulation software for modeling and simulation to obtain simulated I-V curves, and the model parameters are adjusted so that the error between the simulated I-V curve and the measured I-V curve is within Within the specified range, the model used for the simulation curve that finally meets the error requirements is used as the model for performance analysis.

[0016] In this embodiment, one wafer is used. There are 31 crystal grains on the w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More