Multi-chip stack packaging structure with asymmetric conductive wire rack

A technology of chip packaging and stacking structure, applied in the field of multi-chip stacking packaging structure, can solve problems such as electrical signal phase change, metal wire displacement, chip short circuit, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

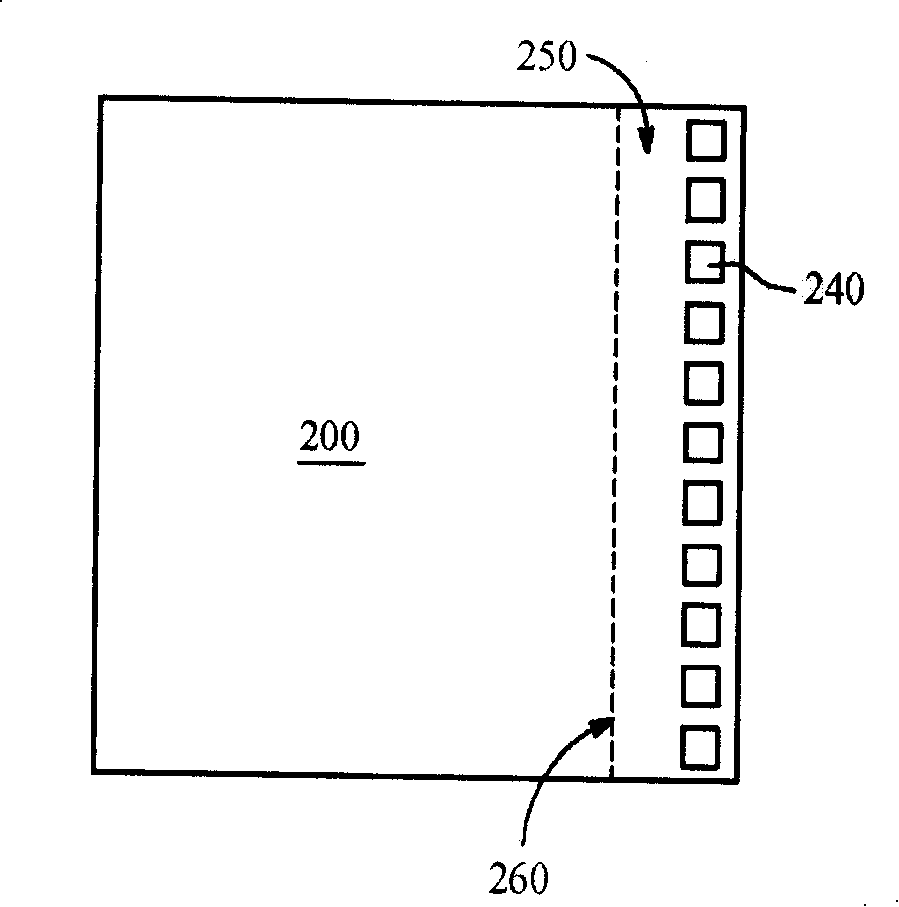

[0073] as reference Figure 2A and Figure 2B As shown, a schematic plan view and a schematic cross-sectional view of the chip 200 that has completed the aforementioned process. Such as Figure 2B As shown, the chip 200 has an active surface 210 and a back surface 220 opposite to the active surface, and an adhesive layer 230 has been formed on the back surface 220 of the chip; it should be emphasized here that the adhesive layer 230 of the present invention is not limited to the aforementioned prepreg. The purpose of the adhesive layer 230 is to form a bond with the substrate or the chip. Therefore, as long as it is an adhesive material with this function, it is an embodiment of the present invention, such as a die attached film.

[0074] Next, please refer to Figure 2C , a schematic cross-sectional view of a multi-chip offset stack structure 30 completed by the present invention. Such as Figure 2C As shown, a plurality of welding pads 240 are arranged on the active sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More