3D chip packaging structure and preparation method thereof

A chip packaging structure, 3D technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of inability to meet the development trend of miniaturization, insufficient integration, high cost, etc., to meet the miniaturization development The needs of the trend, the effect of high packaging integration and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

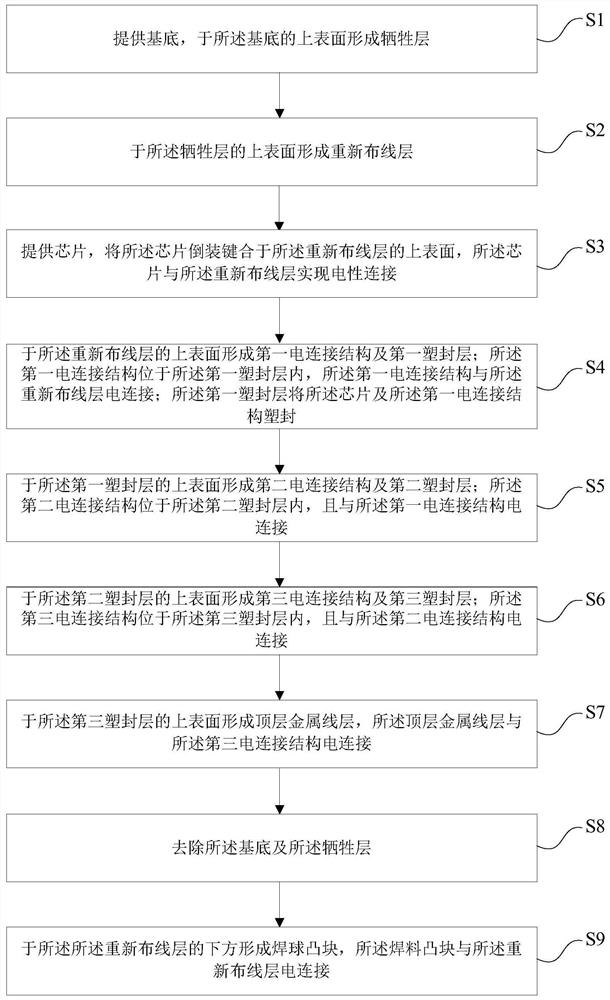

[0080] see figure 1 , the present invention provides a method for preparing a 3D chip packaging structure, the method for preparing the 3D chip packaging structure includes the following steps:

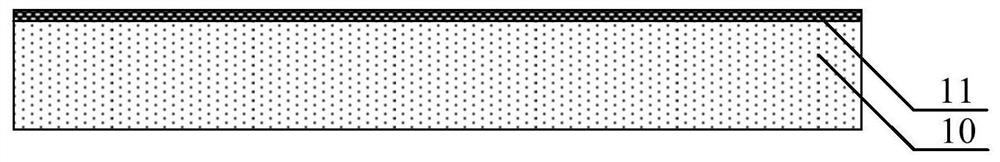

[0081] 1) providing a base, and forming a sacrificial layer on the upper surface of the base;

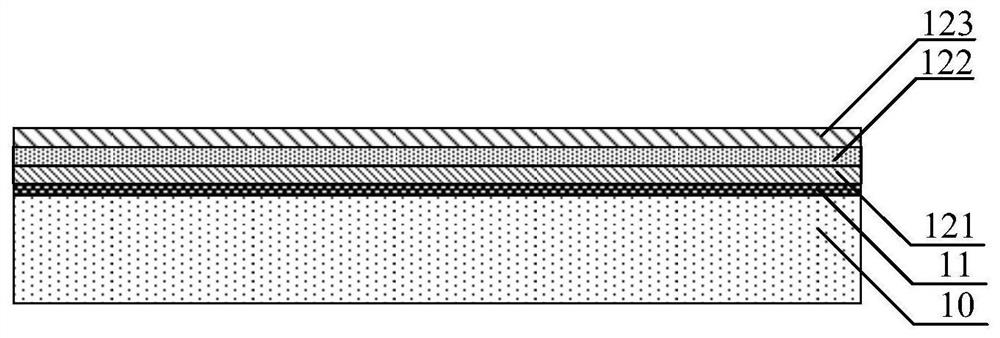

[0082] 2) forming a rewiring layer on the upper surface of the sacrificial layer;

[0083] 3) providing a chip, flip-chip bonding the chip to the upper surface of the rewiring layer, and electrically connecting the chip to the rewiring layer;

[0084] 4) Forming a first electrical connection structure and a first plastic encapsulation layer on the upper surface of the rewiring layer; the first electrical connection structure is located in the first plastic encapsulation layer, and the first electrical connection structure and the redistribution layer The wiring layer is electrically connected; the first plastic sealing layer plastic-seals the chip and the first electrical connection struc...

Embodiment 2

[0147] Please combine Figure 2 to Figure 17 read on Figure 18 , the present invention also provides a 3D chip packaging structure, the 3D chip packaging structure includes: a rewiring layer 12; a chip 13, the chip 13 is flip-chip bonded to the upper surface of the rewiring layer 12, and the The chip 13 is electrically connected to the rewiring layer 12; the first electrical connection structure 14, the first electrical connection structure 14 is located on the upper surface of the rewiring layer 12, and the first electrical connection structure 14 is connected to the The rewiring layer 12 is electrically connected; the first plastic sealing layer 15, the first plastic sealing layer 15 is located on the upper surface of the rewiring layer 12, and the first plastic sealing layer 15 connects the chip 13 and the first electrical The connection structure 14 is plastic-encapsulated; the second electrical connection structure 18, the second electrical connection structure 18 is lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More