Stack type chip package with radiation structure

A chip and multi-chip technology, applied in the field of multi-chip offset stack packaging structure, can solve problems such as the limitation of the number of chip stacks and the inability to further reduce the thickness of the stacked chip packaging structure 100 .

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

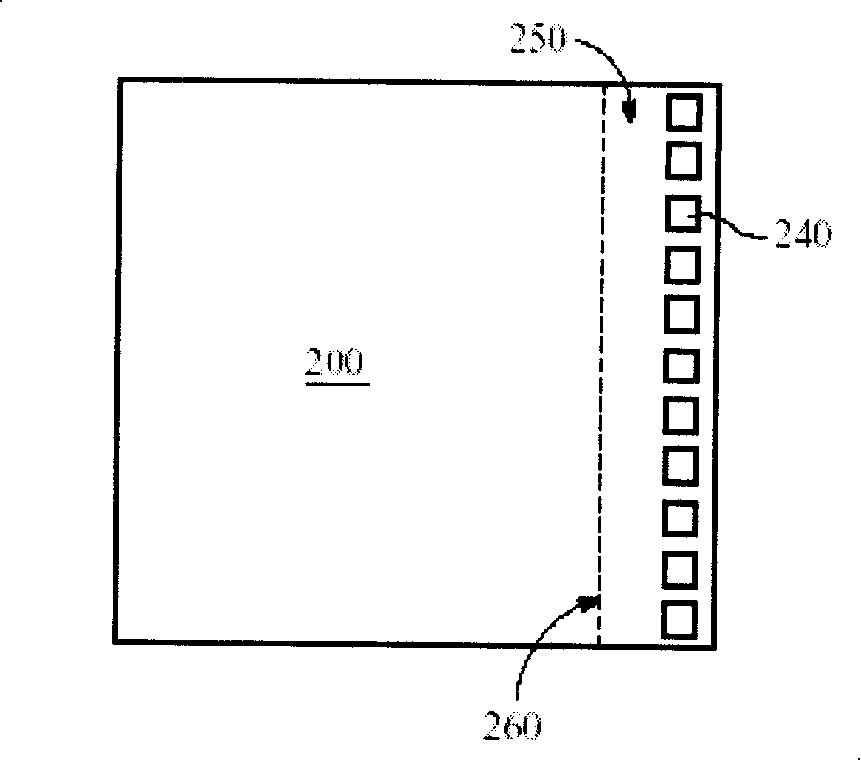

[0074] as reference Figure 2A and Figure 2B As shown, a schematic plan view and a schematic cross-sectional view of the chip 200 that has completed the aforementioned process. Such as Figure 2A As shown, the chip 200 has an active surface 210 and a back surface 220 opposite to the active surface, and an adhesive layer 230 has been formed on the back surface 220 of the chip; it should be emphasized here that the adhesive layer 230 of the present invention is not limited to the aforementioned prepreg. The purpose of the adhesive layer 230 is to form a bond with the substrate or the chip. Therefore, as long as it is an adhesive material with this function, it is an embodiment of the present invention, such as a die attached film. In addition, in the embodiment of the present invention, a plurality of bonding pads 240 are disposed on the active surface 210 of the chip 200, and the plurality of bonding pads 240 have been disposed on the side of the chip 200, therefore, the wir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More