Multi-position quasi memory cell operation method

A technology of storage unit and operation method, which is applied in information storage, static memory, read-only memory, etc., and can solve problems such as low initial voltage, multiple leakages, and difficulty in accurately controlling injected electrons.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

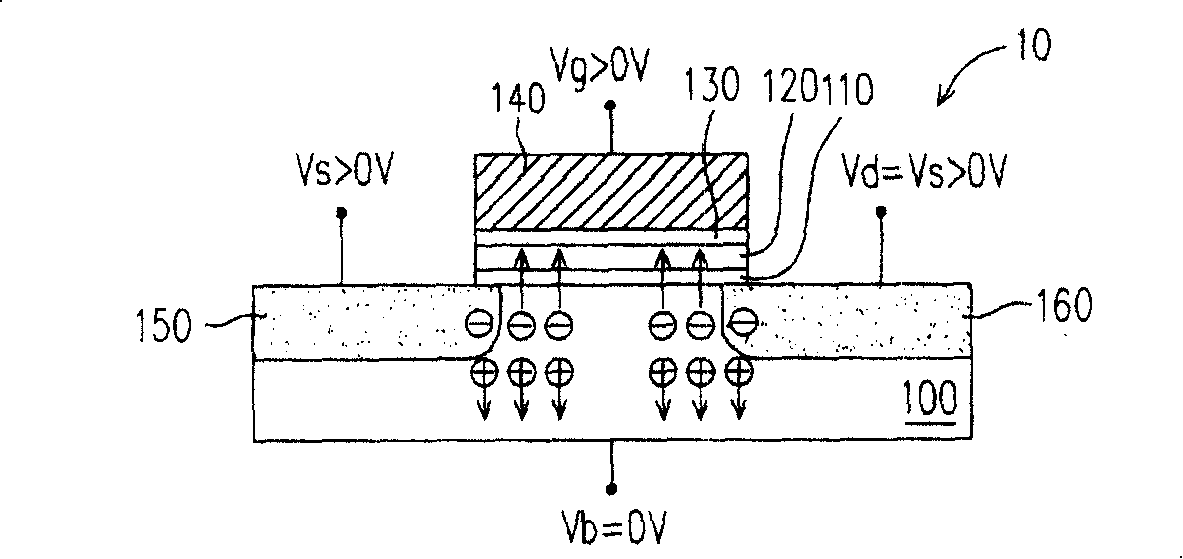

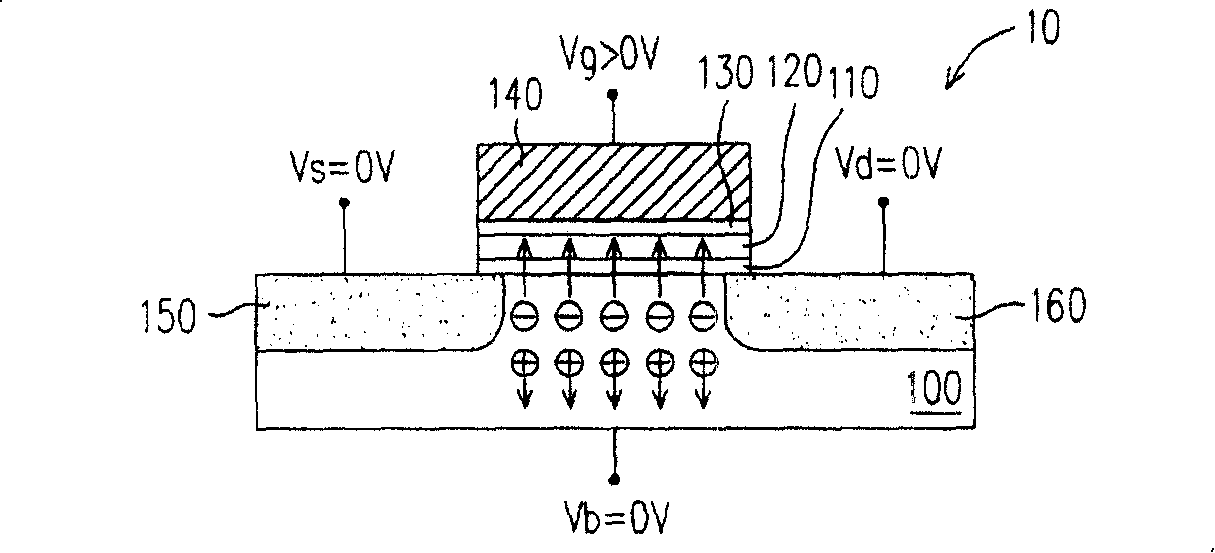

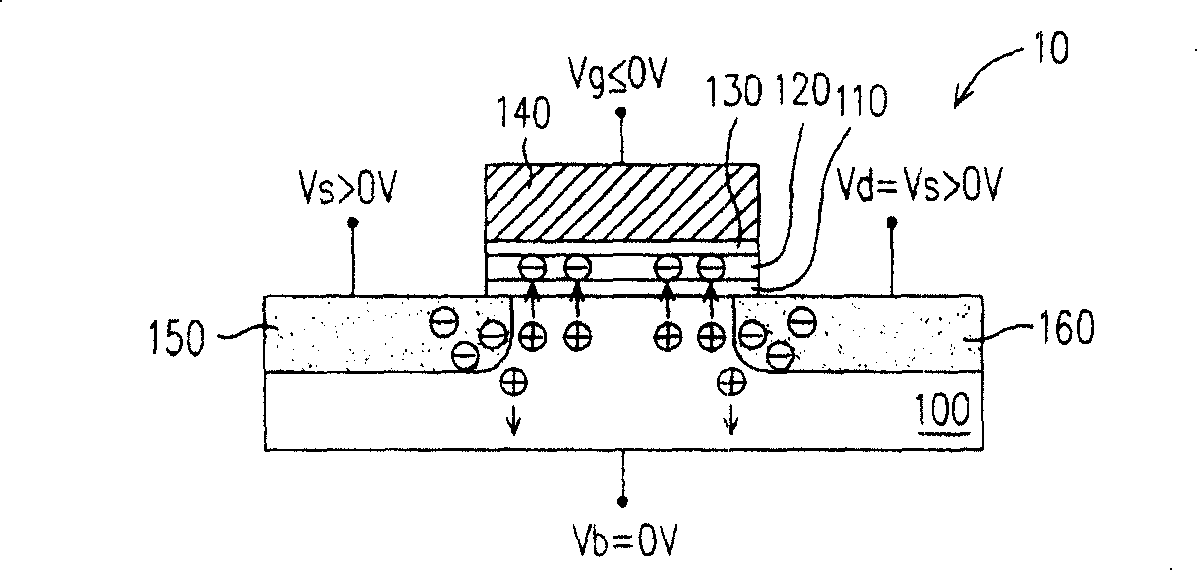

[0020] First of all, it should be noted that although the following embodiments are based on the case where the first conductivity type is P-type, the second conductivity type is N-type, the first-type charges are electrons, and the second-type charges are holes, but with this A person skilled in the art should be able to infer from the description of this embodiment that the multi-level memory cell operating method of the present invention is also applicable to applications where the first conductivity type is N-type, the second conductivity type is P-type, and the first type of charge is electric. hole and the second type of charge is an electron.

[0021] In addition, the charge storage layer in the memory cell to which the operation method of the multi-level memory cell of the present invention is applicable is, for example, a floating gate, a charge-trapping layer or a nano-crystal layer. The material of the floating gate is usually doped polysilicon, the material of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com