A high voltage N-type MOS transistor and the corresponding manufacturing method

A technology of semiconductor tubes and oxides, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as incompatibility, achieve good compatibility, improve overall life, and reduce hot carrier injection. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

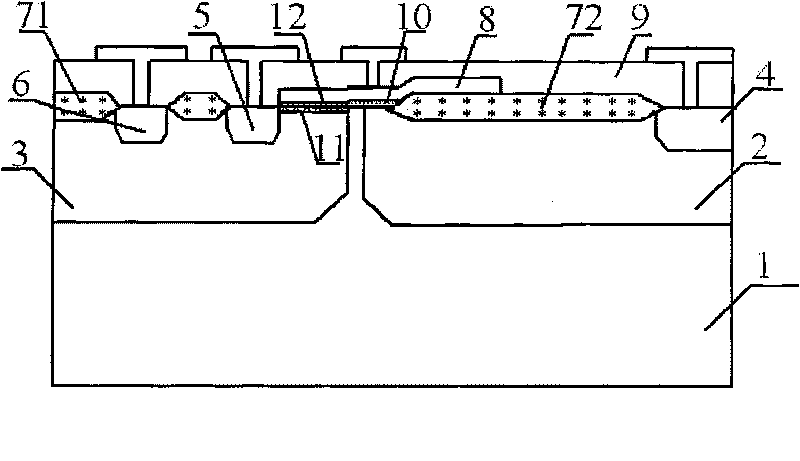

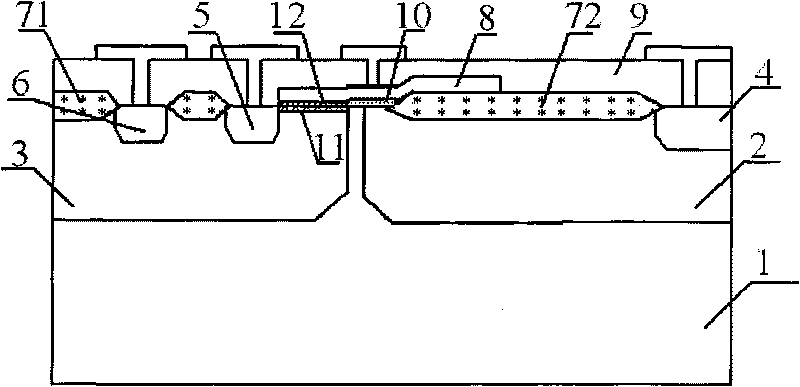

[0014] A high-voltage N-type metal oxide semiconductor tube, comprising a P-type substrate 1, a P-type well 3 and an N-type drift region 2 are arranged on the P-type substrate 1, and a P-type contact hole is arranged on the P-type well 3 6. N-type source 5 and field oxide layer 71, N-type drain 4 and field oxide layer 72 are provided on N-type drift region 2, and P-type well 3, N-type drift region 2 and part of P-type substrate 1 A gate oxide layer is provided above and the gate oxide layer is located between the N-type source 5 and the field oxide layer 72 on the N-type drift region 2. A polysilicon gate 8 is provided on the gate oxide layer and the polysilicon gate 8 extends to the N-type On the field oxide layer 72 on the drift region 2, on the field oxide layer 71 on the P-type well, the P-type contact hole 6, the N-type source 5, the polysilicon gate 8, and the field oxide layer 72 on the N-type drift region (2) And the N-type drain 4 is provided with an oxide layer 9, th...

Embodiment 2

[0016] A method for preparing a high-voltage N-type metal oxide semiconductor tube. First, select a P-type substrate, prepare a P-type well and an N-type drift region on the P-type substrate, and then prepare a field oxide layer, and then perform thick gate oxidation. The growth of the thick gate oxide layer and the etching of the thick gate oxide layer are performed at the same time as the P-type impurity implantation region under the thin gate oxide region, and then a thin gate oxide layer is grown on the P-type impurity implantation region, and then the growth and etching of the polysilicon gate , followed by the source and drain implantation and the substrate contact implantation area, and finally the lead hole, the preparation and passivation treatment of the aluminum lead. The entire process can be realized on the basis of standard epitaxial low-voltage metal-oxide-semiconductor process lines.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More