4-level logic decoder

A decoder and level technology, applied in the field of multi-level logic, can solve problems such as complex design, timing verification, and hindering modeling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The invention can be modified through various modifications and alternative forms, some specific examples of which will be shown and described in detail by way of example shown in the drawings. It should be understood, however, that the intention is not to limit the invention to the particular embodiments described. On the contrary, the invention covers all modifications, equivalents, and alternatives falling within the spirit and scope of the invention as defined by the appended claims.

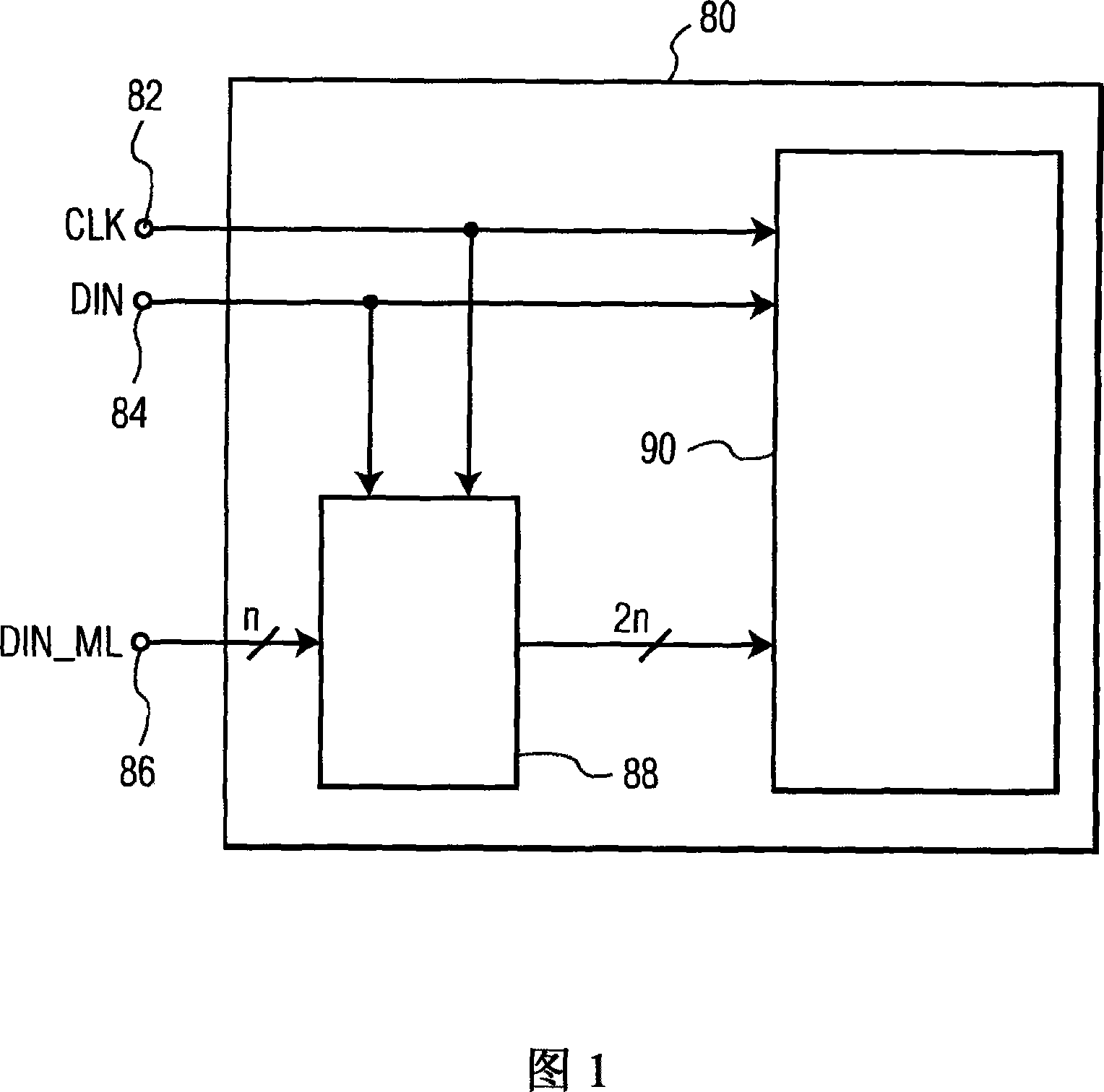

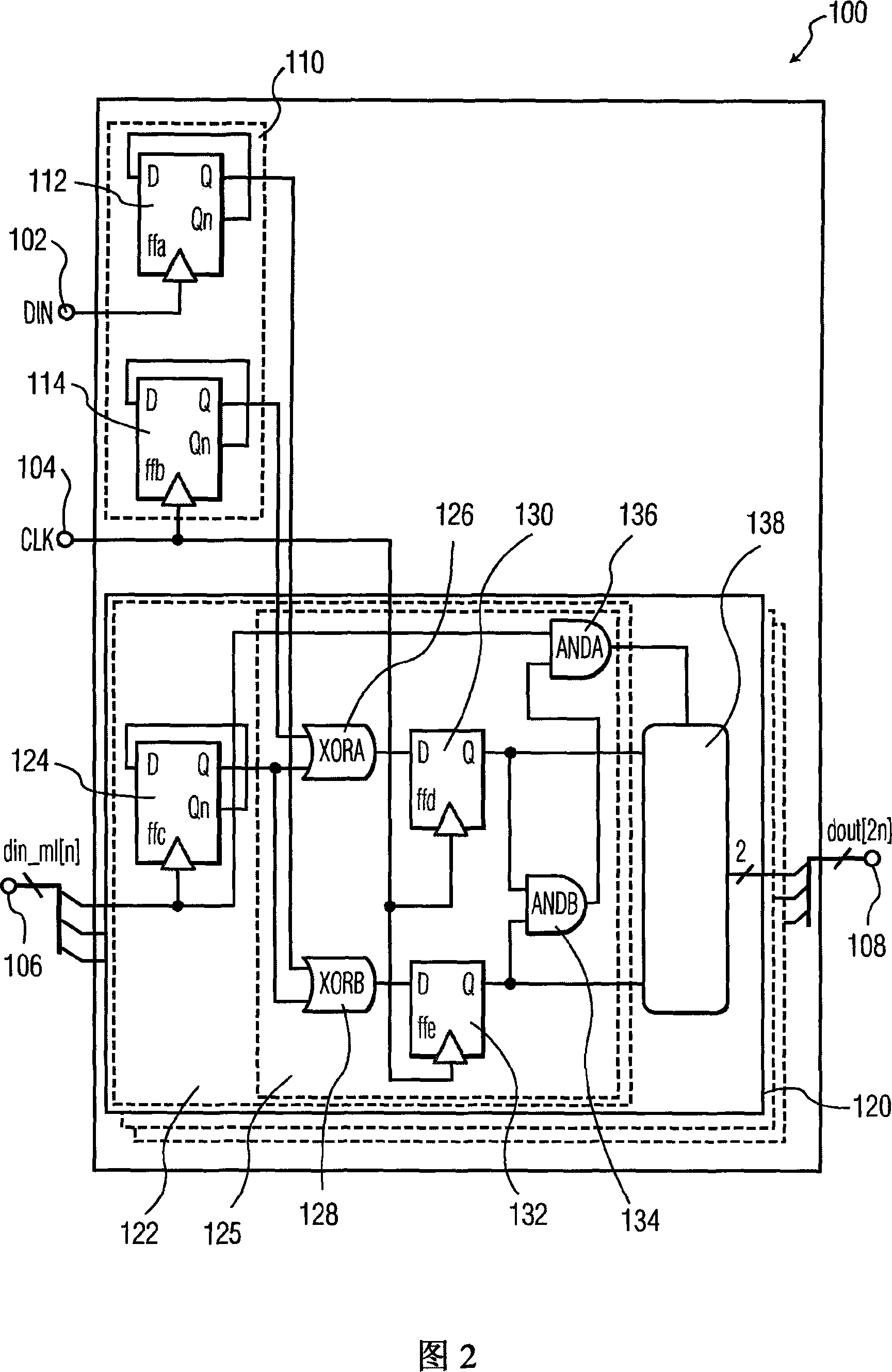

[0014] Traditional digital circuits only use high or low levels to represent the binary value '1' or '0' in the data bit. In this case, n bits can be used to represent a 2n-bit number. In multi-level logic, the number of levels used for data transmission in a single data channel is p, and p>2. For example, in a circuit powered by a 4V power supply, p=4, and levels 4V, 3V, 2V, and 1V are used for single-channel data transmission. This enables an n-channel data bus to represent 4n bit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com