An extraction device and method for synchronous clock

A technology of synchronous clock and extraction device, which is applied in the direction of TV, automatic power control, color TV parts, etc., can solve the problems of affecting PLL work, PLL out of lock, and inability to obtain pixel clock, etc., to achieve the effect of eliminating pulse interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

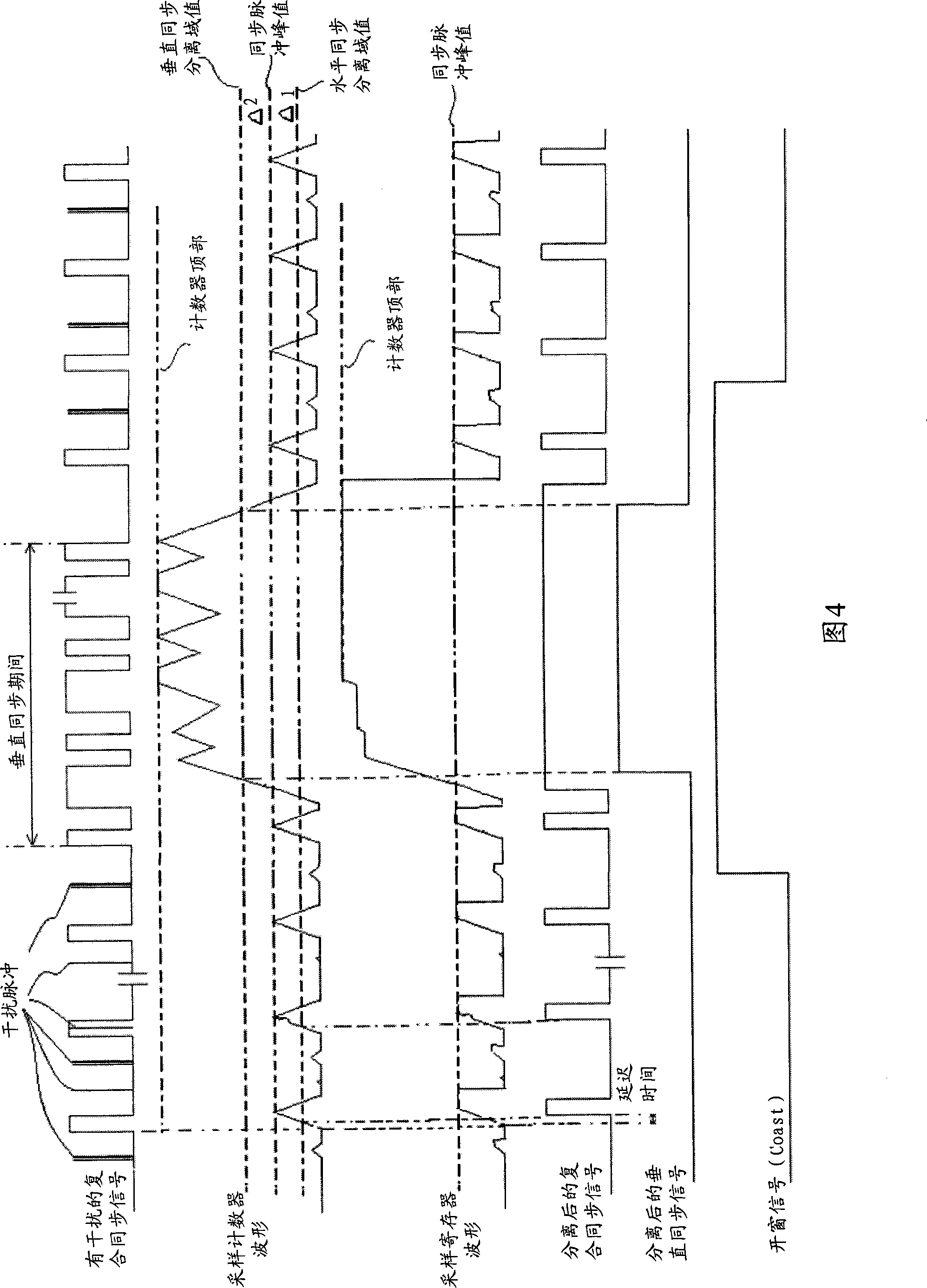

[0026] The first embodiment of the present invention provides a synchronous clock extraction device, its structural block diagram is as follows image 3 As shown, including: clamper and composite sync separator, vertical sync separator, standard detector, phase-locked loop and delay-locked loop.

[0027] The above-mentioned clamper is used for recovering a DC component from an interference signal embedded with a synchronization signal (eg, a video signal), and sending the interference signal including the recovered DC component to the composite sync separator.

[0028] The composite synchronous separator is used to compare the level of the signal output by the clamper with the set separation level, and obtain the interfering composite synchronous signal according to the comparison result.

[0029] Taking the interfering SOY signal embedded in synchronization as an example, the clamper restores the DC component of the SOY signal, and the compound sync separator combines the lev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More