An irregular topology structure generation method for chip network

A technology of on-chip network and topology structure, applied in the field of on-chip interconnection network design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

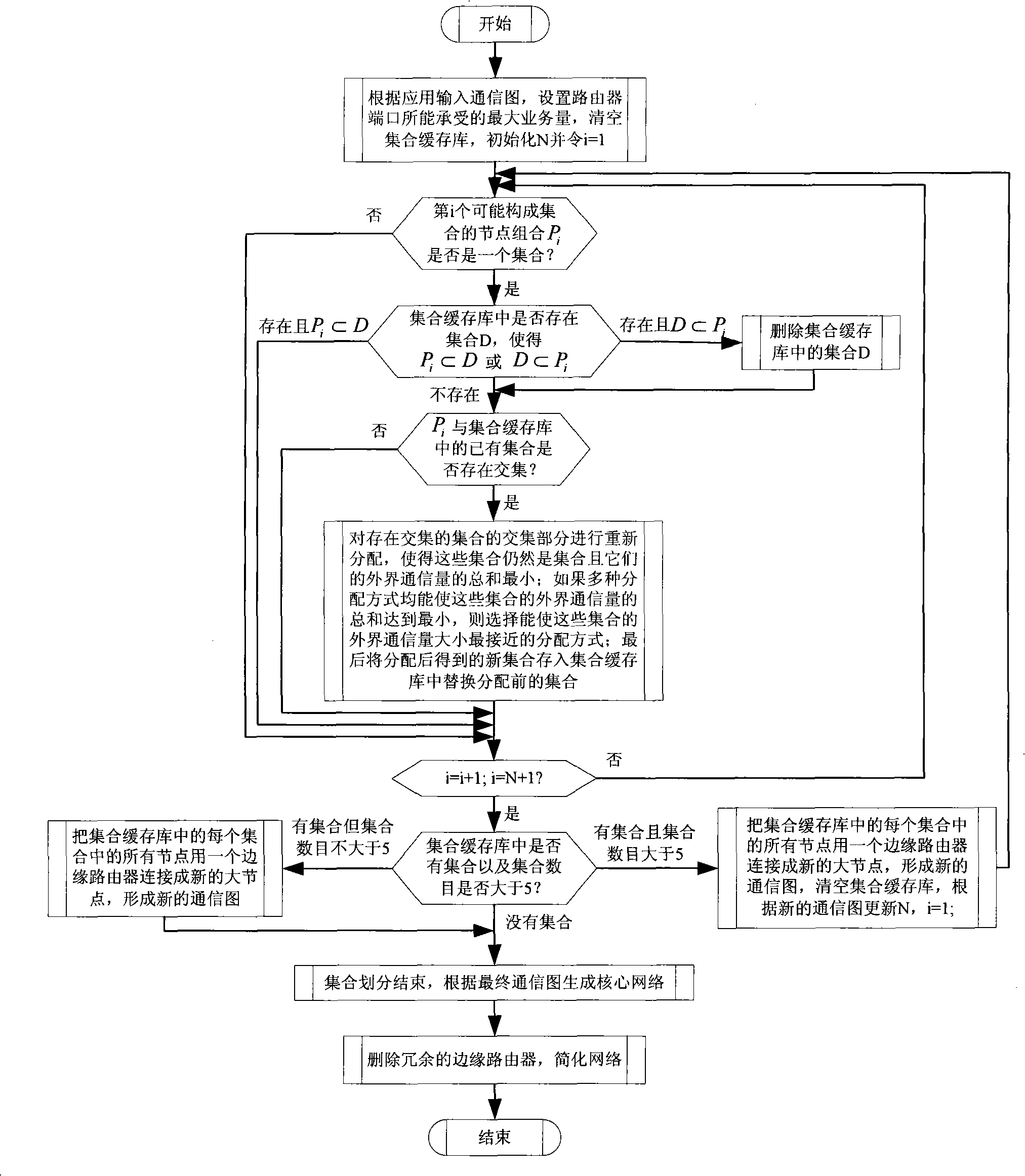

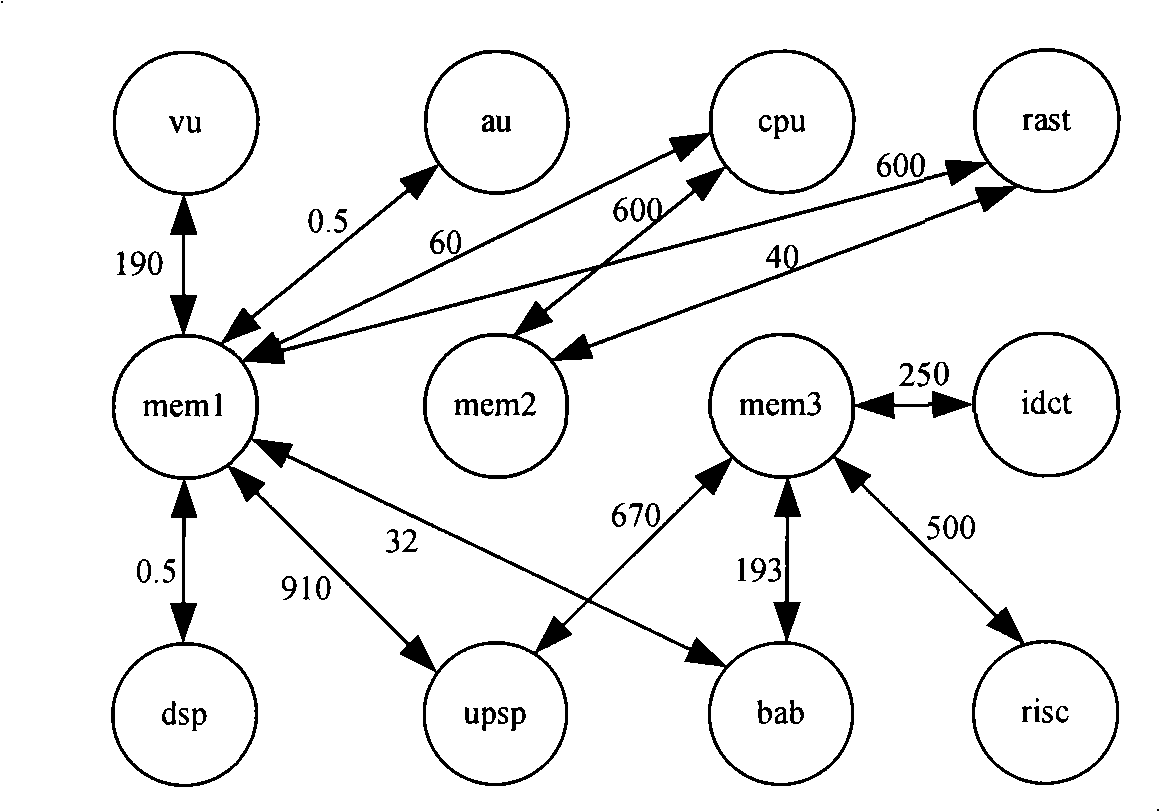

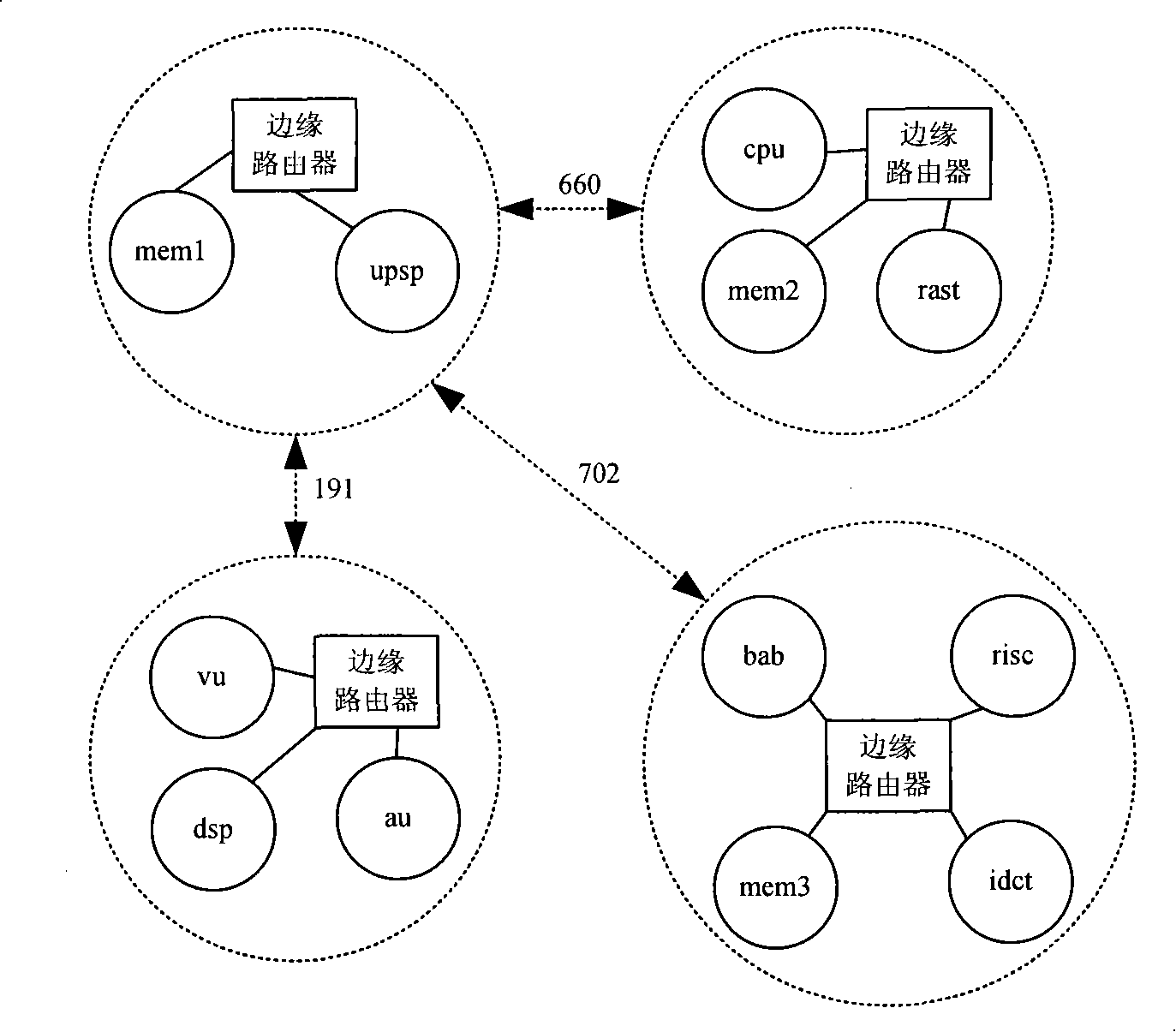

[0022] Before describing the specific implementation, we first define five concepts: 1) All the nodes constituting the set A are called elements of the set A. 2) If there are common elements in the two sets, it is said that the two sets have an intersection. 3) If all elements in set B belong to set A and there are elements in A that do not belong to B, then set A is said to contain set B, expressed as B ⋐ A ; Otherwise, it is said that set A does not contain set B, expressed as B ⊂⃒ A . 4) The sum of the traffic between each node in a set and each node outside the set is called the external traffic of the set. 5) For edge routers, the ports connected to the nodes of the directed communication graph are called local ports, and other ports are called network ports. An edge router can have multiple local ports but only one network port. Assuming that the number of nodes in a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More