IC testing methods and apparatus

A technology for testing circuits and test patterns, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

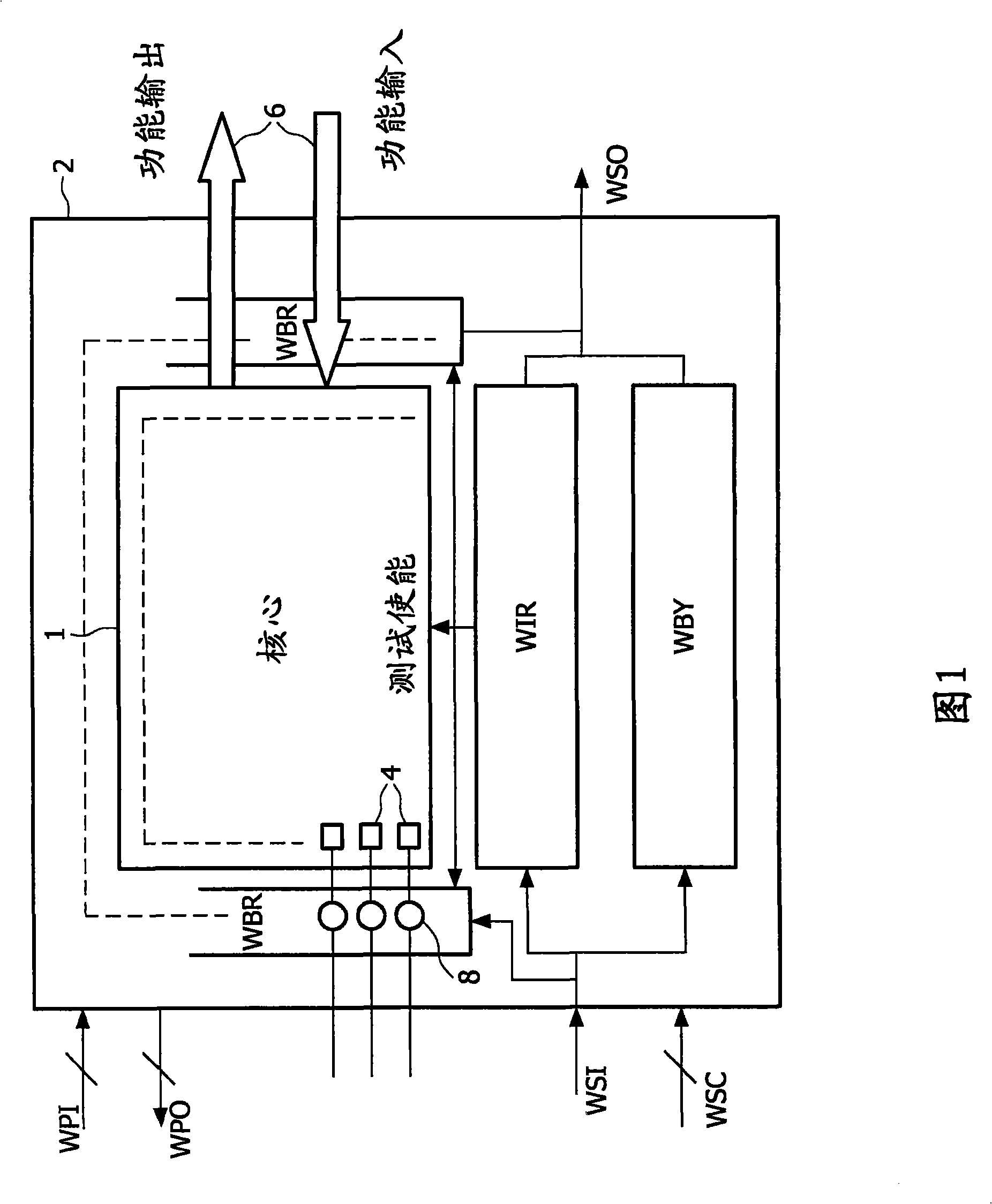

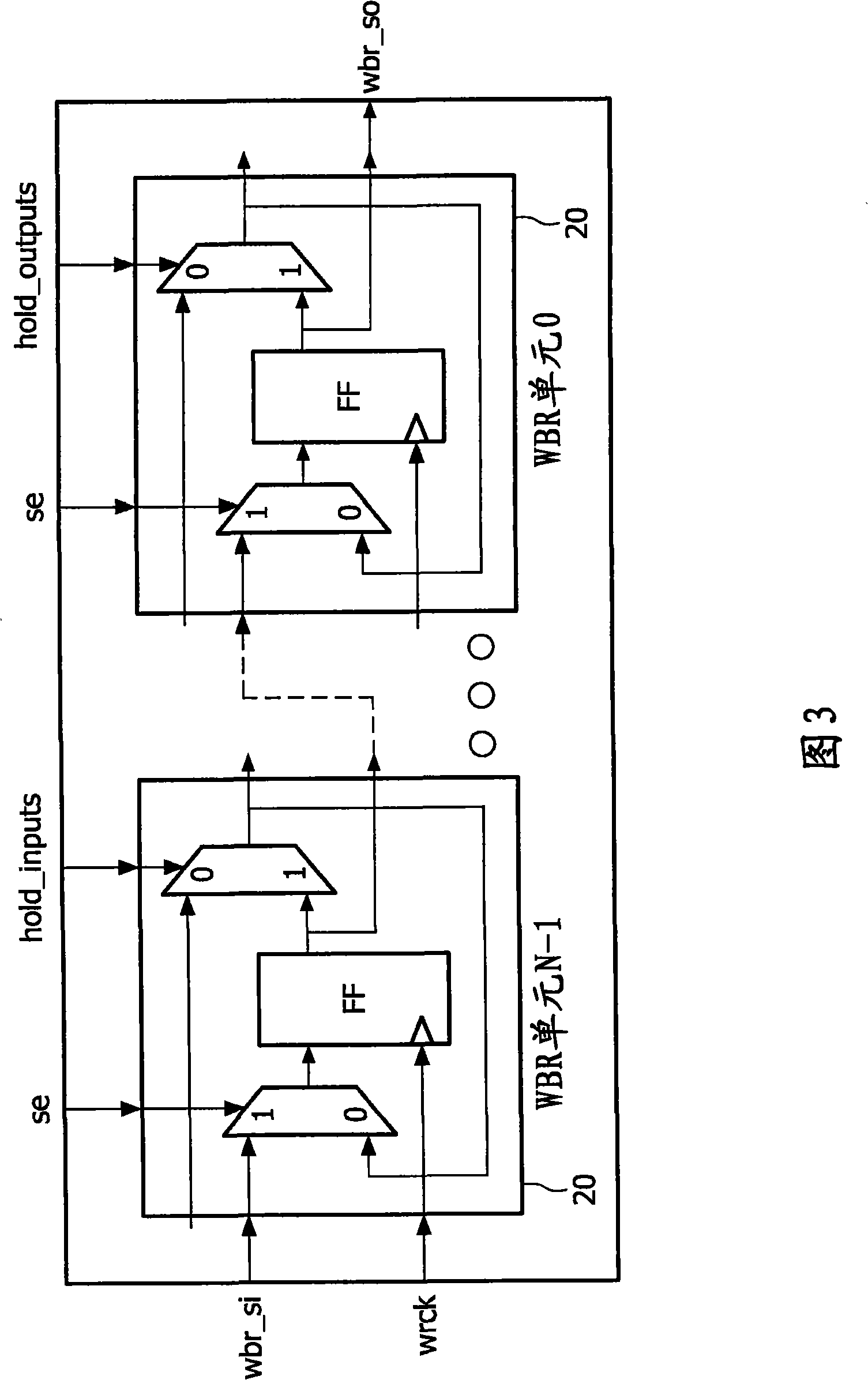

[0064] The example of the invention described below provides an encapsulator architecture in which WBR units are configured in groups in parallel to support reception of parallel data from parallel encapsulator ports.

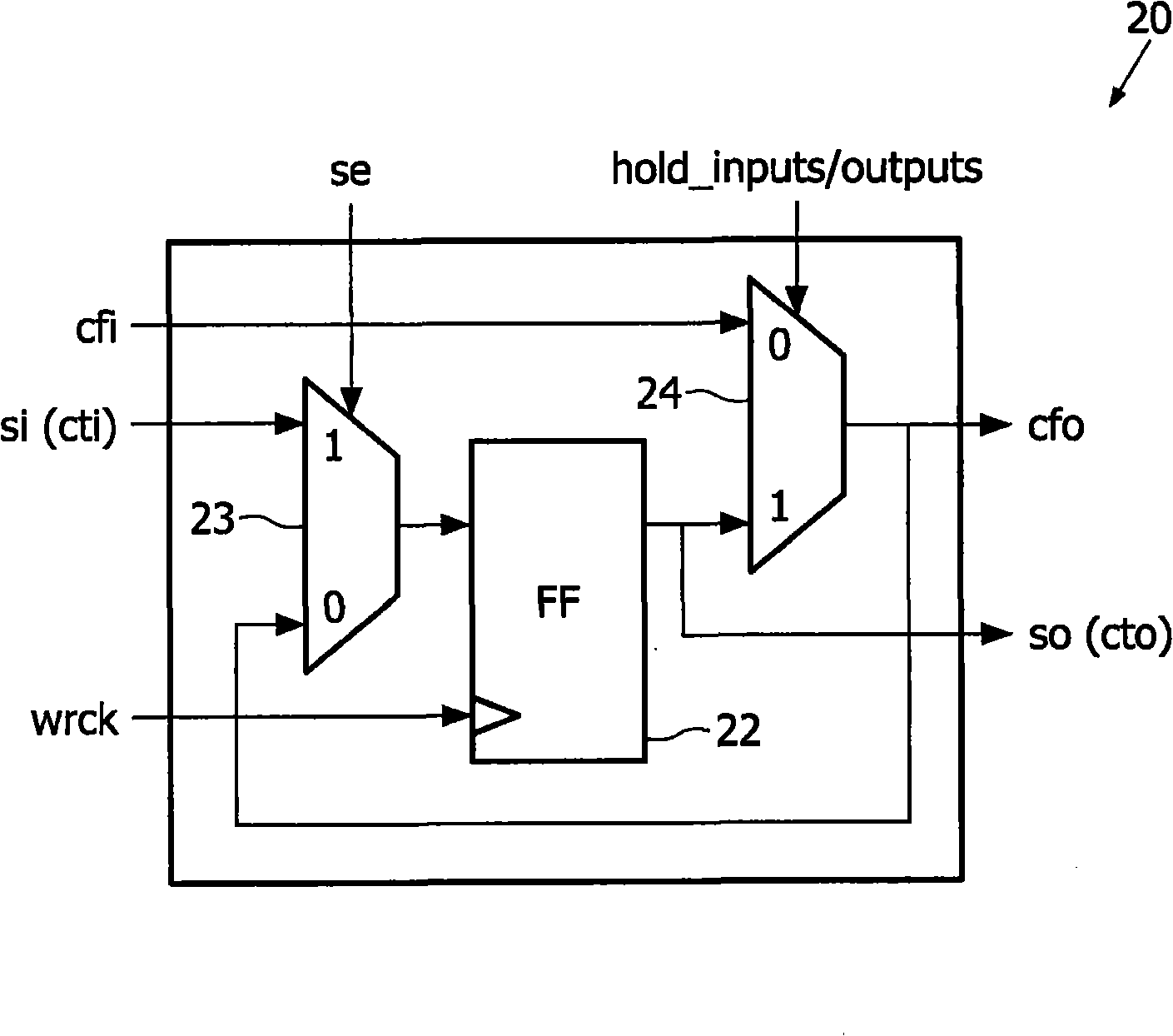

[0065] A scan chain segment is defined between each serial input and a respective serial output, the scan chain segment comprising a cell set of shift register circuits, a core scan chain portion, a first bypass path bypassing the core scan chain portion, and A second bypass path bypassing the group of shift register circuit cells. This structure enables data to be loaded in parallel to the core scan chains, or to the shift register (WBR). In addition, each scan chain segment has a series latch element, which provides additional test performance. In particular, data shifting between these latch elements can be used to test bypass paths when executing internal or external modes. Therefore, such testing can be performed as part of a single ATPG process.

[006...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More