Clock receiver and correlative semiconductor memory module and emendation method

A storage module and receiver technology, applied in information storage, static memory, digital memory information and other directions, can solve problems affecting clock signal edge, phase offset, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

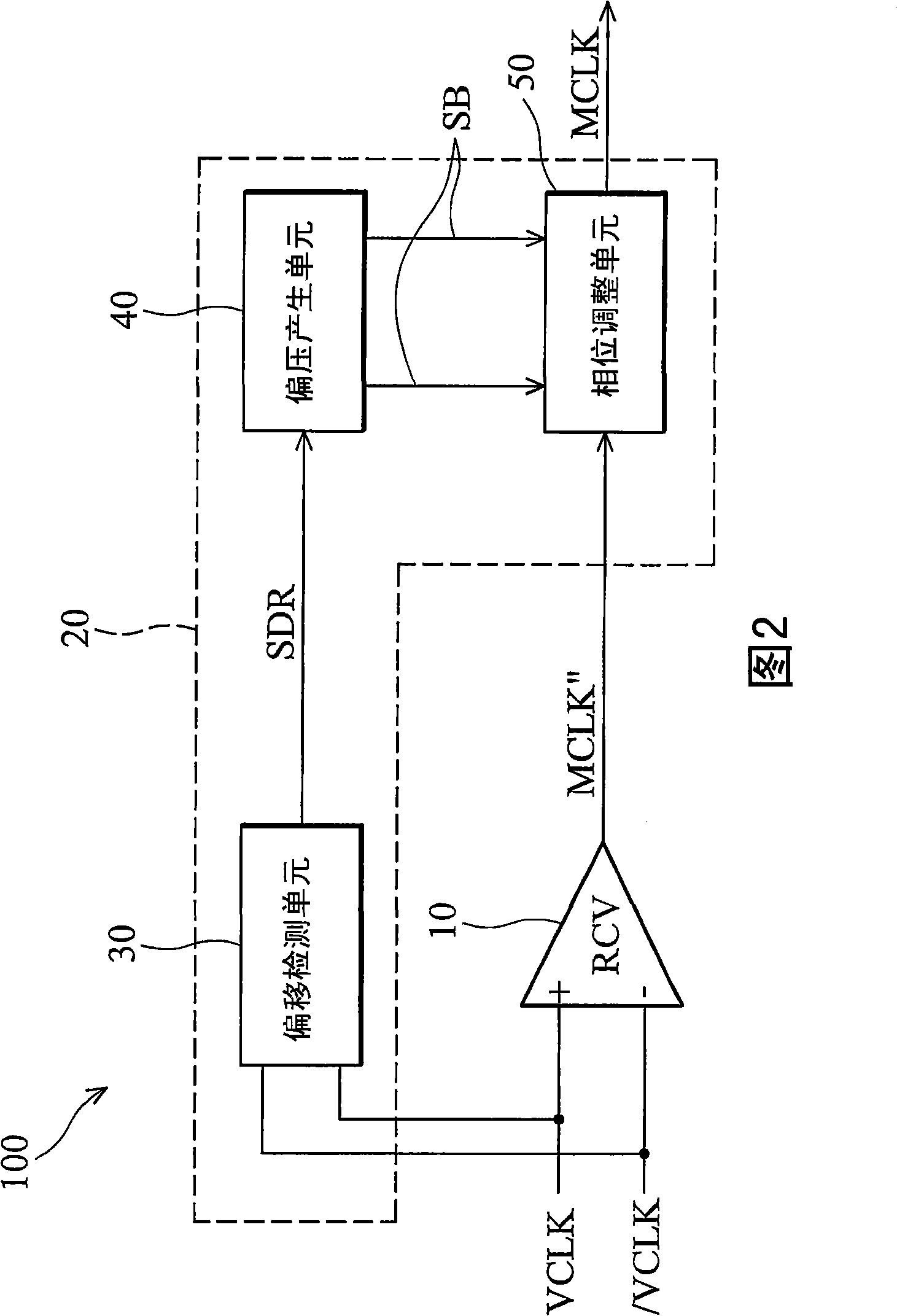

[0041] figure 2 Shown is an embodiment of a clock receiver of the present invention. As shown in the figure, the clock receiver 100 includes: a receiving unit 10 for receiving a complementary clock signal VCLK and / VCLK and generating a clock signal MCLK”; and a correction unit 20 for detecting the clock signal VCLK and / Whether the intersection point of VCLK is shifted, the toggling of the clock signal MCLK" is adjusted so as to output a main clock signal MCLK. The calibration unit 20 includes an offset detection unit 30 , a bias voltage generation unit 40 and a phase adjustment unit 50 . For example, the clock receiver 100 can be disposed in a semiconductor chip, but not limited thereto.

[0042] The receiving unit 10 is used to receive the clock signals VCLK and / VCLK to generate a corresponding clock signal MCLK". For example, the receiving unit 10 can be a receiver, when the level of the clock signal VCLK is higher than the clock signal / VCLK When the level is high, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More