Area compact and fast BCH parallel decoding method

A compact and fast technology, applied in the field of error control codes, which can solve the problems of reduced implementation area of BCH decoder, large hardware implementation area, slow decoding speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

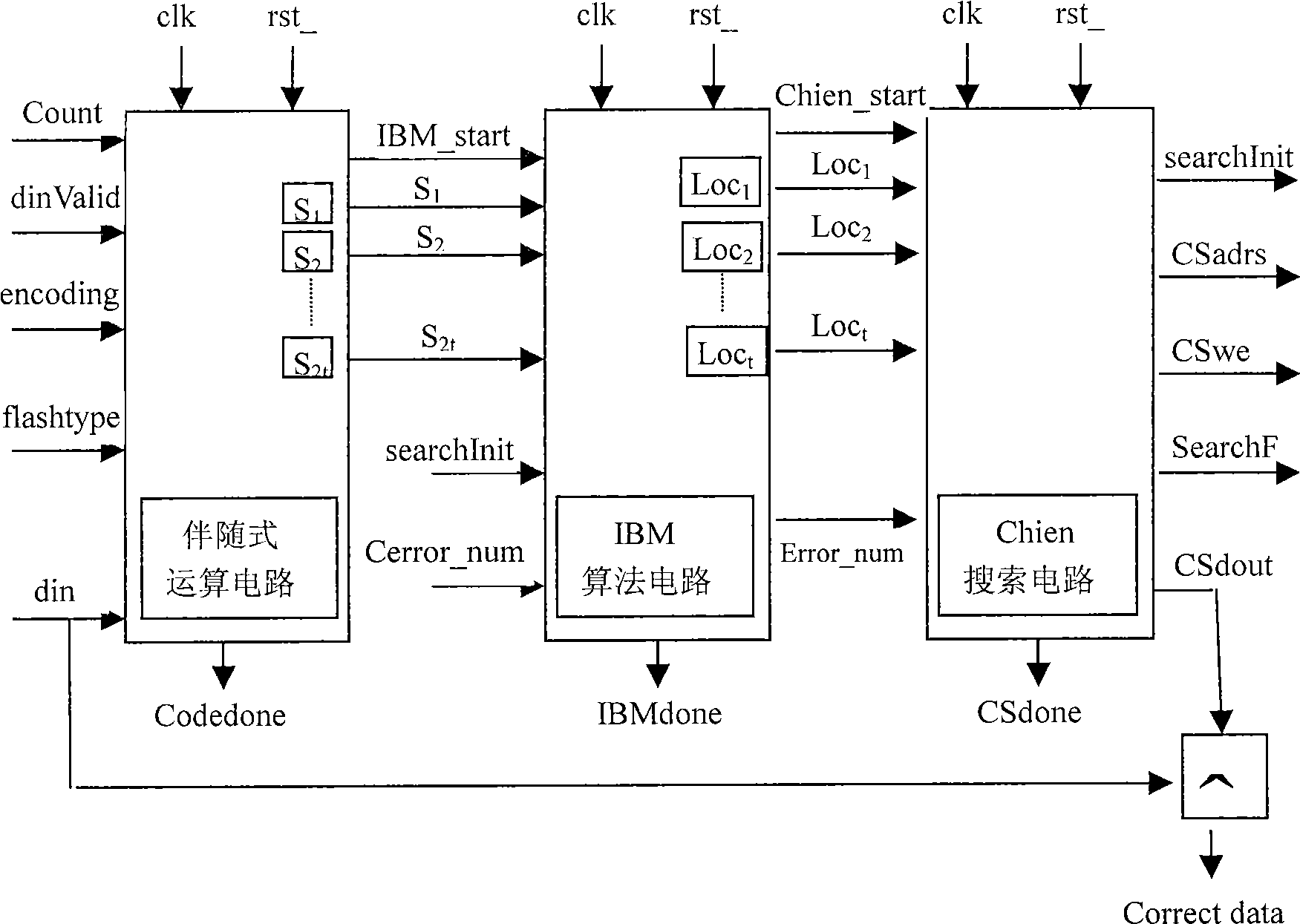

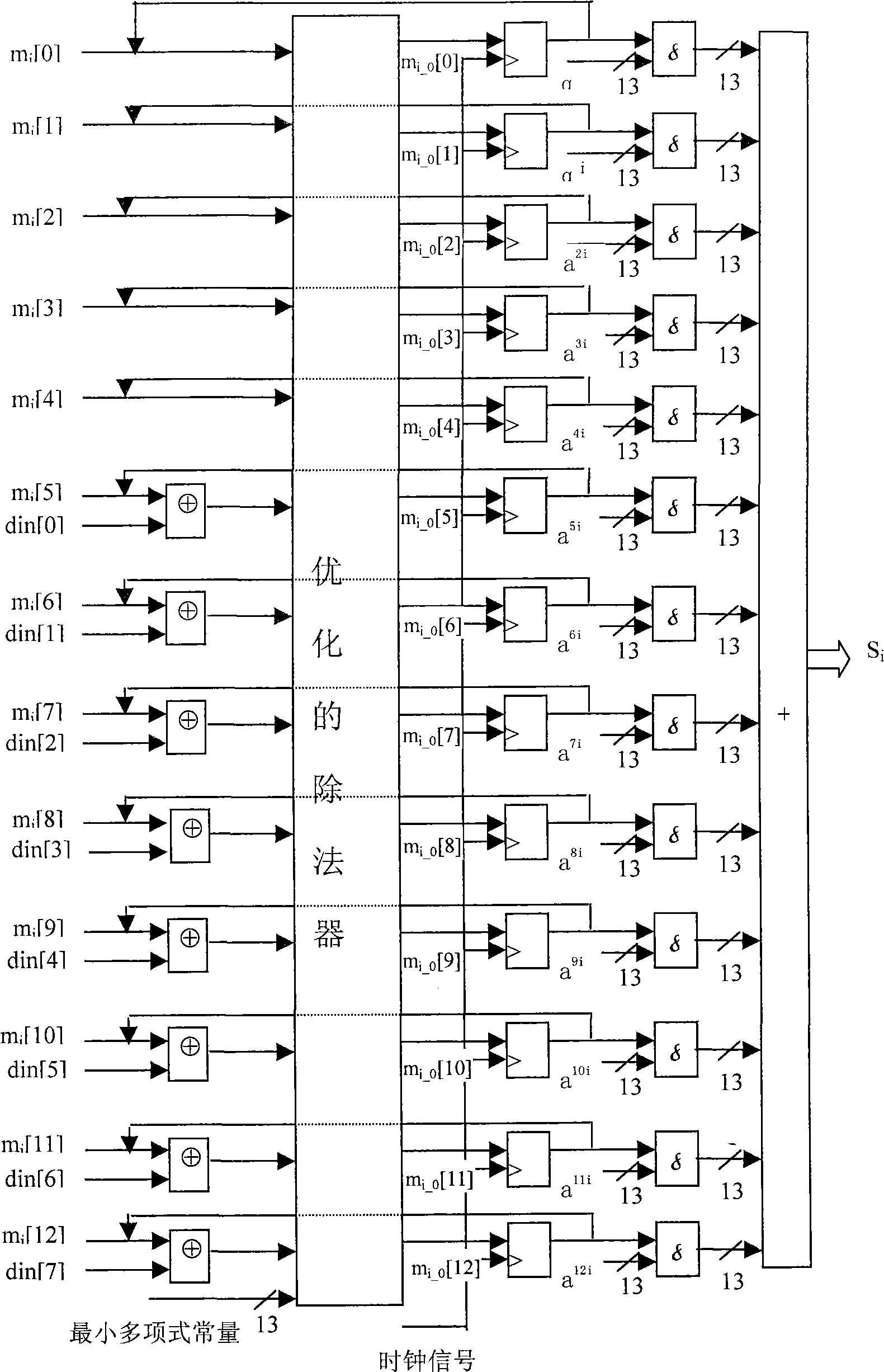

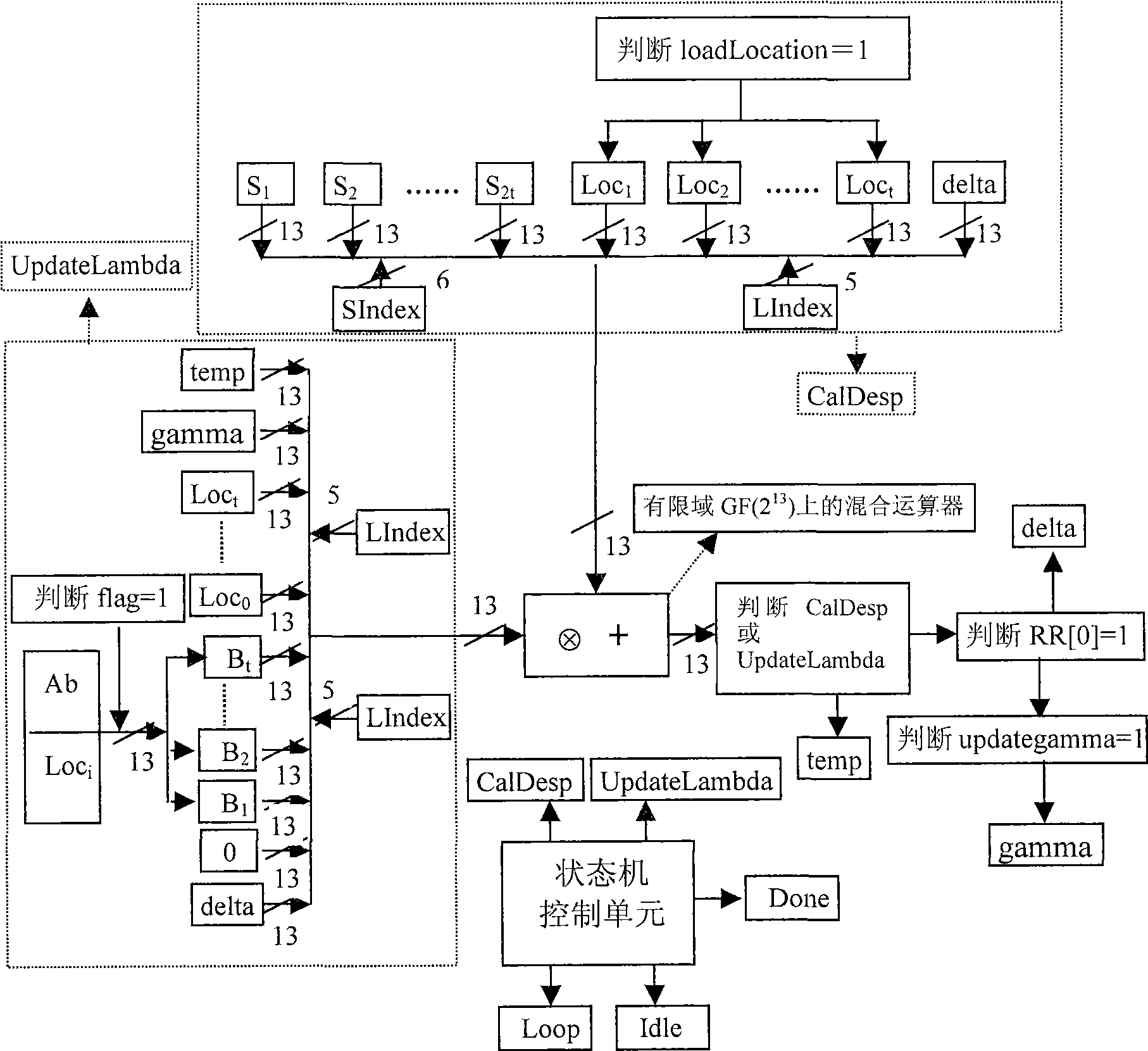

[0062] Embodiment: a compact and fast BCH parallel decoding method, by BCH parallel decoding circuit (such as Figures 1 to 4 shown) to realize error correction when reading data, the BCH parallel decoding circuit is mainly composed of adjoint syndrome operation circuit (i.e. figure 1 The adjoint operation circuit in ), the error position polynomial iterative circuit (ie figure 1 The IBM algorithm circuit in the) and the wrong address search circuit (iefigure 1 Chien search circuit in) composition. The BCH parallel decoding circuit works in the finite field GF(2 13 ), first use the syndromic syndrome operation circuit to complete the calculation of the syndrome syndrome through the parallel operation of 8-bit codeword input at the same time, and then use the error position polynomial iterative circuit to obtain The error position polynomial, and finally use the error address search circuit to use the 4-bit pre-search method of full combinational logic to pre-search the error...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More