Symbol rate hardware accelerator

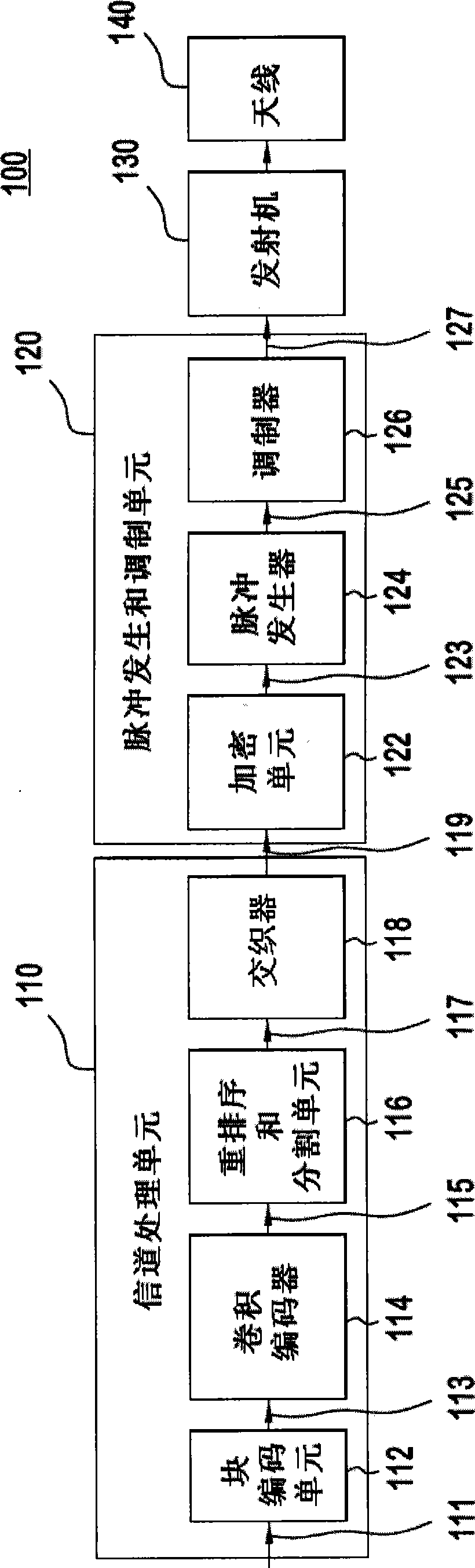

A technology of hardware accelerator and buffer, which is applied in the direction of instruments, electrical components, digital transmission systems, etc., and can solve problems such as loss of flexibility and changes in hardware requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

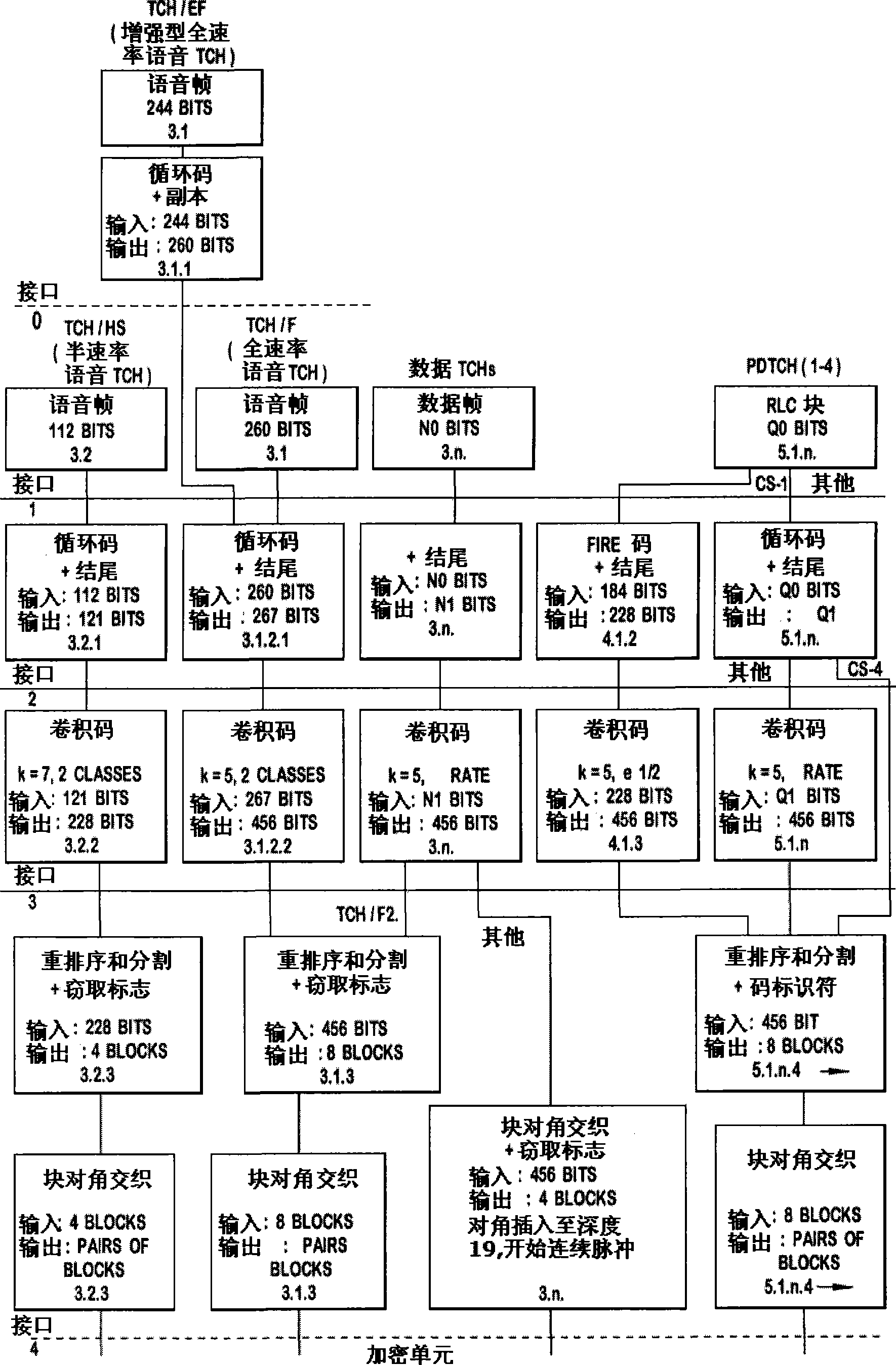

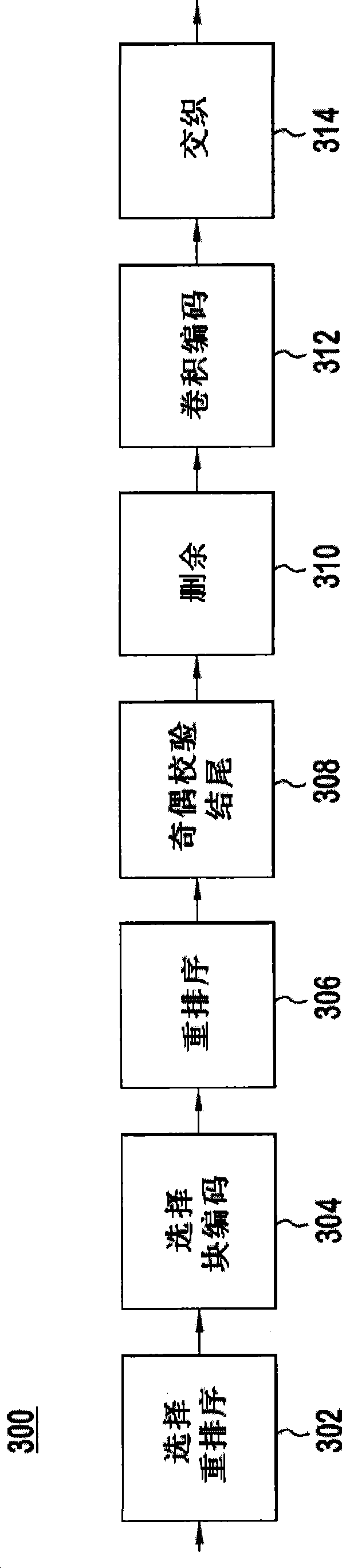

Method used

Image

Examples

Embodiment

[0059] CLAIMS 1. A hardware accelerator for performing channel processing on wirelessly transmitted and received information bits, the hardware accelerator in communication with a shared memory.

[0060] 2. The hardware accelerator according to Embodiment 1, comprising: a first buffer and a second buffer for storing information bits and processed information bits.

[0061] 3. The hardware accelerator according to embodiment 2, comprising: at least one address generator for generating addresses for accessing the first buffer and the second buffer.

[0062] 4. The hardware accelerator according to any one of embodiments 2-3, comprising: a translation ROM for generating translated addresses for accessing the first buffer and the second buffer.

[0063] 5. The hardware accelerator according to any one of embodiments 1-4, comprising: an interface for accessing a shared memory.

[0064] 6. The hardware accelerator according to any one of embodiments 1-5, comprising: a CRC generator...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More