Hierarchical buffer zone management system and method

A management system and buffer technology, applied in the field of hierarchical buffer management systems, can solve the problems of short access length, affect access, affect the efficiency of other modules, etc., and achieve the effects of improving access response, reducing access times, and improving response speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0033] Figure 5 A schematic structural diagram of the hierarchical buffer management system according to the present invention is shown.

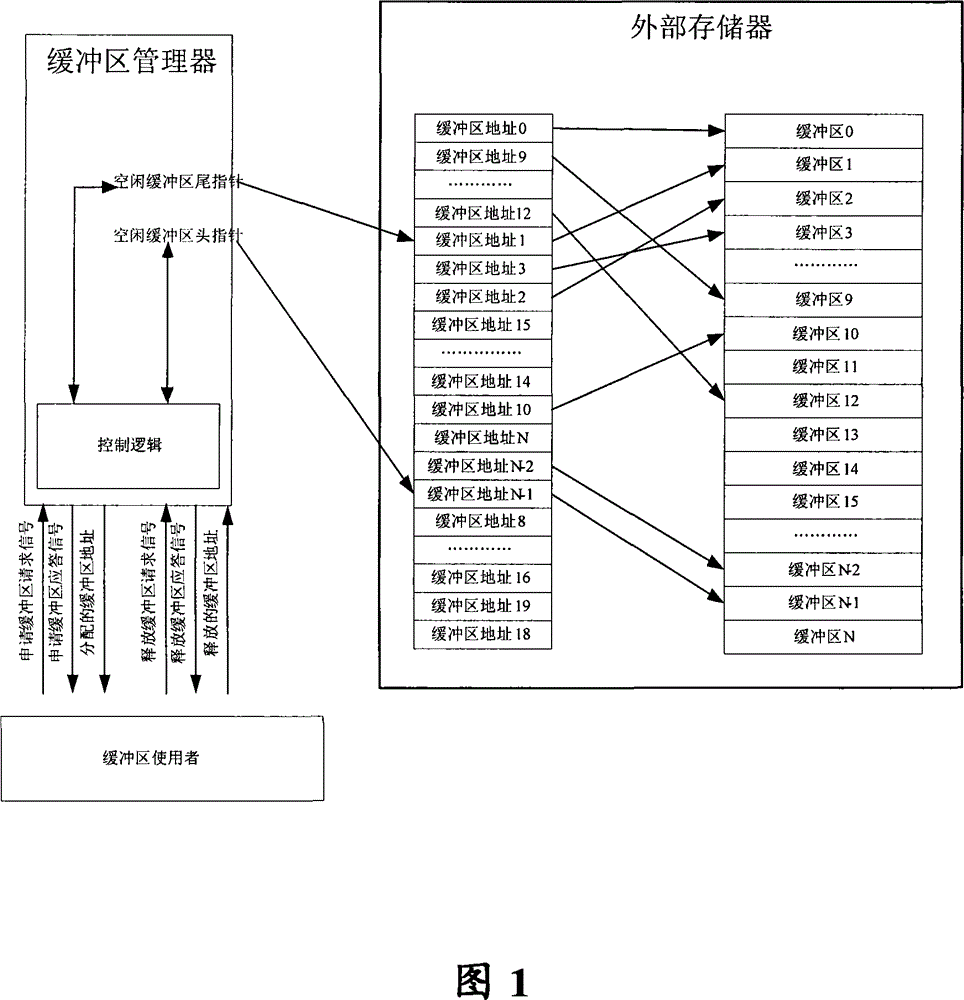

[0034] refer to Figure 5 , provides a hierarchical buffer management system, including a chip 10 and an external memory 20, wherein the external memory 20 includes an external free buffer queue 201, the chip 10 includes an external free buffer queue control module 103 and a control logic module 104, the chip 10 also includes:

[0035] The internal free buffer queue 101 is used to store the RAM space of the partial buffer address, wherein the priority of storing the buffer address in the internal free buffer queue 101 is highe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More