Test vector coding compression method based on test vector compatibility

A test vector, code compression technology, applied in the direction of digital circuit test, electronic circuit test, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

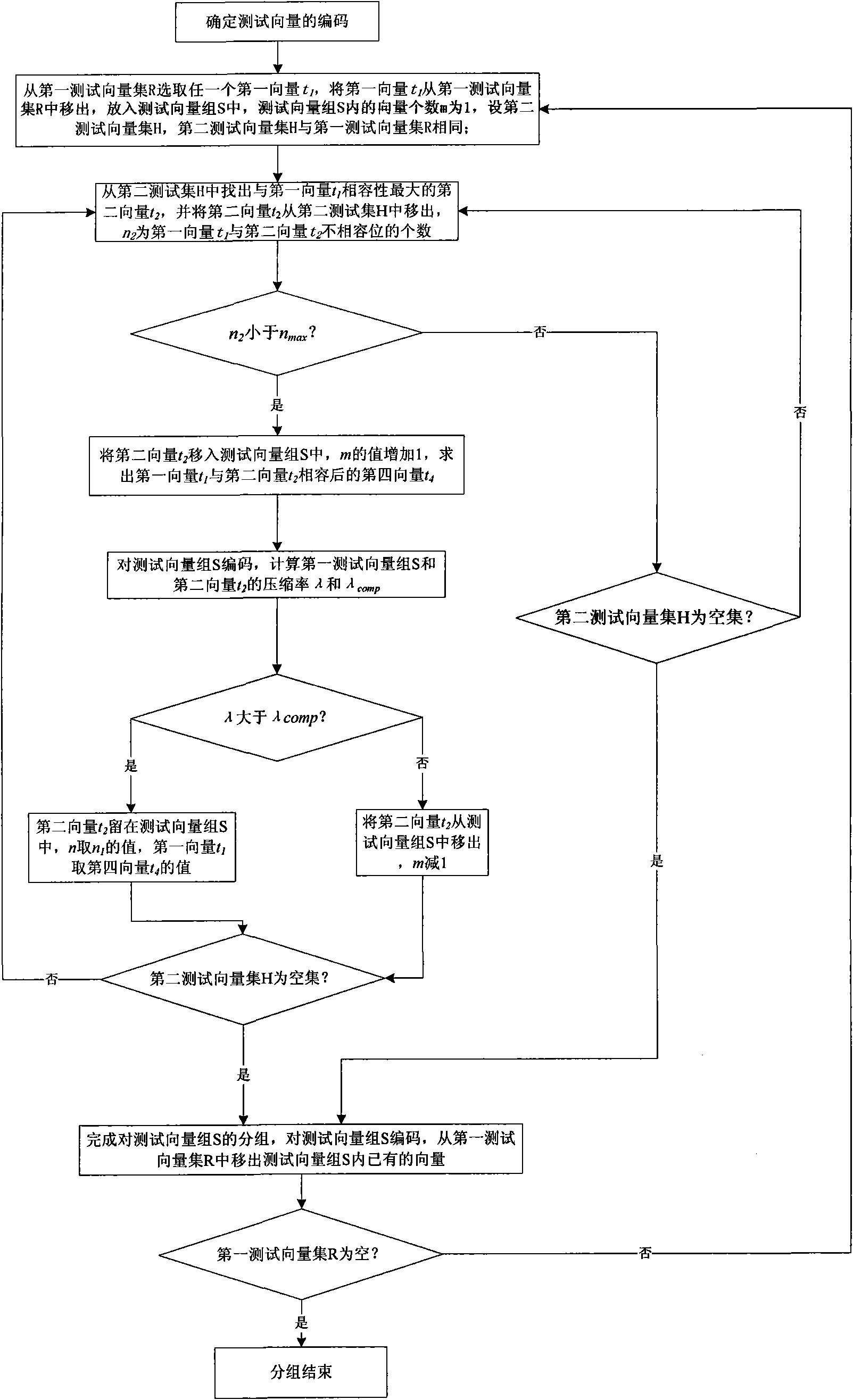

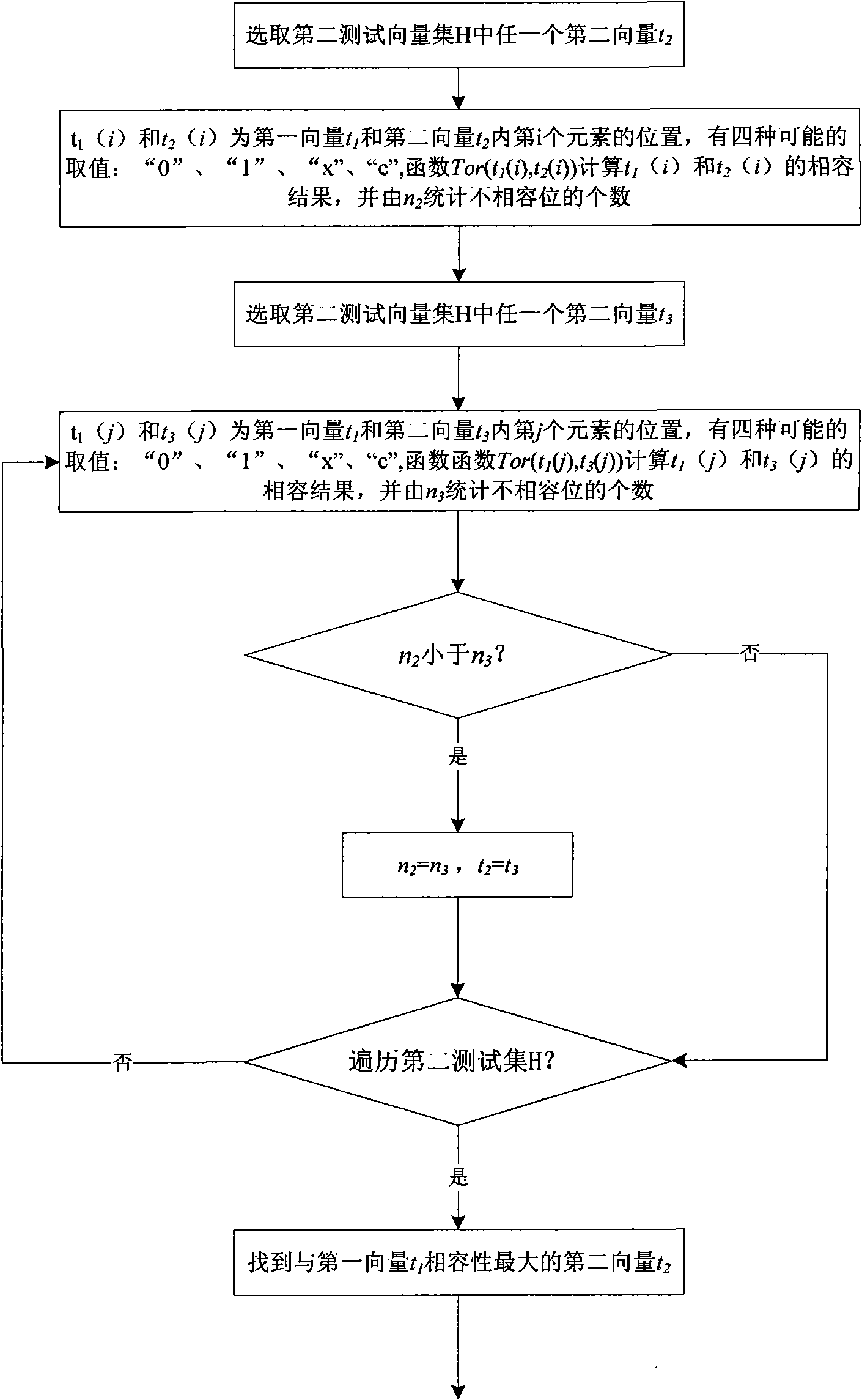

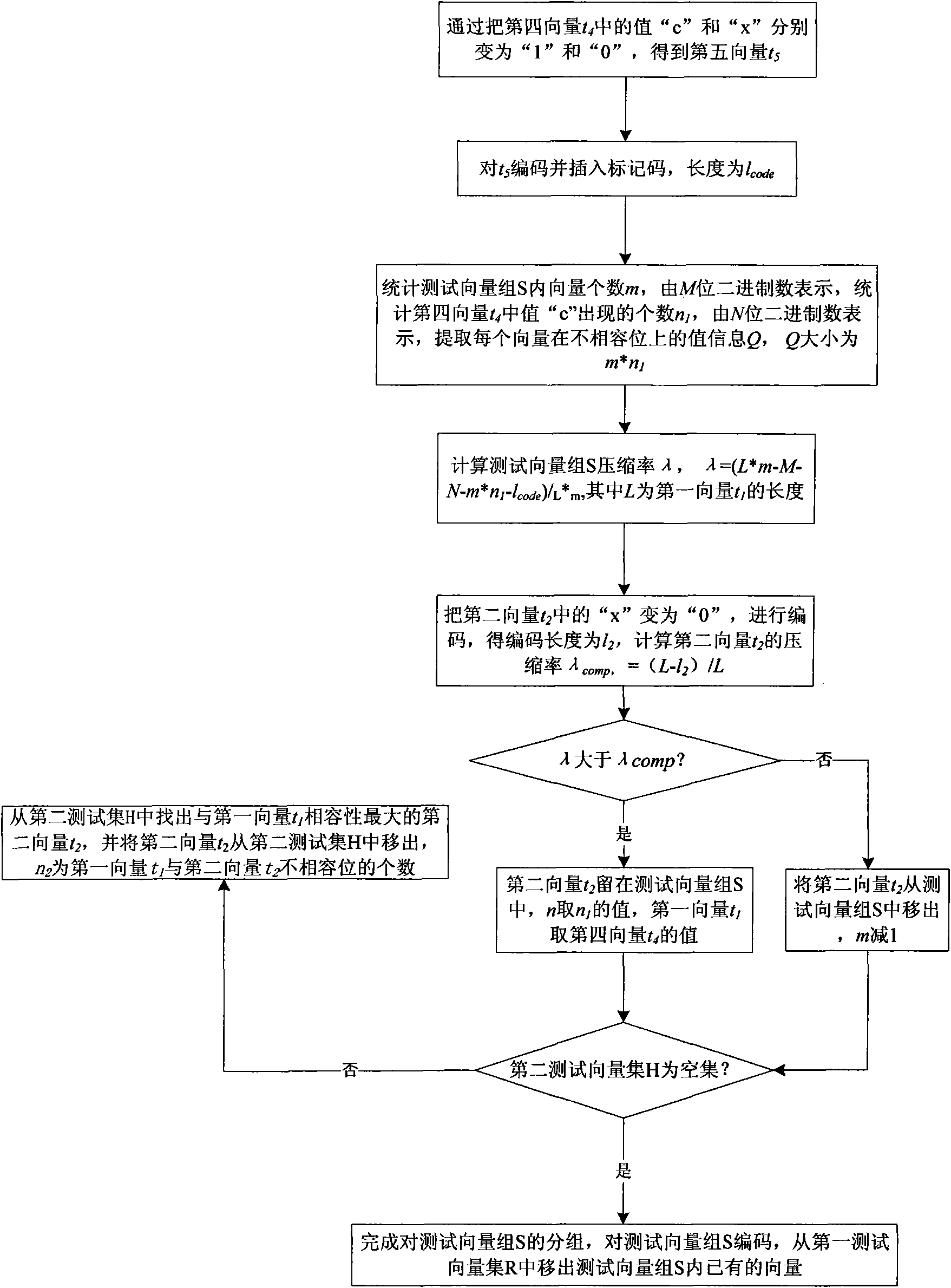

Method used

Image

Examples

Embodiment

[0126] Suppose there are four vectors in the test set R: T1, T2, T3, T4. The vector length L is both 24 bits. Pick T1 as the first vector of group S, shift out of R, and make t 1 =T1. The vectors in R are T2, T3, T4. Set H=R. n max =3. The group segmentation code Sep_code takes 11110

[0127] T1: 1xxx1xxxx0xx1xxxxx1xxxxx

[0128] T2: xxxx0xx0x0xxx0xxxx1xxxxx

[0129]T3: 0xxx1xxxx1xxxxxxxx1xxx1x

[0130] T4: 1xxx01xxx1xxxxxxxxx0xx0x

[0131] find and t from H 1 The most compatible vector, get the vector t 2 =T2,n 2 =1. remove t from H 2 . n 2 less than n max And the test set H is not an empty set. m=2, merge t 1 with t 2 get the vector t 4 . t 2 Move into test vector group S. t 4 The median number of "c" is n 1 =1, M=N=2, Q=m*n 1 = 2.

[0132] t 4 : 1xxxcxx0x0xx10xxxx1xxxxx

[0133] Set "c" to "1" and "x" to "0" to get the vector t 5

[0134] t 5 : 100010000000100000100000

[0135] Encoding: 011010110010110000110000 24bits

[0136] Insertion c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More