Method for processing abnormality between main processor and coprocessor interface and realizing device

A technology of co-processor and main processor, applied in the direction of response error generation, etc., can solve the problems of low switching efficiency, time-consuming, poor real-time performance, etc., and achieve the effect of improving switching efficiency, reducing complexity, and good real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

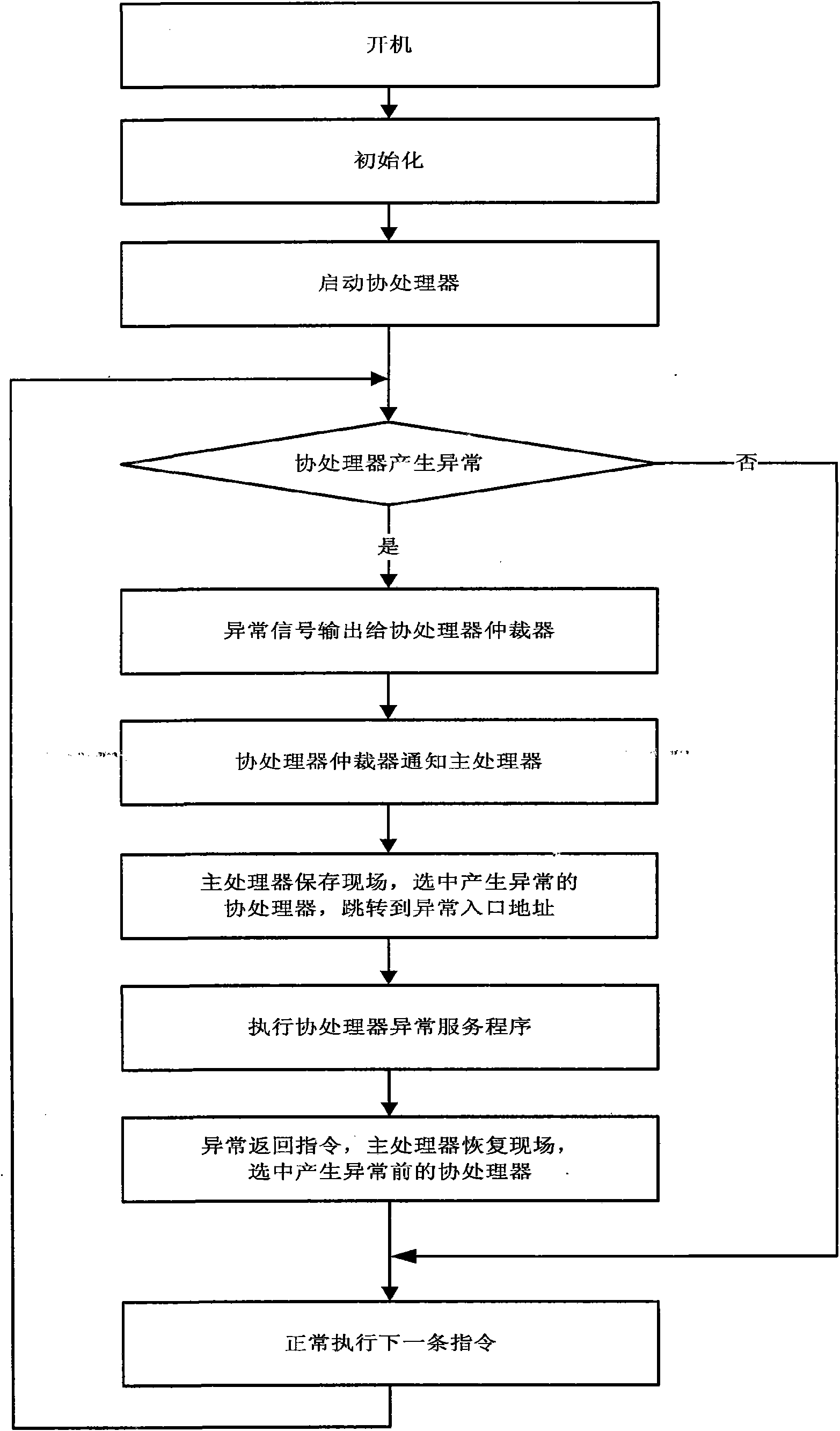

[0026] refer to image 3 , an exception handling method between a main processor and a coprocessor interface, the exception handling method comprises the following steps:

[0027] A. When the coprocessor generates an abnormal signal, it notifies the main processor;

[0028] B. The main processor automatically switches to the abnormal coprocessor according to the abnormal signal generated: by backing up the original main processor status register to the main processor status shadow register, the current main processor status register is automatically modified and the generated coprocessor is selected. exception coprocessor;

[0029] C. After the main processor executes the exception service program, when returning through a main processor exception return instruction, the coprocessor before the exception is automatically restored according to the main processor state shadow register.

[0030] In the step A, the process of when the coprocessor generates an abnormal signal: an ...

Embodiment 2

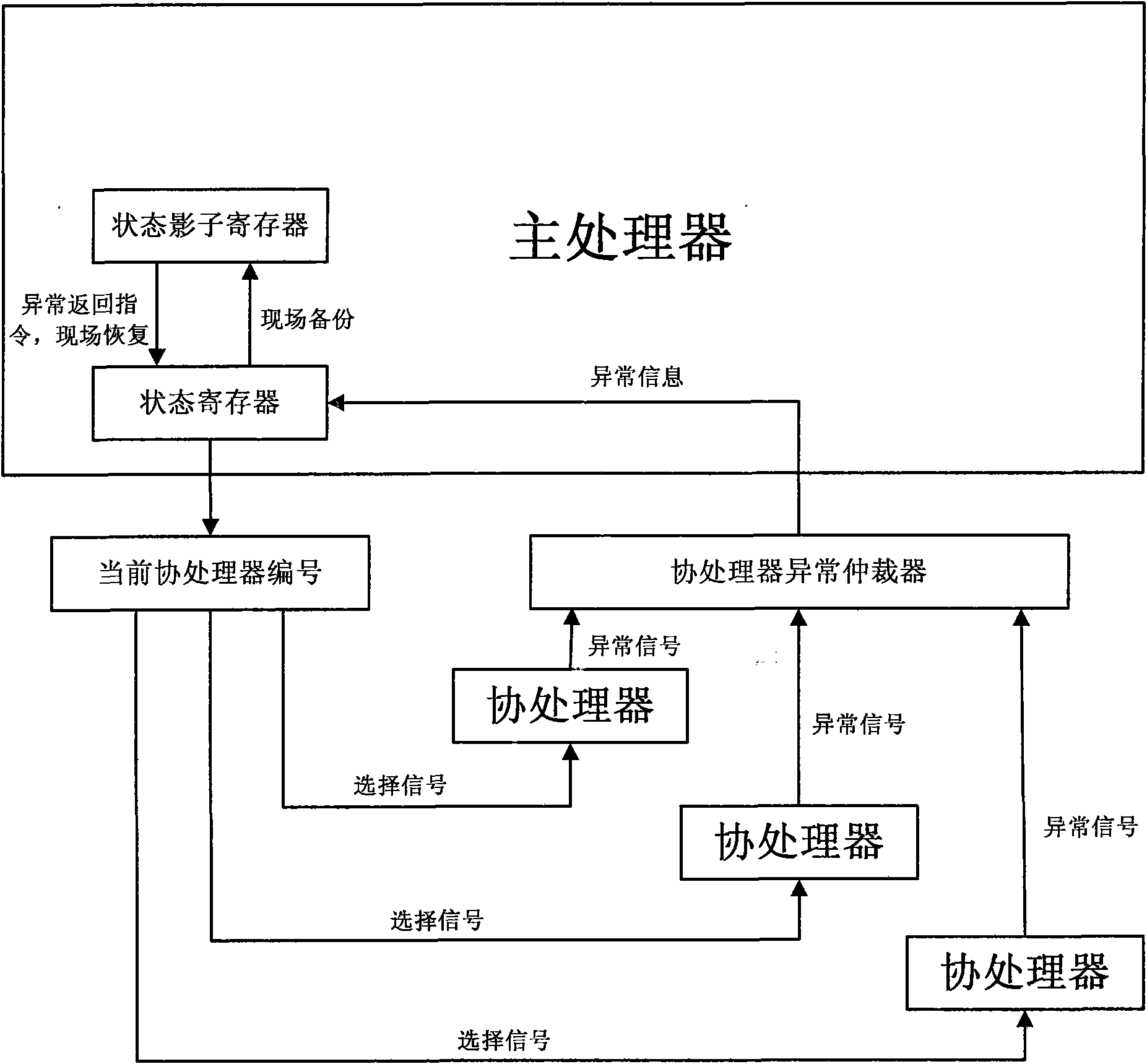

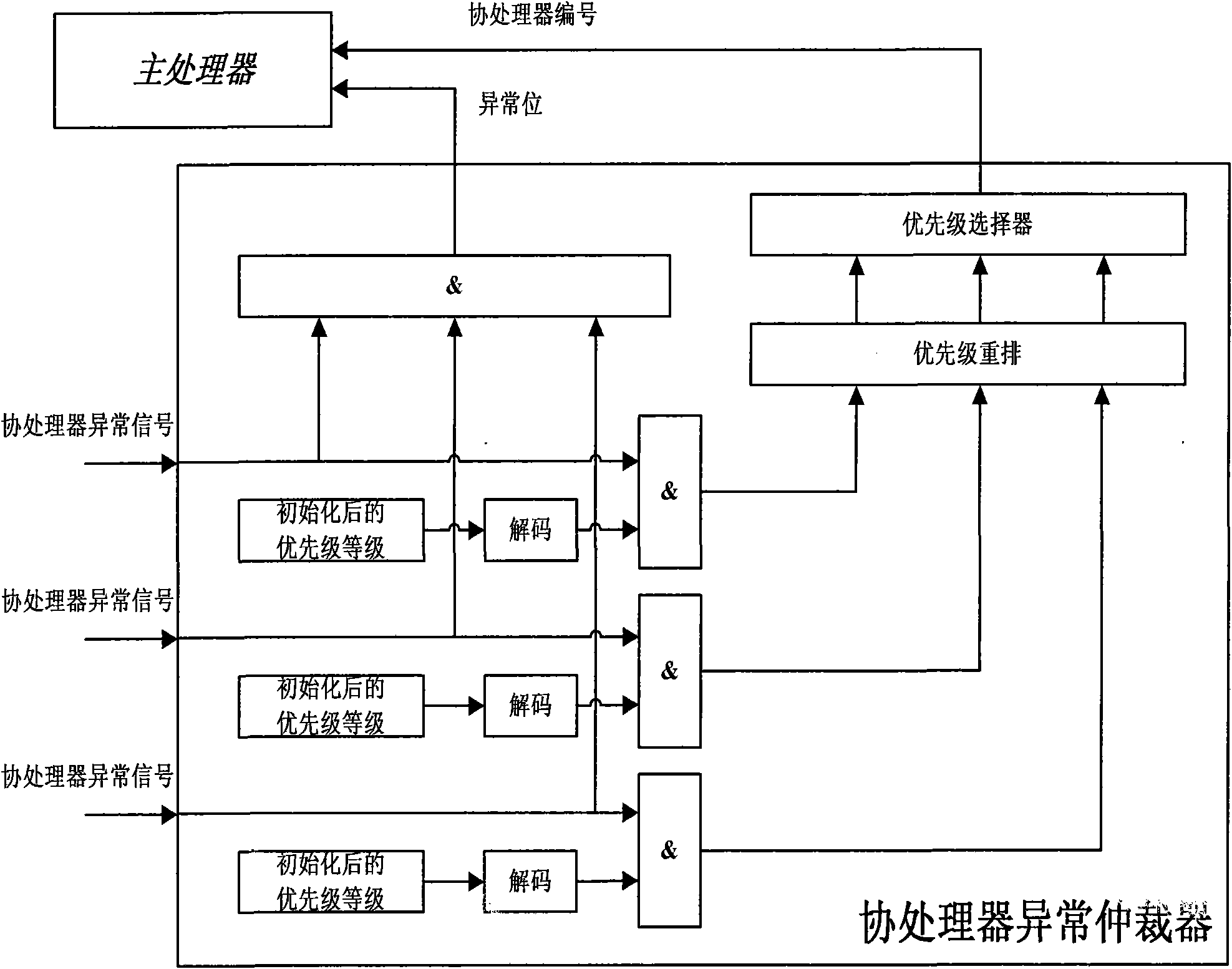

[0044] refer to Figure 1 ~ Figure 2An exception handling device between a main processor and a coprocessor interface includes a main processor and a coprocessor, the coprocessor includes a coprocessor abnormal signal generating unit for generating an abnormal signal; the main The processor includes: a coprocessor selection unit for the main processor to select a corresponding coprocessor according to the indication of the main processor status register; a main processor status register for indicating the coprocessor number selected by the current main processor; The main processor status shadow register used to save the coprocessor number selected by the main processor before the exception occurred; and the main processor exception used to notify the main processor to handle returning from the abnormal state to the normal state after completing the exception service routine Return to the control unit.

[0045] There are at least two coprocessors, and the implementation devic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More