Unbalanced design method of high-position current source unit of current rudder-type digital-to-analog converter

A technology of digital-to-analog converters and design methods, applied in digital-to-analog converters, electrical components, circuits, etc., can solve the problems of large precision errors of digital-to-analog converters, the inability to effectively reduce second-order errors, and high integral nonlinear errors , to achieve the effects of offsetting the second-order error, improving accuracy, and reducing integral nonlinear error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

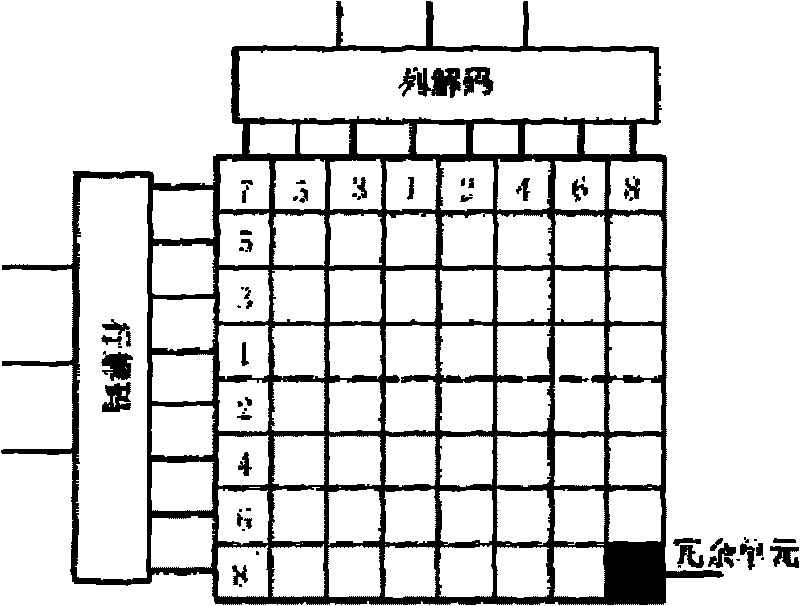

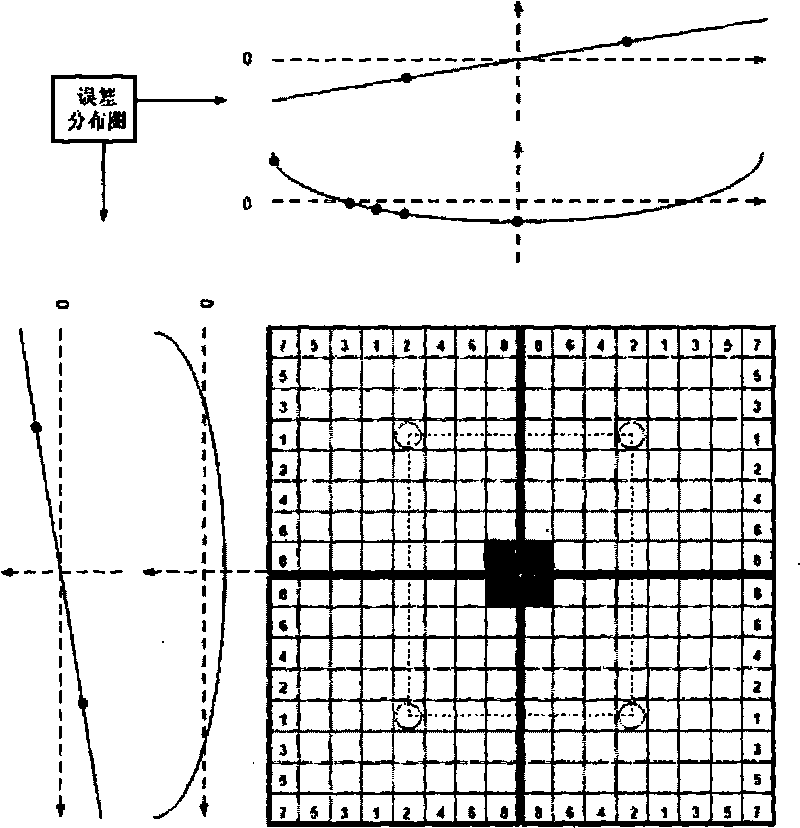

[0020] Embodiment 1: a high-speed and high-precision current steering digital-to-analog converter with 10-bit precision, its low-order current unit is composed of 4 binary current source units, and its high-order current unit controls 6 high-order, which includes 63 current source units. The 63 current source units are placed in the physical layout of the actual chip, and each unit is divided into four parts. These four parts are placed symmetrically in four quadrants, forming an 8×8 matrix in each quadrant. It is 8 rows and 8 columns, and the extra unit is a redundant unit. Since it is placed symmetrically in four quadrants, the units in each quadrant are opened in a specific order. Take the second quadrant as an example, see figure 1 , counting from left to right, the fourth column of the physical column is the first column to be opened, and the fifth column of the physical column is the second column to be opened. For the order of the number of columns to be opened, see fig...

Embodiment 2

[0022] Embodiment 2: a high-speed and high-precision current steering digital-analog converter with 10-bit precision, its low-order current unit is composed of 4 binary current source units, and its high-order current unit controls 6 high-order, which includes 63 current source units. The 63 current source units are placed in the physical layout of the actual chip, and each unit is divided into four parts. These four parts are placed symmetrically in four quadrants. The structure diagram of the second quadrant is shown in figure 1 . Among them, the second-order error brought by the CMOS process itself is 0.032%, and the length of the MOS tubes of the 63 current source units is l, and the widths of the 1st, 2nd, 3rd, 4th, 5th, and 6th column MOS tubes are all is w, the width of the MOS tube in the seventh column is 0.985w, and the width of the MOS tube in the eighth column is 1.015w.

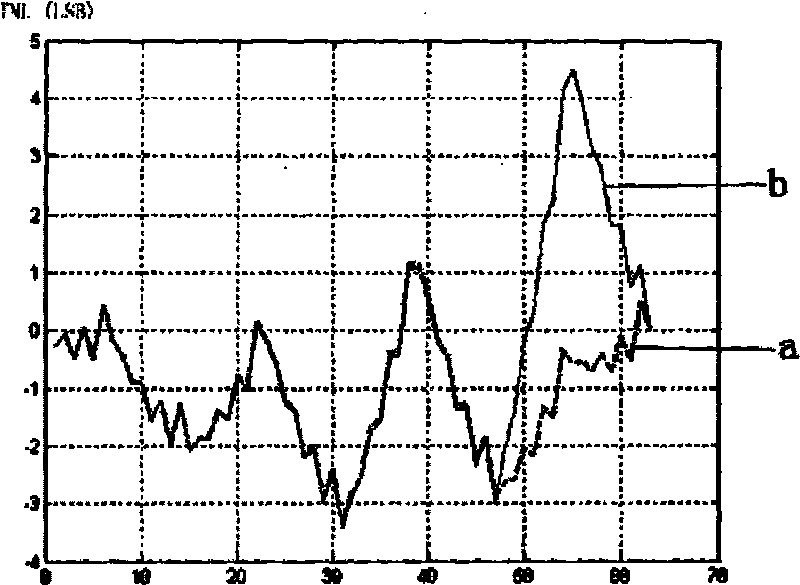

[0023] After adjusting the width of the MOS tubes in the 7th and 8th columns, the INL schema...

Embodiment 3

[0024] Embodiment 3: a high-speed and high-precision current steering digital-analog converter with 11-bit precision, its low-order current unit is composed of 5 binary current source units, and its high-order current unit controls 6 high-order, which includes 63 current source units. The 63 current source units are placed in the physical layout of the actual chip, and each unit is divided into four parts. These four parts are placed symmetrically in four quadrants. The structure diagram of the second quadrant is shown in figure 1 . Among them, the second-order error brought by the CMOS process itself is 0.036%, and the length of the MOS tubes of the 63 current source units is l′, and the width of the MOS tubes in the first, second, third, fourth, fifth, and sixth columns Both are w', the width of the MOS tube in the seventh column is 0.98w', and the width of the MOS tube in the eighth column is 1.02w'.

[0025]After adjusting the width of the MOS tubes in the 7th and 8th col...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More