Bytecode caching device and accessing method for real-time Java processor

A high-speed cache and bytecode technology, which is applied to the architecture with a single central processing unit, machine execution device, general-purpose stored program computer, etc., can solve the problems of low utilization rate and long waiting time of the processor, and achieve the reduction of CPU pause effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

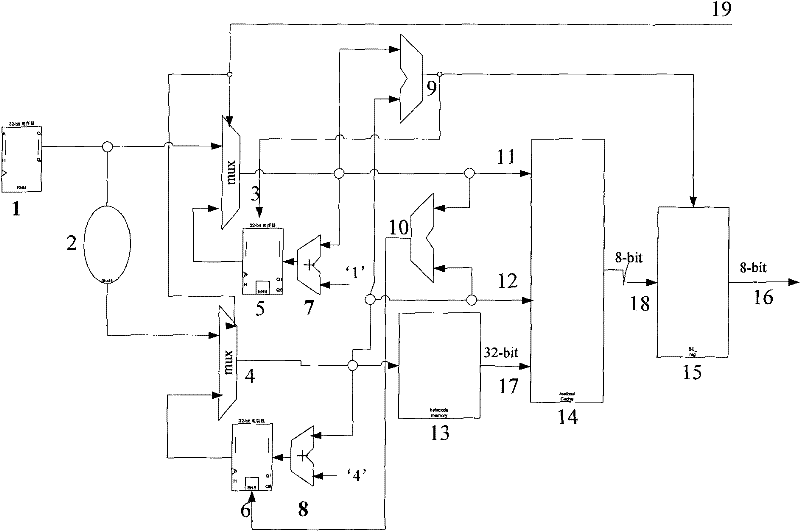

[0032] Such as figure 1 As shown, the device proposed by the present invention includes a bytecode counter 1, a cache read address multiplexer 3, a cache write address multiplexer 4, a cache read address register 5, and a cache write address register 6 , cache read address adder 7 , cache write address adder 8 , bytecode readable comparator 9 , bytecode writable comparator 10 , main memory 13 , cache memory 14 and bytecode register 15 .

[0033] Among them, the bytecode counter 1 is used to save the address of the bytecode to be executed with the byte as the addressing unit, and the byte as the addressing minimum unit, which is adjusted by the decoding segment of the CPU according to the actual length of the current bytecode . The width of the bytecode counter 1 is determined by the address width of the main memory 13 . The address of the bytecode counter 1 is sent to the cache write address multiplexer 4 after the address alignment operation 2 .

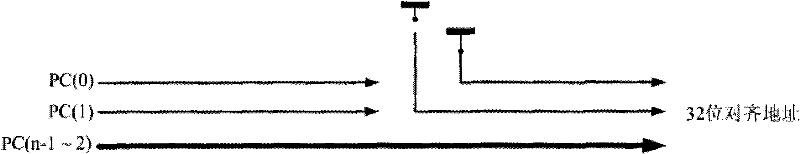

[0034] figure 2 It is a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More