Method for multiplexing IO units in stream processor

A stream processor and multiplexing processing technology, applied in the direction of machine execution device, concurrent instruction execution, etc., can solve the problems of increased design area and delay, inconvenient programming for programmers, no longer able to provide support, etc., to reduce the number of selectors , the effect of reducing the number of IO units and reducing the instruction field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

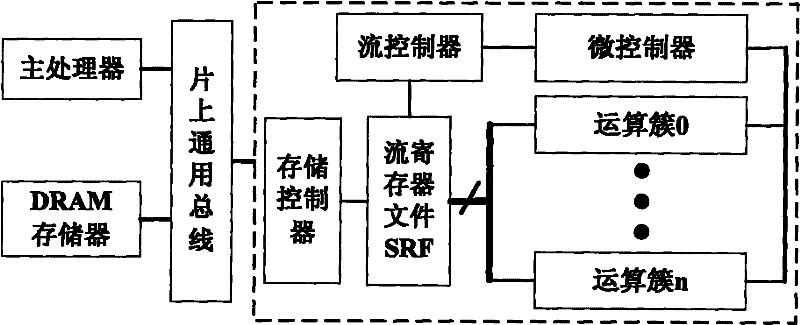

[0044] figure 1 It is the logical structure diagram of the current Imagine series stream processor. The stream processor is composed of a main processor, DRAM memory, storage controller, stream controller, microcontroller, stream register file SRF and multiple computing clusters, and all components are connected by an on-chip general bus. All calculation operations in the stream processor are completed by the calculation cluster, and the input data stream, output data stream and intermediate data related to the calculation are all stored in the stream register file SRF to ensure that the data can be recycled inside the processor without external DRAM memory is accessed. The VLIW code generated by compiling the core program is stored in the microcode memory of the microcontroller. When the core program starts, the microcontroller broadcasts the VLIW code to each operation cluster one by one, and controls each operation cluster to execute in SIMD mode.

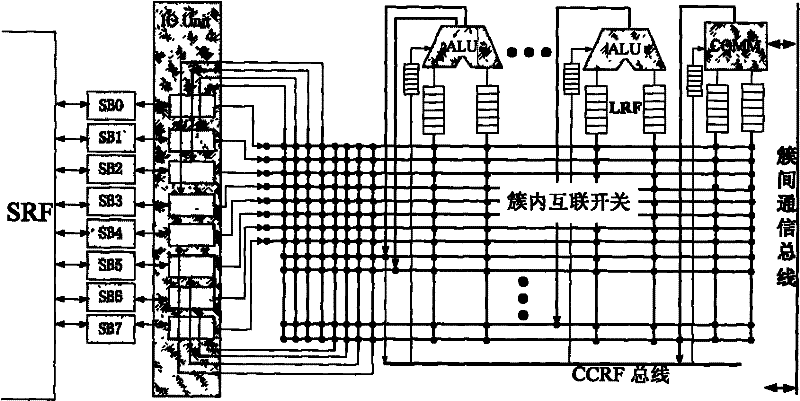

[0045] figure 2 yes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More