Encapsulating structure of semiconductor chip and manufacturing technology thereof

A technology of packaging structure and manufacturing process, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc. It can solve the problems that the welding protective coating cannot fully penetrate, and the protective layer cannot effectively cover the lead metal layer. , to achieve the effect of ensuring electrical performance, improving quality and enhancing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

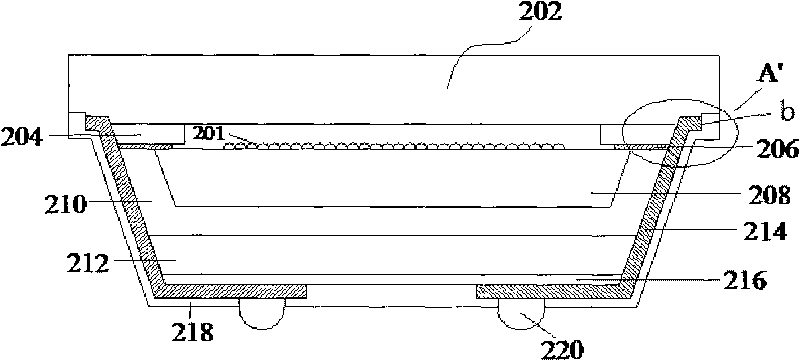

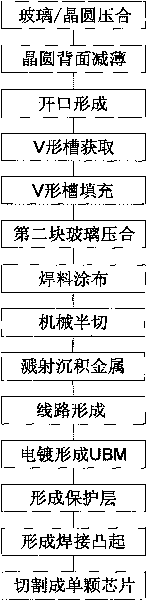

[0043] Example: first combine figure 2 As shown, the semiconductor chip packaging structure provided by the present invention is a wafer-level chip-scale packaging structure, which includes a package body, a chip 208 packaged in the package body and containing a photosensitive element 201, and a solder pad connected to the chip 208 206. The lead metal layer 214 connected to the exposed side of the solder pad 206 in a T-shaped connection and extending along the side wall of the package to the back of the package and connected to the solder bump 220, and the protection covering the outer surface of the lead metal layer 214 Layer 218. The package described in this embodiment is specifically composed of a substrate 202, a cavity wall 204 arranged on the substrate 202 in a closed-loop structure, a resin layer 210, an insulating layer 216, and a glass layer 212. The front side of the chip 208 passes through the solder pad 206. The cavity wall 204 on the substrate 202 is pressed to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More